Computer FPGA reconstruction system based on dual-core ARM SoC and operation method

A technology for reconstructing systems and operating methods, which is applied in computing, code reconstruction, error detection of redundant codes, etc. It can solve problems such as the inability to update and upgrade the FPGA software, and the computer cannot be independently controlled to achieve high maintainability. , Reduce device cost and reduce power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0038] The present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

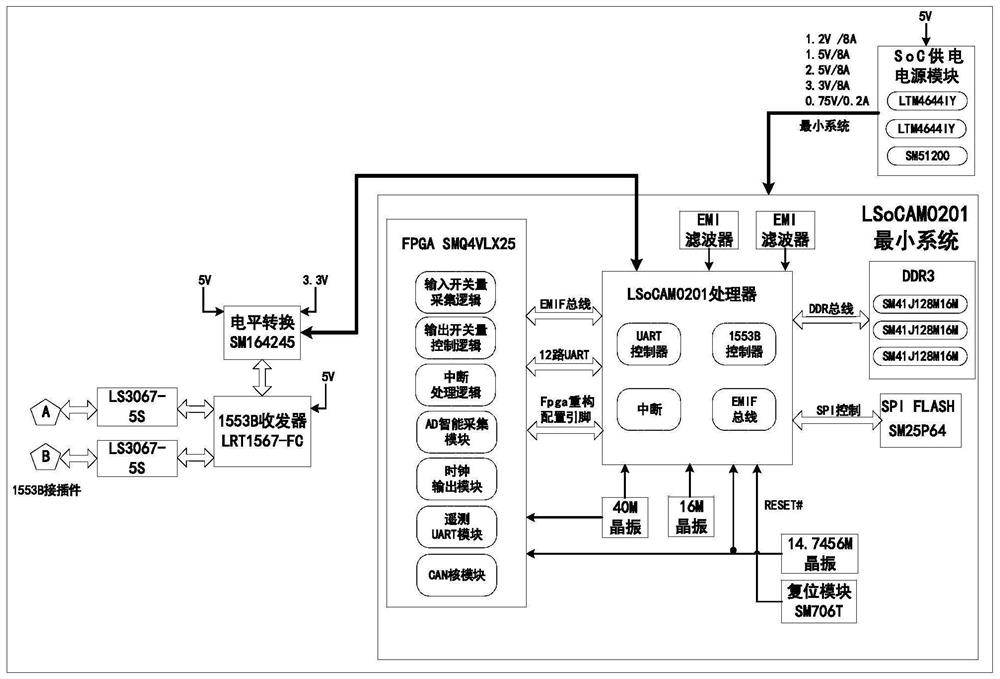

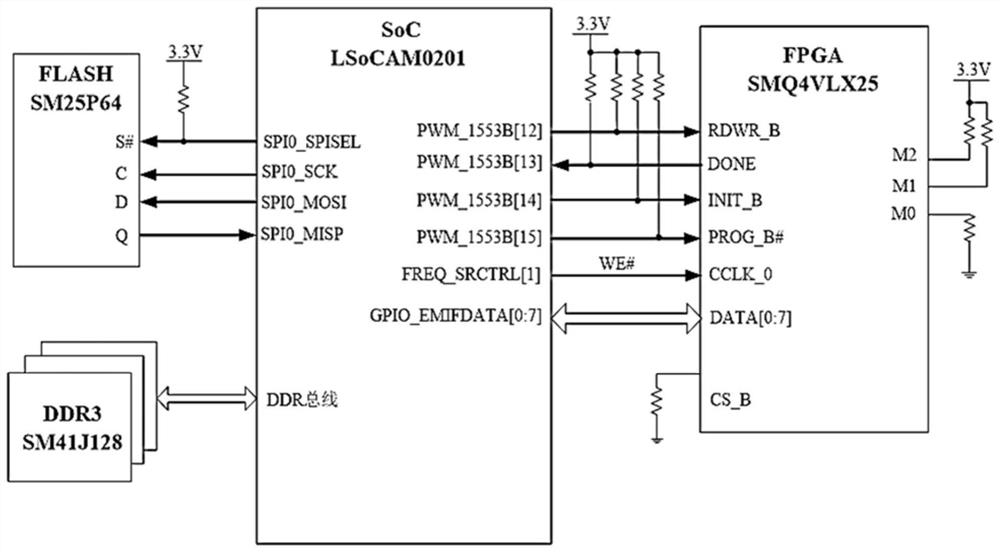

[0039] The reconstruction system of the present invention is a localized computer developed based on the LSoCAM0201 dual-core ARM SoC, wherein FPGA selects SMQ4VLX25FF668, DDR3 RAM selects 3 slices of SM41J128M16M, and the chip single-chip capacity is 128M×16bit (4Mbit), and FLASH selects 1 slice of SPI FLASH SM25P64, single chip capacity is 64Mbit, different codes of ARM SoC and FPGA can be stored in different sectors of FLASH. In addition, the computer also includes a redundant 1553B communication bus, and the communication between peripherals and the computer is realized through the 1553B communication interface.

[0040](1) LSoCAM0201 is a dual-core ARM SoC circuit for missile weapon control system and information processing system applications. The chip uses a dual-core CPU Cortex A9 as the main processor, and each core also includes a S...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More