Lead frame for chip packaging, preparation method thereof, and chip packaging structure

A lead frame and chip packaging technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve the problems of high cost, complex process, and difficulty in matching the thickness of filled electrophoretic resin, etc. Simple, low-prep effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

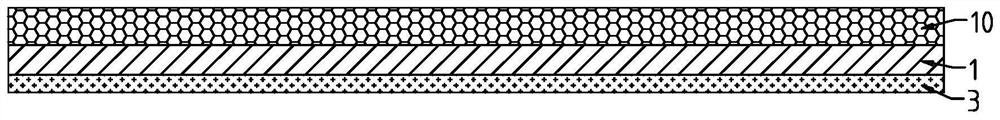

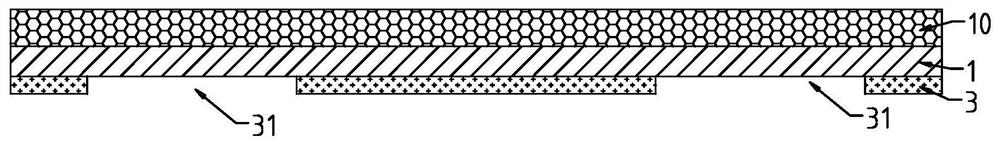

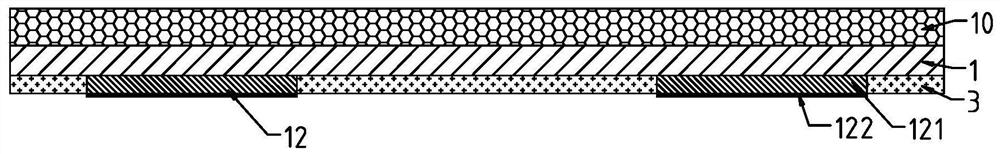

[0065] Embodiment 1 of the present invention is used for the structure of a unit circuit of a lead frame for chip packaging as follows: Figure 11 As shown, it includes a carrier sheet 2 , a solder resist ink layer 3 , two solder resist ink layers and a plurality of unit circuits arranged in a matrix. Each unit circuit includes two electrodes, and the electrodes include a top electrode 11 and a bottom electrode 12 . The top electrode 11 is arranged on the top surface of the solder resist ink layer 3 . Corresponding to each unit circuit, the solder resist ink layer 3 includes two bottom electrode holes 31 , the bottom electrode 12 is arranged in the bottom electrode holes 31 , and the top of the bottom electrode 12 is fixed on the bottom surface of the top electrode 11 . The carrier sheet 2 is peelably pasted on the solder resist ink layer 3 and the bottom surface of the bottom electrode 12 .

[0066] In this embodiment, the lateral dimension of the top electrode 11 is greater...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com