Method and device for grading and screening chips and electronic equipment

A grading and chip technology, applied in the grading field, can solve the problems of inconvenient packaging operation, no difference in the quality of wafers and wafers, inaccurate classification results, etc., to achieve high yield and reliability, and improve product quality. rate, good efficiency and the effect of the market

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

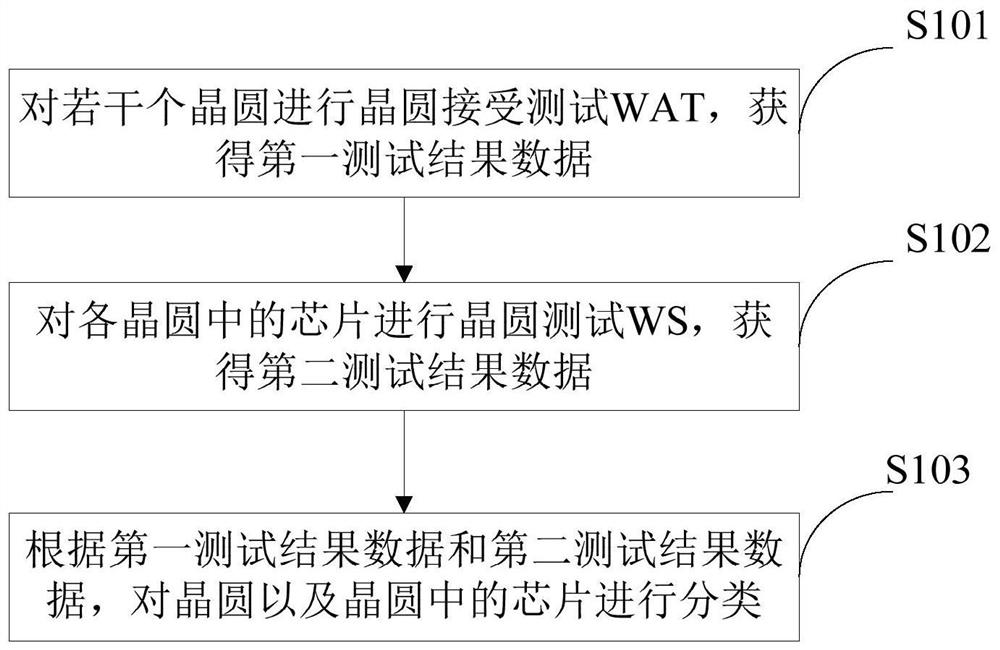

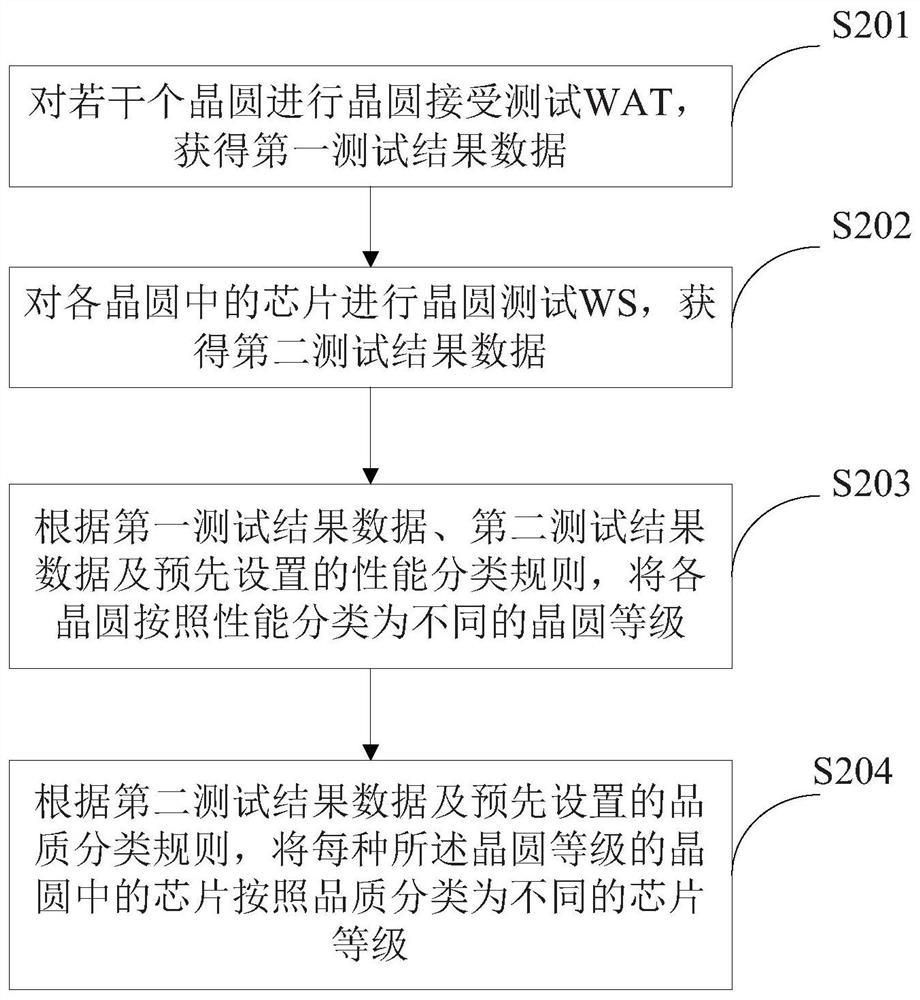

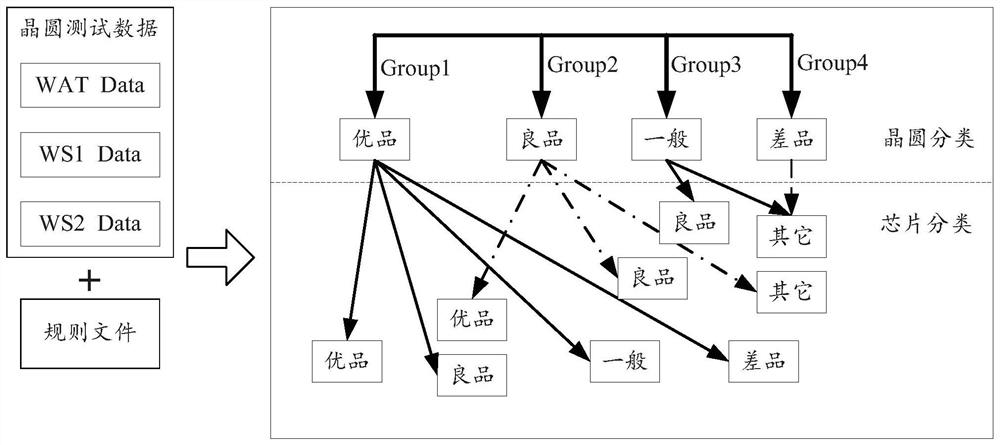

[0044] The present invention considers that there are quality differences between wafers in the same batch of wafer production, and it is necessary to classify the quality of wafers as high, medium, and low grades; at the same time, there are also chip performance differences in the wafers, which are used in wafer packaging and packaging. Before plastic packaging, the script can be used to classify the quality according to the key index parameter specifications, and generate the packaging coordinates of the three-dimensional array, mark the chip level, and use it for different grades of products after plastic packaging. Embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0045]It should be clear that the described embodiments are only some of the embodiments of the present invention, not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More