Manufacturing method of intermediate isolation oxide layer of low-capacitance split-gate trench IGBT device

A technology for isolating oxide layers and intermediate isolation, which is applied in semiconductor/solid-state device manufacturing, electrical components, semiconductor devices, etc., and can solve problems such as insufficient breakdown voltage and reduced service quality of split-gate trench IGBT devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

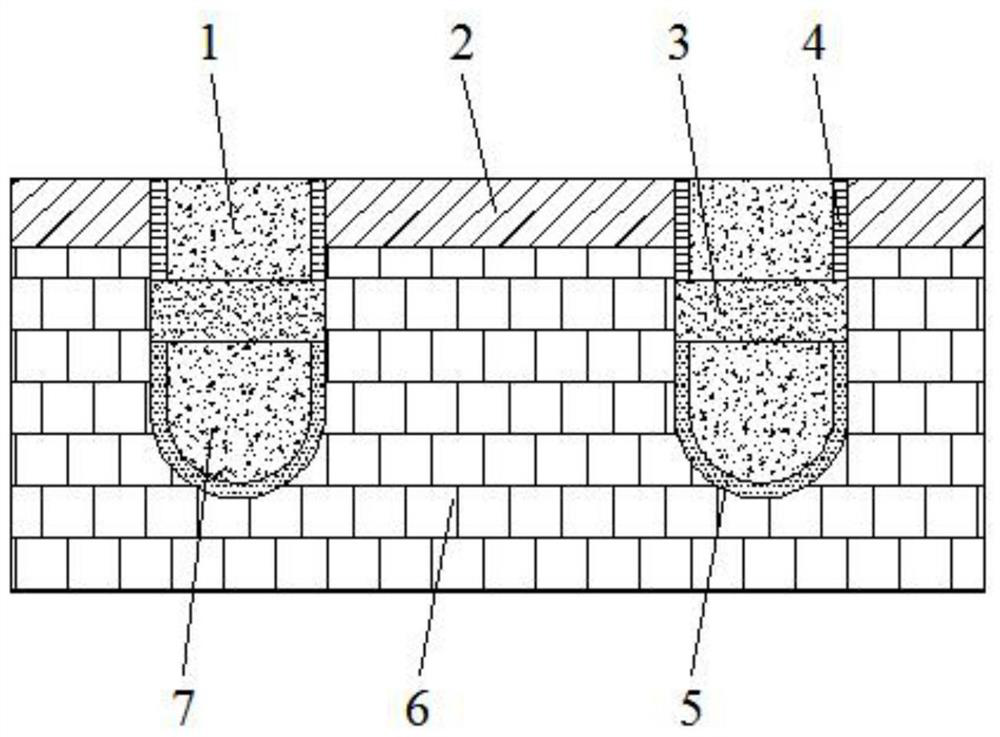

[0028] refer to Figure 1-2 , a fabrication of an isolation oxide layer in the middle of a low-capacity split-gate trench IGBT device, including an isolation oxide layer 3, a P well 2 and a silicon substrate 6, the P well 2 is arranged on the top of the silicon substrate 6, and the top of the P well 2 is opened There is a groove, the groove runs through the P well 2 and passes through the top of the silicon substrate 6, the gate oxide 4 is vertically arranged around the top of the groove, the gate polysilicon 1 is arranged inside the gate oxide 4, and the bottom thick oxide layer is arranged at the bottom of the groove. 5. The emitter polysilicon 7 is arranged inside the bottom thick oxide 5 , and the isolation oxide layer 3 is located between the gate polysilicon 1 and the emitter polysilicon 7 .

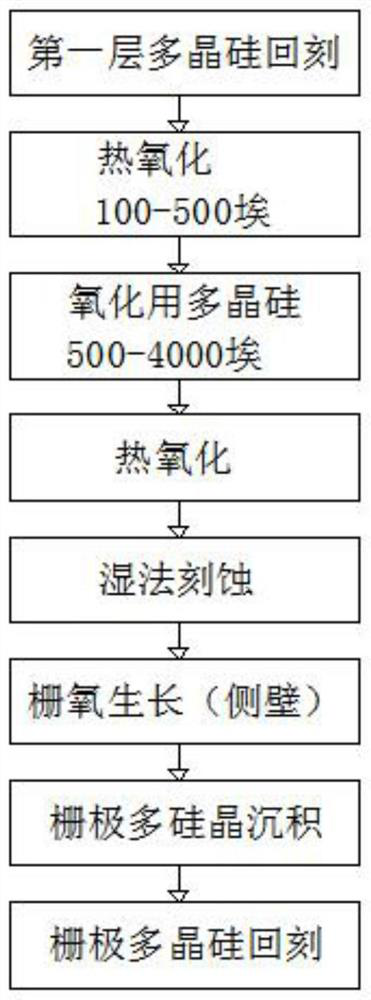

[0029] In the present invention, the isolation oxide layer 3 is obtained by combining thin oxygen plus polysilicon oxidation process.

[0030] In the present invention, the isolat...

Embodiment 2

[0040] refer to Figure 1-2 , a fabrication of an intermediate isolation oxide layer for a low-capacity divided gate trench IGBT device, comprising an isolation oxide layer 3, a P well 2 and a silicon substrate 6, the P well 2 is arranged on the top of the silicon substrate 6, and the P well 2 A groove is opened on the top, the groove runs through the P well 2 and passes through the top of the silicon substrate 6, and the gate oxide 4 is vertically arranged around the top of the groove, the gate polysilicon 1 is arranged inside the gate oxide 4, and the bottom of the groove is arranged There is a bottom thick oxide 5 , the emitter polysilicon 7 is arranged inside the bottom thick oxide 5 , and the isolation oxide layer 3 is located between the gate polysilicon 1 and the emitter polysilicon 7 .

[0041] In the present invention, the isolation oxide layer 3 is obtained by combining thin oxygen plus polysilicon oxidation process.

[0042] In the present invention, the isolation ...

Embodiment 3

[0052] refer to Figure 1-2, a fabrication of an intermediate isolation oxide layer for a low-capacity split-gate trench IGBT device, including an isolation oxide layer 3, a P well 2 and a silicon substrate 6, the P well 2 is arranged on the top of the silicon substrate 6, and the P well 2 A groove is opened on the top, the groove runs through the P well 2 and passes through the top of the silicon substrate 6, and the gate oxide 4 is vertically arranged around the top of the groove, and the gate polysilicon 1 is arranged inside the gate oxide 4, and the bottom of the groove is arranged There is a bottom thick oxide 5 , the emitter polysilicon 7 is arranged inside the bottom thick oxide 5 , and the isolation oxide layer 3 is located between the gate polysilicon 1 and the emitter polysilicon 7 .

[0053] In the present invention, the isolation oxide layer 3 is obtained by combining thin oxygen plus polysilicon oxidation process.

[0054] In the present invention, the isolation ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More