Semiconductor structure and forming method thereof

A semiconductor and structural surface technology, applied in the field of semiconductor structure and its formation, can solve the problems of transistor performance to be improved, and achieve the effect of improving carrier mobility, good electrical performance, and good breakdown resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] As mentioned in the background, existing semiconductor structures perform poorly.

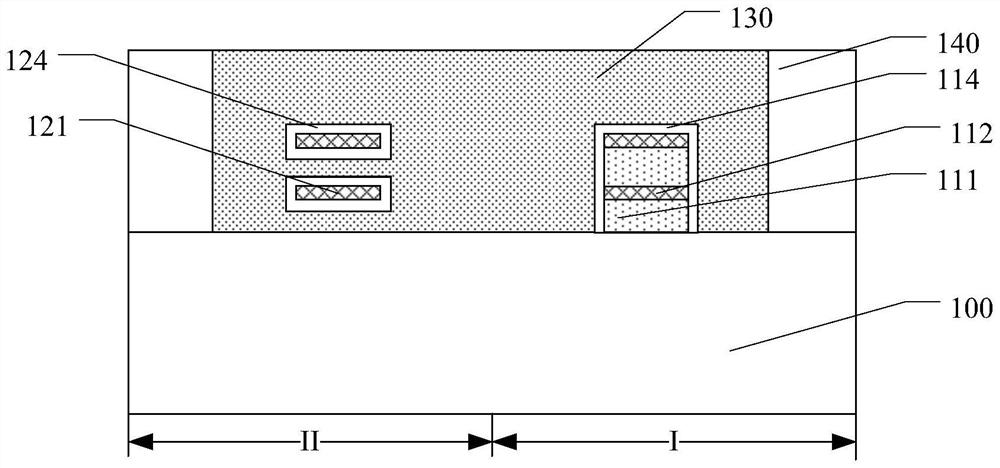

[0032] The reasons for the poor performance of the semiconductor structure will be described in detail below in conjunction with the accompanying drawings. figure 1 A schematic diagram of a semiconductor structure.

[0033] Please refer to figure 1, including: a substrate 100, the substrate 100 includes: a first region I and a second region II, the first region I has a first fin structure (not shown), the first fin structure includes Several composite fin layers (not shown) stacked in the normal direction on the surface of the substrate 100, each composite fin layer includes a first fin layer 111 and a second fin layer 112 located on the surface of the first fin layer 111 , the second region II has a second fin structure (not shown), the second fin structure includes several layers of third fin layers 121 separated from each other along the normal direction of the surface of the substr...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More