Packaging structure and forming method thereof

A packaging structure and flip-chip technology, which is applied in the manufacture of electrical components, electrical solid devices, semiconductor/solid devices, etc., can solve the problems of reduced connection area on the back of the substrate, limited circuit design of the substrate, and blockage of air holes by plastic packaging materials, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

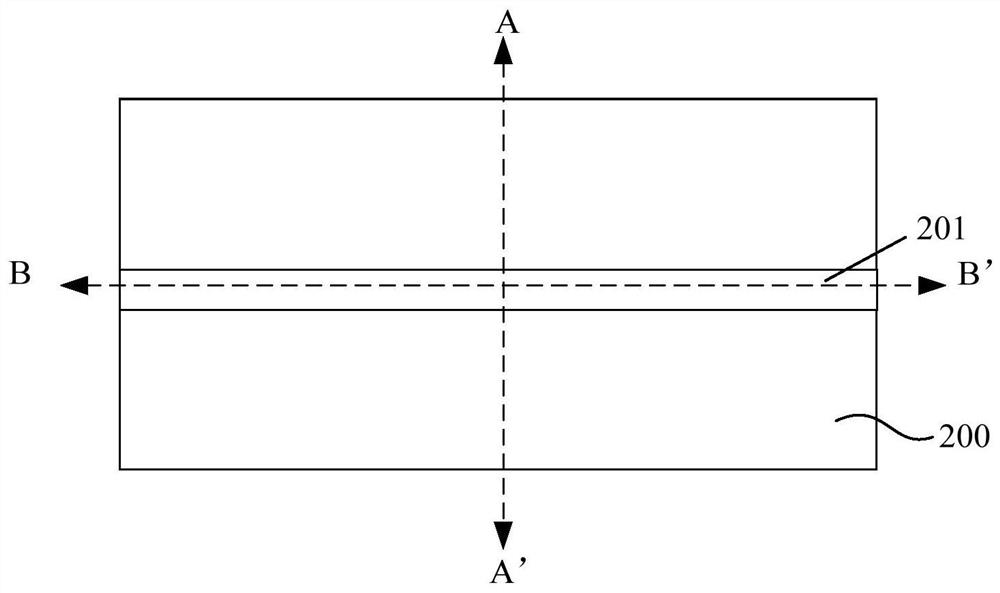

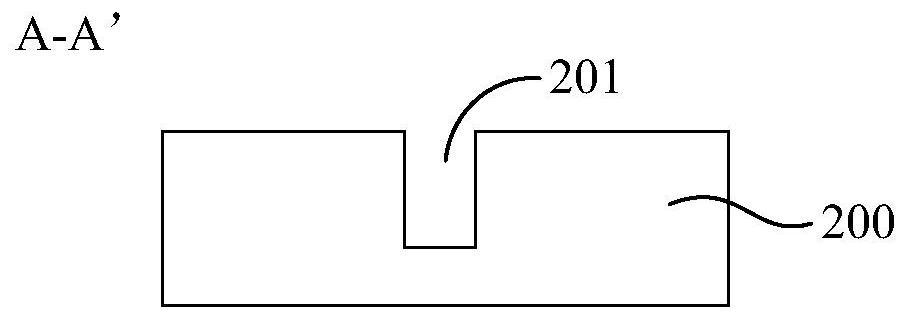

[0033] Please refer to Figure 2A to Figure 2C It is a structural schematic diagram of a substrate of a packaging structure according to a specific embodiment of the present invention, wherein Figure 2A is a schematic top view of the substrate, Figure 2B for the substrate along Figure 2A The cross-sectional schematic diagram of A-A' direction in the middle, Figure 2C for the substrate along Figure 2A The cross-sectional schematic diagram of B-B' direction in the middle.

[0034] The substrate 200, the substrate 200 has opposite first surface and second surface, the first surface is used to fix the chip, and the second surface is used to form solder balls connected with other circuit boards.

[0035] The substrate 200 is a circuit board, and the surface and / or inside of the substrate 200 are formed with electrical connection structures such as interconnection circuits and pads (not shown in the figure), which are used to form an electrical connection with the chip and ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Width | aaaaa | aaaaa |

| Depth | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More