3DIC chip and preparation method of 3DIC chip

A chip and chip body technology, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve the problems of bump stress concentration, stress concentration, unevenness, etc., to avoid the risk of virtual welding and ensure coplanarity. degree of effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

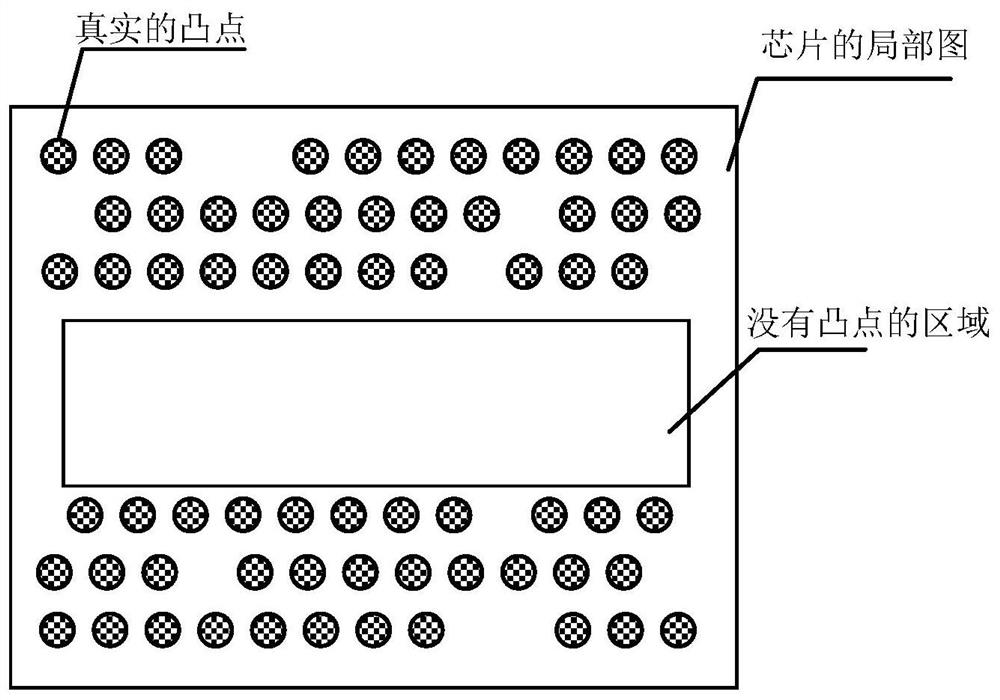

[0049] The present invention provides a 3DIC chip, comprising: a chip body, a window is opened on the first surface of the chip body; Staggered; the top metal layer is set under the first surface; the chip pad is set on the top metal layer, and the real bump is set on the chip pad. Disposing the real bumps on the chip pads can ensure the signal transmission capability of the real bumps, and the dummy bumps are disposed on the first surface to distribute stress but not transmit signals.

Embodiment 2

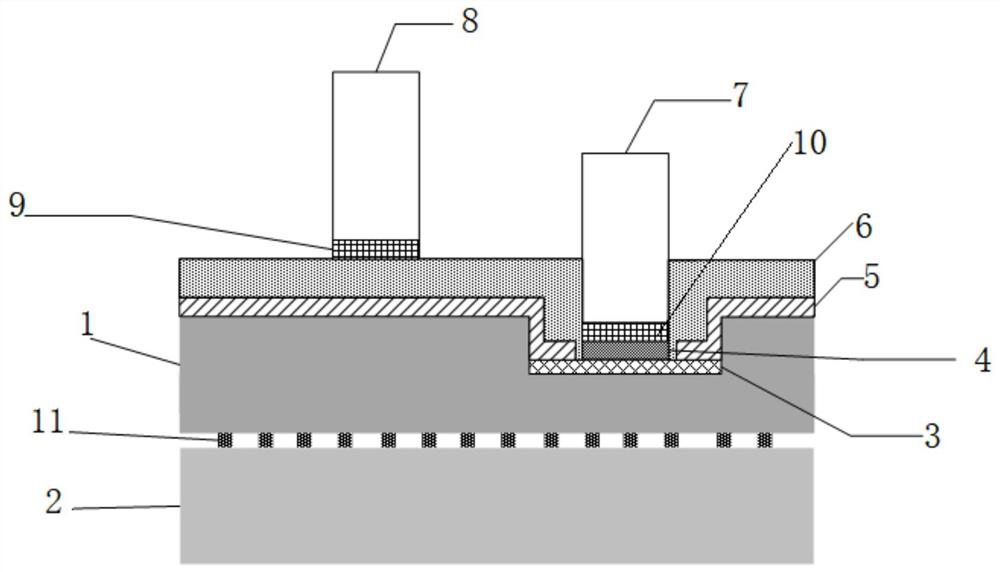

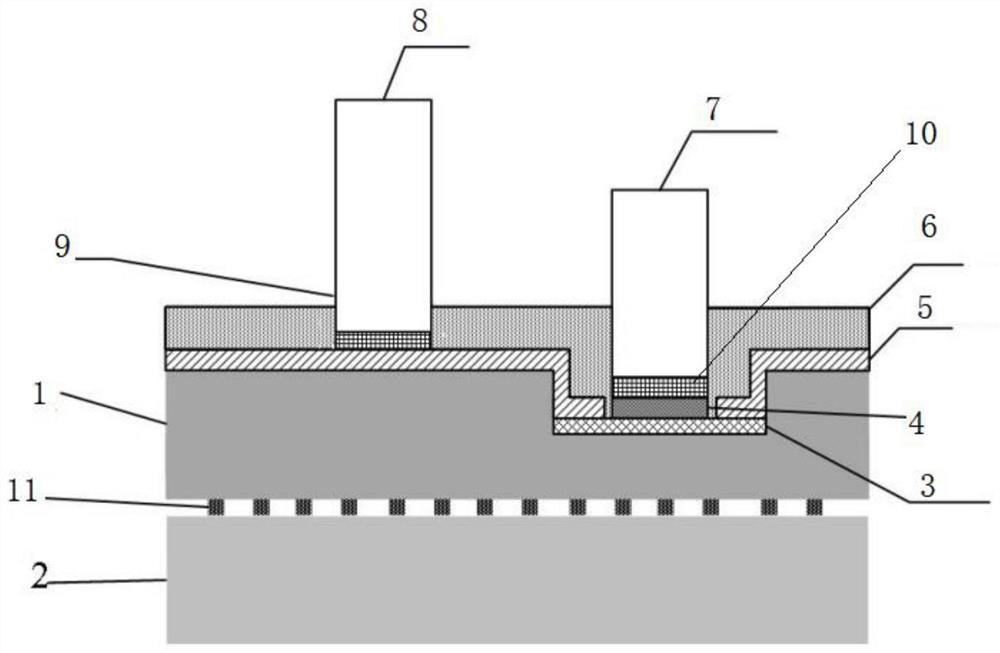

[0051] In order to reduce the height difference between the real bump and the dummy bump and prevent oxidation of the metal layer of the chip, a passivation layer is provided. On the basis of Embodiment 1, a passivation layer is also included. The passivation layer is disposed on the first surface, the sidewall of the window and covers the top metal layer without chip pads; the dummy bump is disposed on the passivation layer corresponding to the first surface. The passivation layer completely covers the bare top metal layer and the first surface to prevent oxidation of the metal layer. The virtual bumps are set on the passivation layer, the real bumps are set on the chip pads, the virtual bumps and the real bumps grow at the same time, and the height difference between the virtual bumps and the real bumps is only the upper surface of the chip pad and the The distance between the top surfaces of the passivation layer.

Embodiment 3

[0053]In order to reduce the stress of the passivation layer, a transition layer is covered on the passivation layer and fills the opening. The transition layer is generally a polymer. The dummy bumps can be disposed on the passivation layer as described in Embodiment 2, and grow through the transition layer. The real bumps are placed on the die pads, also through the transition layer. Dummy bumps can also be placed directly on the transition layer. However, although the direct setting of virtual bumps on the transition layer can also solve the problem of stress concentration, the welding accuracy must be well controlled. If the height difference between the virtual bumps and the real bumps exceeds the tolerance requirements for chip flipping, cause solder joint problems.

[0054] The specific structure is as figure 2 As shown, a 3DIC chip includes a chip body, a top metal layer, a metal layer, a passivation layer, and a polymer layer (ie, a transition layer). The chip bo...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More