Heterogeneous computing hardware energy consumption and performance optimization method and system and storage medium

A hardware and heterogeneous technology, applied in computing, computing models, energy-saving computing, etc., can solve problems affecting performance efficiency and performance degradation, and achieve optimal power consumption and performance, and reduce power consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

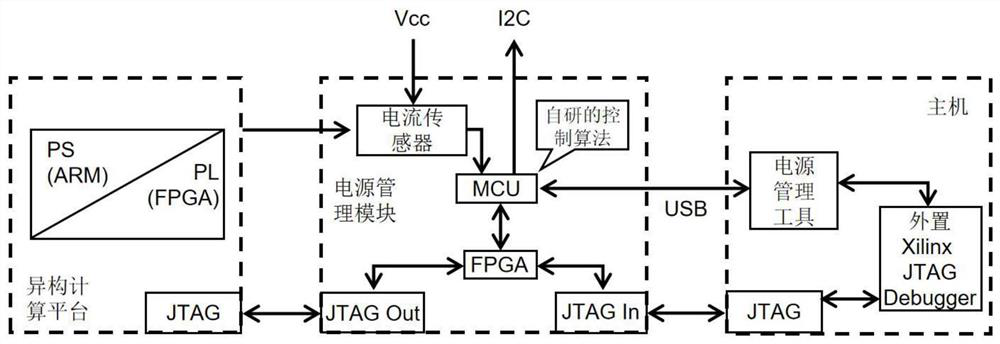

[0015] This embodiment provides a method for optimizing energy consumption and performance of heterogeneous computing hardware through reinforcement learning. Such as figure 1 As shown, the hardware frame structure applied by this method mainly includes:

[0016] PS: Processing System (Processing System), part of the SOC based on the ARM core.

[0017] PL: Programmable logic (Progarmmable Logic), FPGA part.

[0018] MCU: Microcontroller Unit Microcontroller Unit.

[0019] PS and PL together form a heterogeneous computing platform, that is, this heterogeneous platform includes ARM and FPGA computing hardware.

[0020] figure 1 The left part: is the target heterogeneous computing platform, that is, the hardware that needs to be optimized for power consumption. In the embodiment of the present invention, this is a hardware including ARM (PS side) and FPGA (PL side).

[0021] figure 1 Intermediate components: power management module, which is a hardware module connected to ...

Embodiment 2

[0073] This embodiment provides an embedded system, including a memory, a processor, and a program stored in the memory and operable on the processor. When the program is executed by the processor, the program described in Embodiment 1 is implemented. Steps of a method for realizing optimization of energy consumption and performance of heterogeneous computing hardware through reinforcement learning.

Embodiment 3

[0075] This embodiment provides a storage medium, the storage medium stores at least one program, and the at least one program can be executed by at least one processor, so as to realize the energy consumption of heterogeneous computing hardware through reinforcement learning described in Embodiment 1. And the steps of the method of performance optimization.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More