FPGA-based ate test vector compilation acceleration method and ate system

A test vector and basic waveform technology, applied in code compilation, program code conversion, instruments, etc., can solve the problems of long compilation time, affecting compilation time, and compiled software crash, etc., to improve compilation speed, improve compilation efficiency, shorten the The effect of commissioning time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

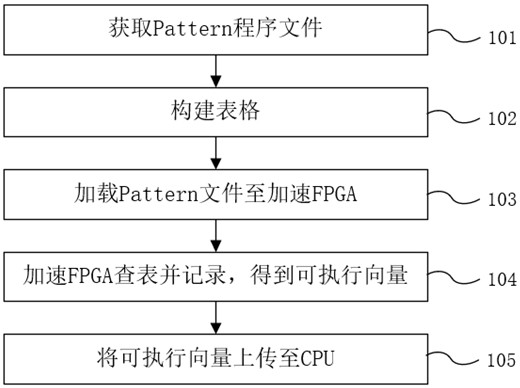

[0068] Embodiment 1 of the present invention discloses an FPGA-based ATE test vector compilation acceleration method. The parallel compilation of test vectors is realized through an external FPGA, which greatly improves the compilation efficiency of test vectors. figure 2 As shown, the specific scheme is as follows:

[0069] A method for accelerating the compilation of FPGA-based ATE test vectors is applied in ATE equipment, and the method comprises the following steps:

[0070] 101. The user performs programming based on preset testing machine instructions and predefined basic waveforms, and obtains the Pattern program file in ASCII format;

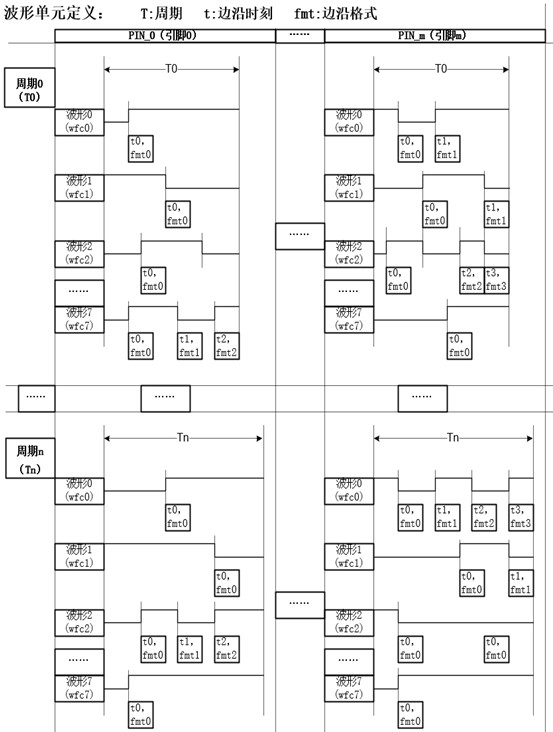

[0071] 102. Construct the waveform periodic table, edge time table, edge format table and microinstruction table based on the Pattern program file;

[0072] 103. Load the Pattern program file from the CPU of the main control board to the preset accelerated FPGA;

[0073] 104. Accelerate the FPGA to compile the Pattern program file, an...

Embodiment 2

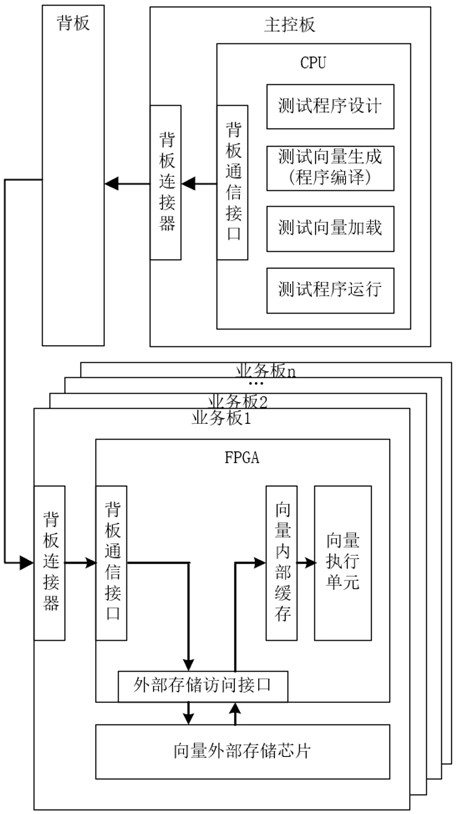

[0096] This embodiment proposes an ATE system, and the ATE system is provided with a compilation acceleration device, which can execute an FPGA-based ATE test vector compilation acceleration method proposed in Embodiment 1. The hardware structure of the ATE system is shown in the attached manual Figure 14 As shown, the specific scheme is as follows:

[0097] An ATE system, comprising a compilation acceleration device 4, a main control board 1, a backplane 2 and at least one service board 3, the backplane 2 is respectively connected to the main control board 1 and the service board 3; the main control board 1 includes a CPU11 and a PCIE interface 5 ; The compilation acceleration device 4 is connected to the main control board 1 through the PCIE interface 5 and establishes a data connection with the CPU 11 . The structure of the ATE system is shown in the attached manual Figure 14 shown.

[0098] An acceleration FPGA is arranged on the compilation acceleration device 4, and...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More