Three-dimensional quantum chip and preparation method thereof

A quantum and three-dimensional technology, applied in the field of multi-qubit chips, can solve the problems of difficult wiring, difficult to achieve wiring, and harsh requirements for pins, and achieve the effect of improving energy relaxation time, easy large-scale expansion, and eliminating preparation problems.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

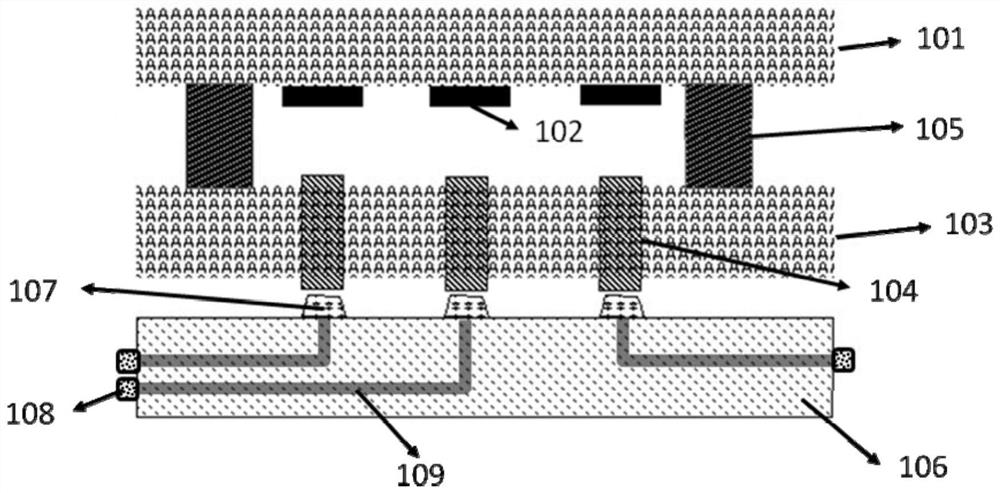

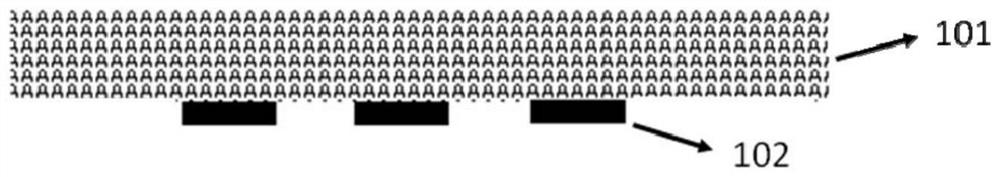

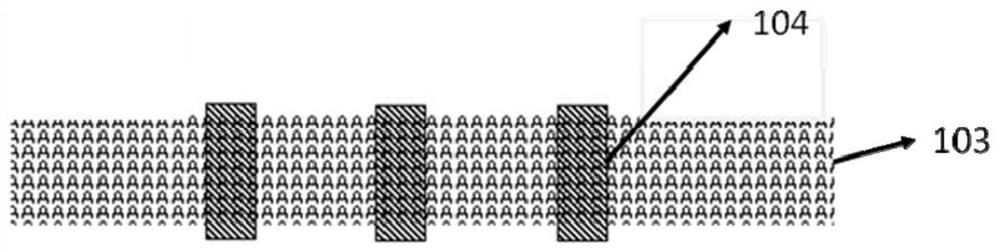

[0041] figure 1 It is a schematic cross-sectional view of a three-dimensional quantum chip prepared in an embodiment of the present invention. Such as figure 1 As shown, the three-dimensional quantum chip includes a qubit layer, an auxiliary graphics layer and a wiring layer. Wherein, the qubit layer includes a substrate 101 and qubits 102 prepared on the substrate 101 . The auxiliary pattern layer includes a substrate 103, various auxiliary patterns prepared on the substrate 103, and through holes 104 penetrating the substrate 103 and deposited with metal. The wiring layer can be a PCB board 106 , inside the PCB board 106 there are a plurality of connection wires 109 , one end of which is connected to the connection terminal 107 , and the other end is connected to the joint 108 . Preferably, the connecting terminals 107 are located on the surface of the PCB 106 facing the side of the auxiliary graphics layer. The connector 108 may be a sma or smp connector for interfacing...

Embodiment 2

[0063] Figure 7 It is a schematic cross-sectional view of a three-dimensional quantum chip prepared in another embodiment of the present invention. Such as Figure 7 As shown, the three-dimensional quantum chip includes a qubit layer, an auxiliary graphics layer and a wiring layer. Wherein, the qubit layer includes a substrate 101 and qubits 102 prepared on the substrate 101 . The auxiliary pattern layer includes a substrate 103, various auxiliary patterns prepared on the substrate 103, and through holes 104 penetrating the substrate 103 and deposited with metal. The wiring layer can be a PCB board, and the PCB board 106 has a plurality of connection wires 109 inside, one end of which is connected to the connection terminal 110 , and the other end is connected to the connector 108 . Preferably, the connecting terminal 110 is located on the surface of the side of the PCB 106 facing away from the auxiliary graphics layer. The connector 108 may be a sma or smp connector for ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com