Three-dimensional integrated chip

A three-dimensional integration and chip technology, applied in the fields of instruments, electrical digital data processing, electrical components, etc., can solve the problems of limited storage access bandwidth, insufficiency of storage capacity, etc., to solve the problem of storage walls, high bandwidth, and low power consumption. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

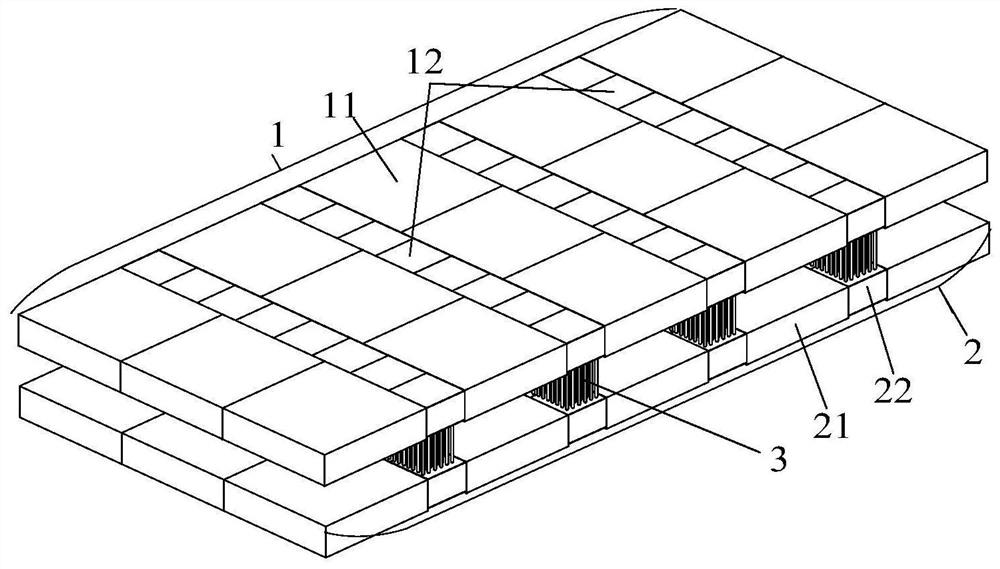

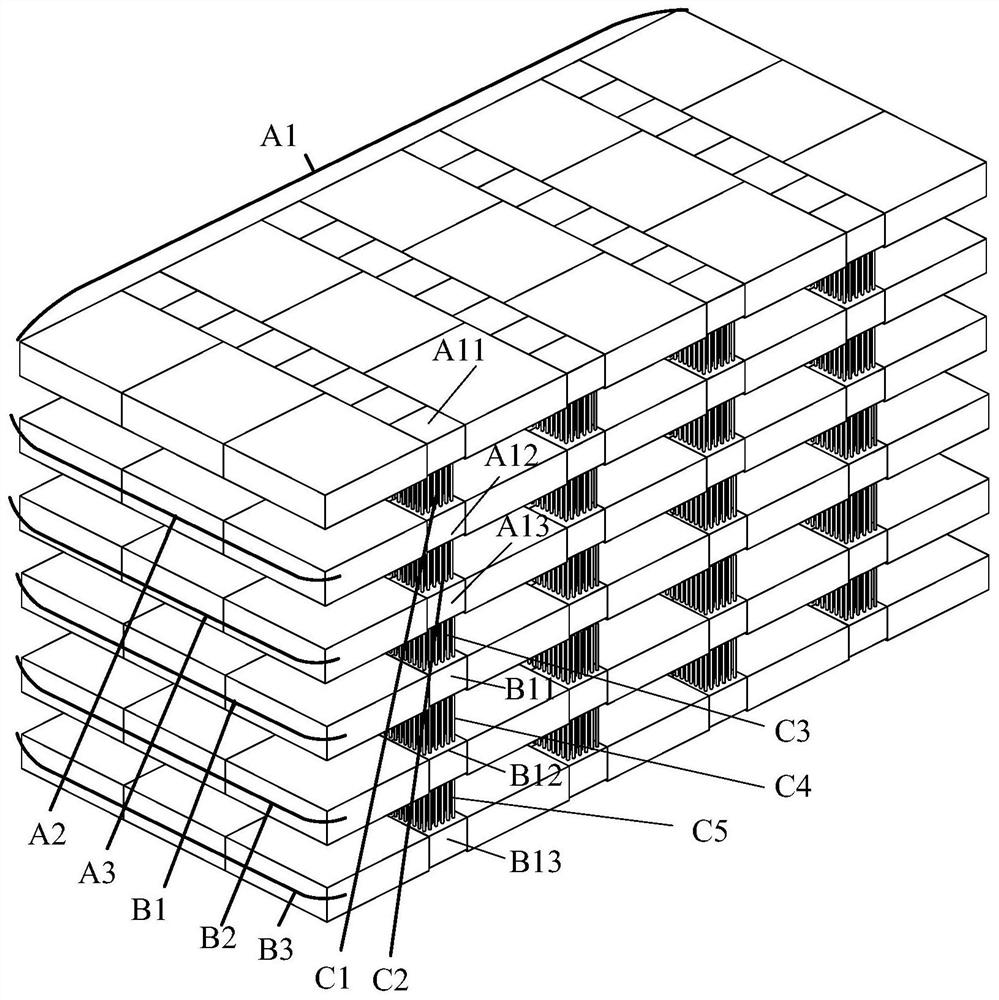

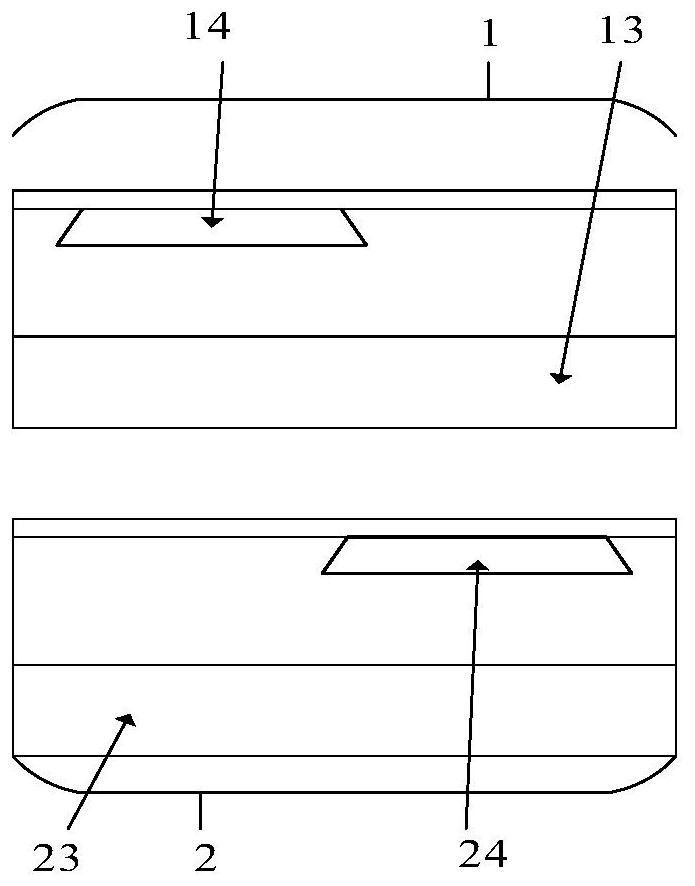

[0036] In this application, the above-mentioned components may be at least one of a die or chip and a wafer, but it is not limited thereto, and it may also be any replacement conceivable by those skilled in the art. .

[0037] Wherein, a wafer refers to a silicon wafer used for manufacturing a silicon semiconductor circuit, and a chip or a die refers to a silicon wafer obtained by dividing the above-mentioned wafer on which a semiconductor circuit is manufactured. In the specific embodiments of the present application, crystal grains are taken as an example for introduction. For example: the programmable array component is a programmable array die.

[0038]With the large-scale growth of data processing requirements, the reconfigurable architecture based on traditional FPGA / eFPGA faces the challenge of storage access. The storage access capacity and bandwidth of the reconfigurable unit are greatly increased, and the storage capacity of the static storage array in the FPGA / eFP...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com