Patents

Literature

34results about How to "Shorten the interconnection distance" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

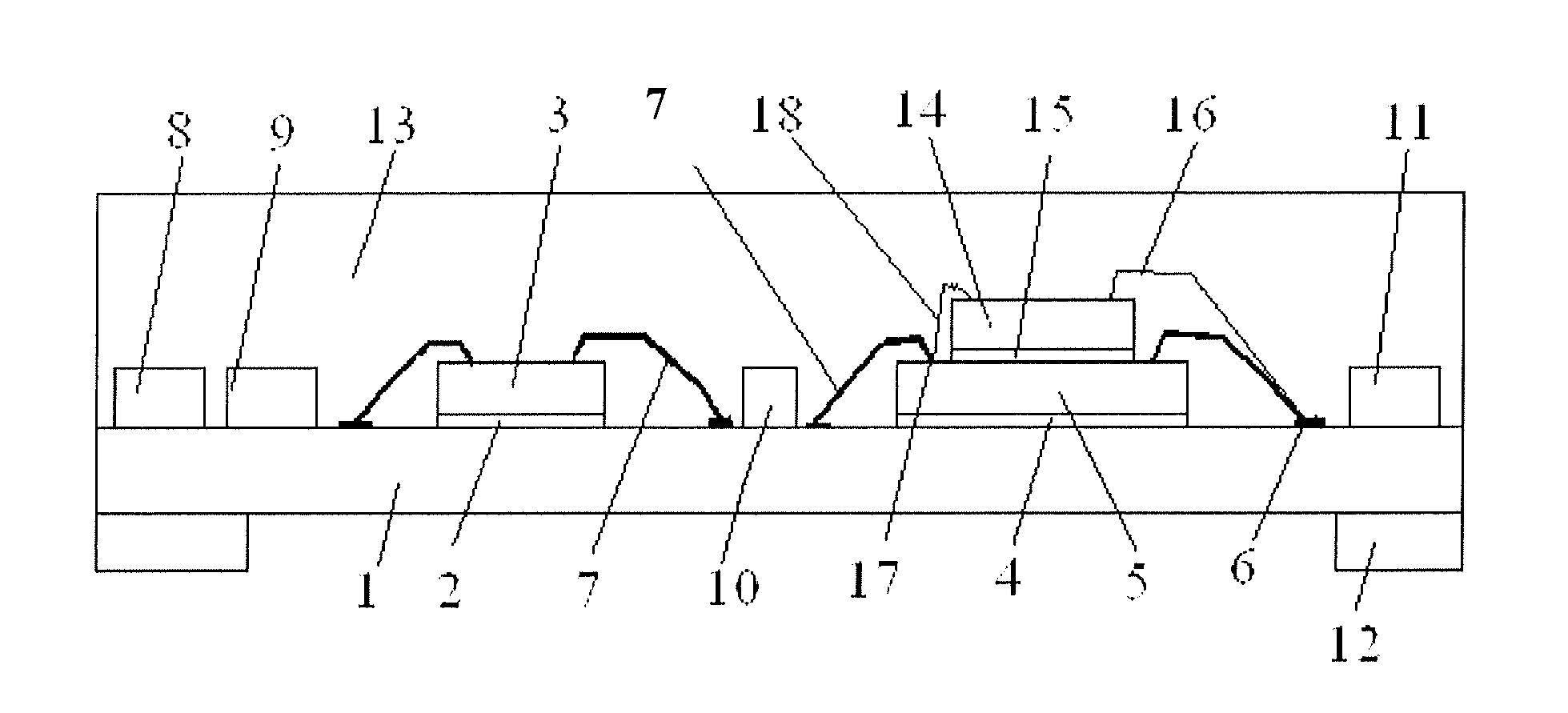

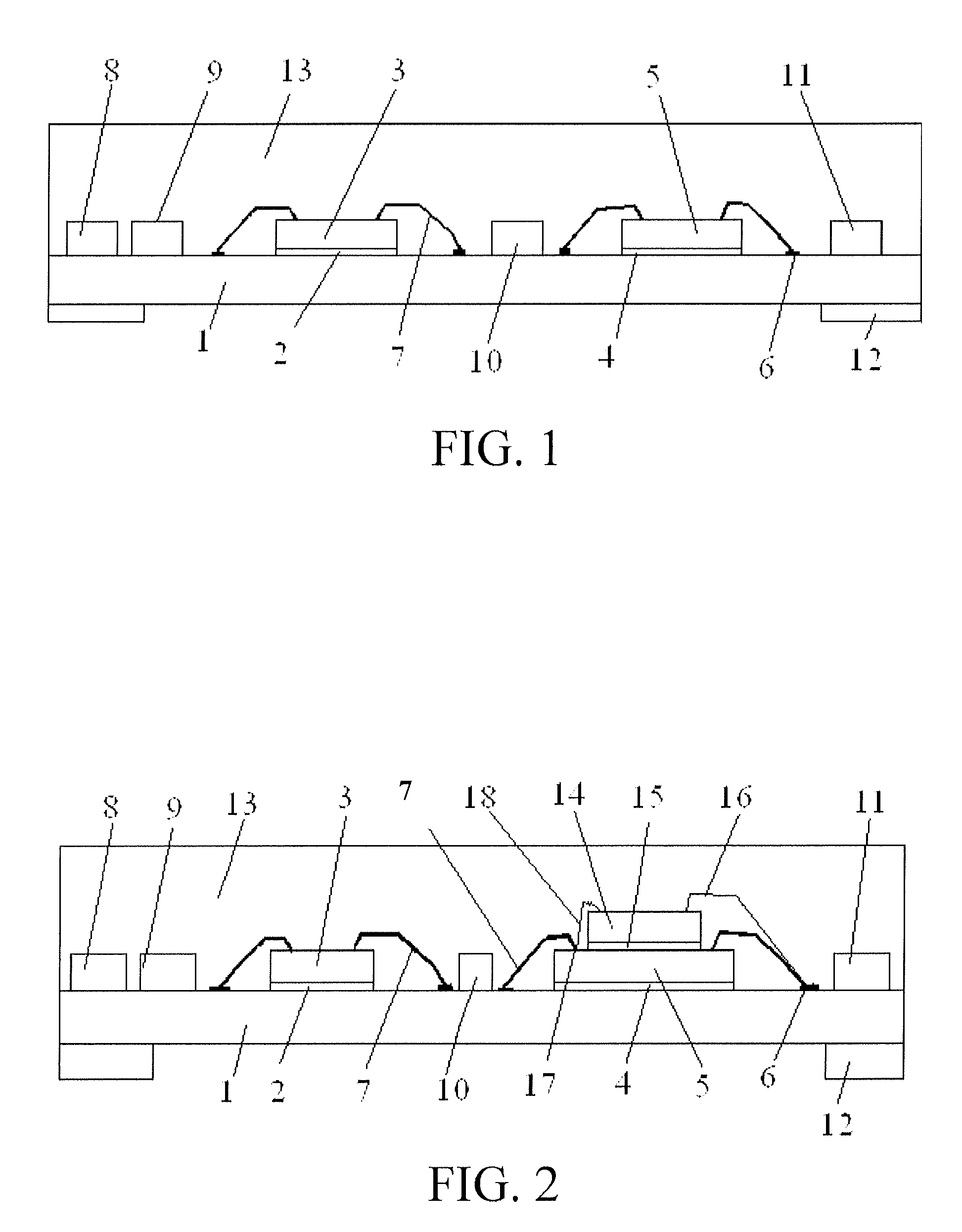

Sip system-integration IC chip package and manufacturing method thereof

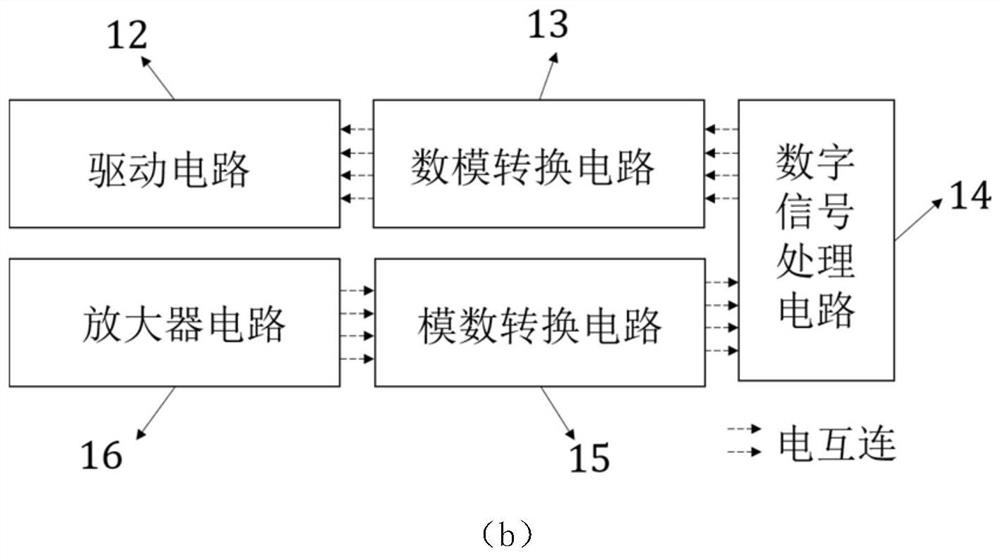

ActiveUS20130214386A1Shorten the interconnection distanceReduces signal delay timeSemiconductor/solid-state device detailsSolid-state devicesIntermediate stageIntegrated circuit

A system-in-package (SiP) system-integration integrated circuit (IC) chip package and a manufacturing method thereof are provided. The package includes a substrate, a passive device and two IC chips are provided on the substrate, an adhesive film is disposed between each of the two IC chips and the substrate, the IC chips are connected to first pads on the substrate through bonding wires, and the substrate is covered by a mold cap. A third IC chip may be further disposed on one of the IC chips, and the third IC chip is connected to the first pad and the IC chip under the third IC chip respectively through a bonding wire. A substrate adopting a surface mount technology (SMT) PAD window-opening manner is used, chip mounting is performed on the substrate, and the substrate undergoes reflow soldering, cleaning, die bonding, plasma cleaning, bonding, marking, cutting, and packing, so that the SiP system-integration IC chip package is manufactured. The package of the present invention integrates devices of different types, has a complete system function, and can be used as a middle stage of further development of system on chip (SoC).

Owner:TIANSHUI HUATIAN TECH

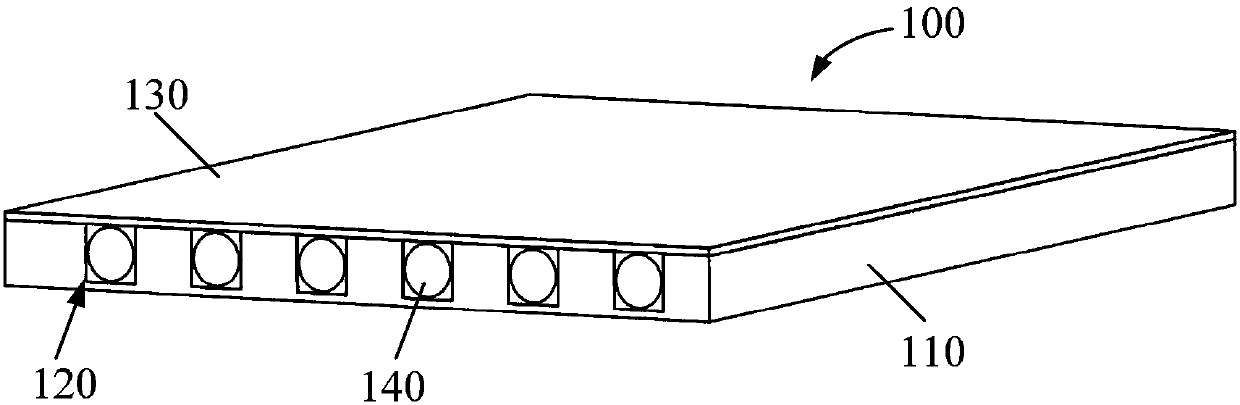

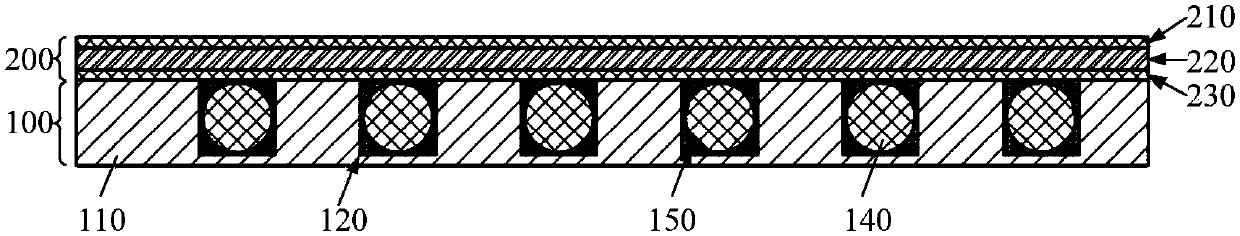

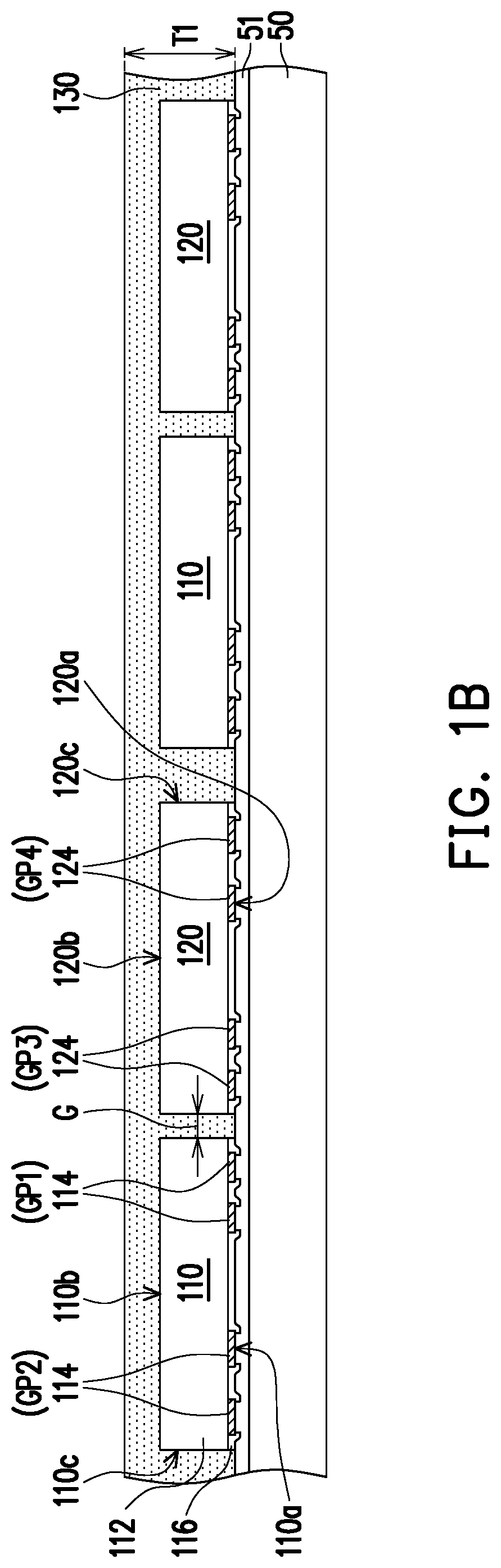

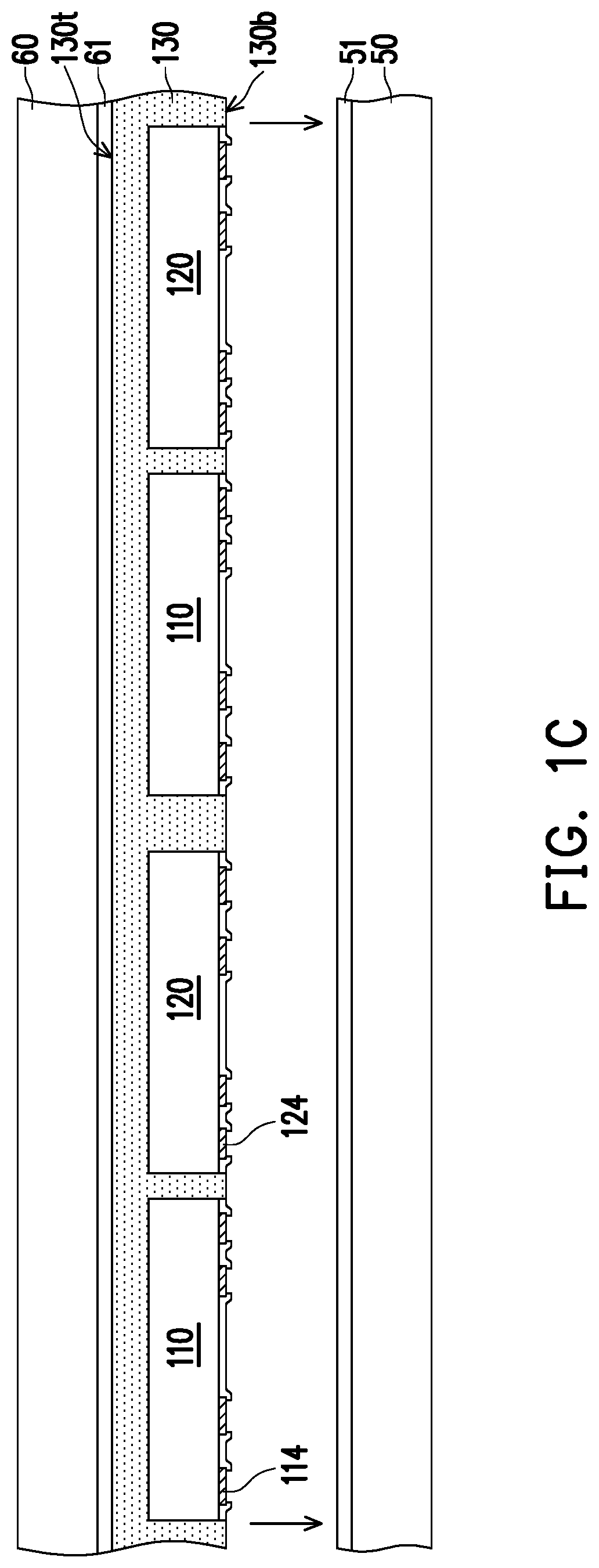

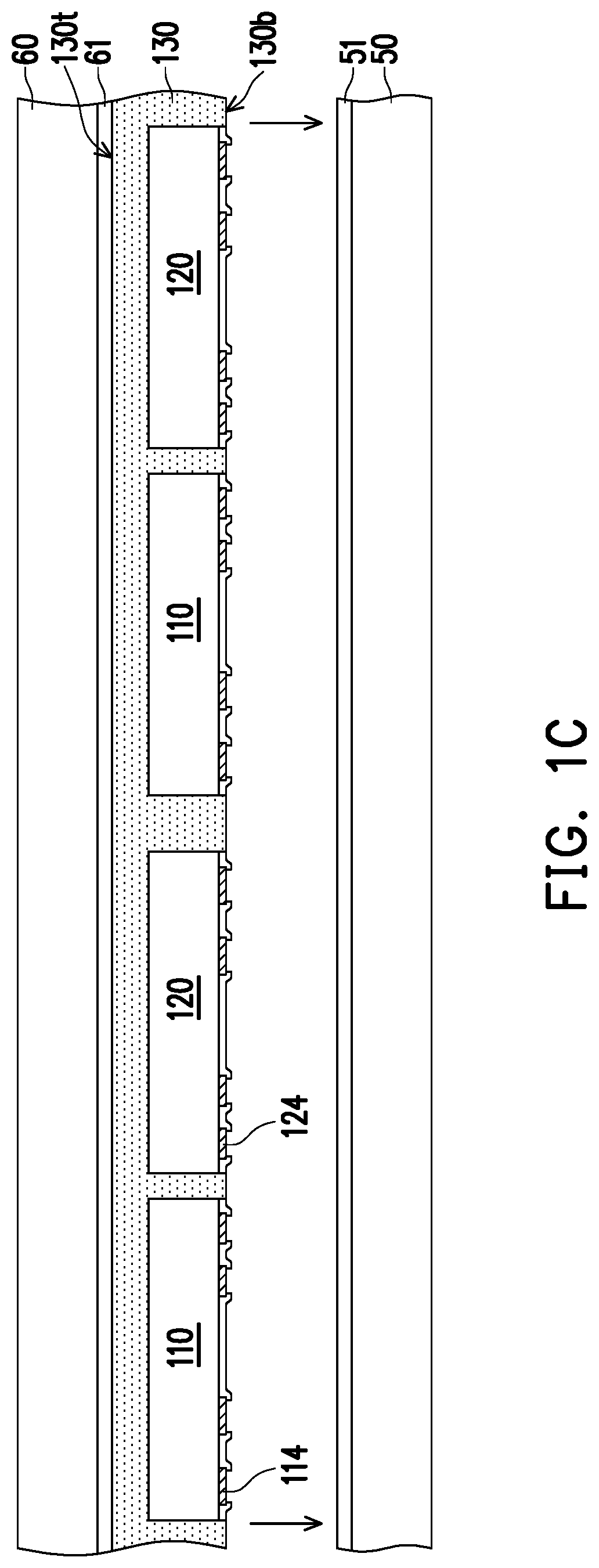

Photoelectric flexible interconnection substrate and manufacturing technology thereof

InactiveCN108024446AReduce manufacturing costAvoid deformationPrinted circuit assemblingCircuit optical detailsManufacturing technologyFlexible circuits

The invention discloses a photoelectric flexible interconnection substrate and a manufacturing technology thereof. The photoelectric flexible interconnection substrate comprises a flexible circuit board and a flexible optical circuit board, wherein a bonding layer is arranged between the flexible circuit board and the flexible optical circuit board; the flexible optical circuit board comprises a flexible interconnection substrate and a semi-cured colloid layer arranged on the upper surface of the flexible interconnection substrate; a positioning groove is formed in the flexible interconnectionsubstrate; a high temperature-resistant bare optical fiber is buried into the positioning groove; and the flexible circuit board comprises a copper circuit layer and a protection layer arranged on the copper circuit layer. The photoelectric flexible interconnection substrate is compatible with the manufacturing technology of a traditional printed circuit board, so that the optical fiber is takenas one layer in the flexible circuit board, an optical signal can be transmitted and lamination process and equipment do not need to be developed for the photoelectric flexible interconnection substrate; deformation, damage and high-temperature degradation of the optical fiber due to high temperature and high pressure in the lamination process can be avoided; and the bending radius of the interconnection substrate can be reduced, the interconnection distance between the boards is reduced and high-density assembly of an electronic communication system is improved.

Owner:NO 30 INST OF CHINA ELECTRONIC TECH GRP CORP

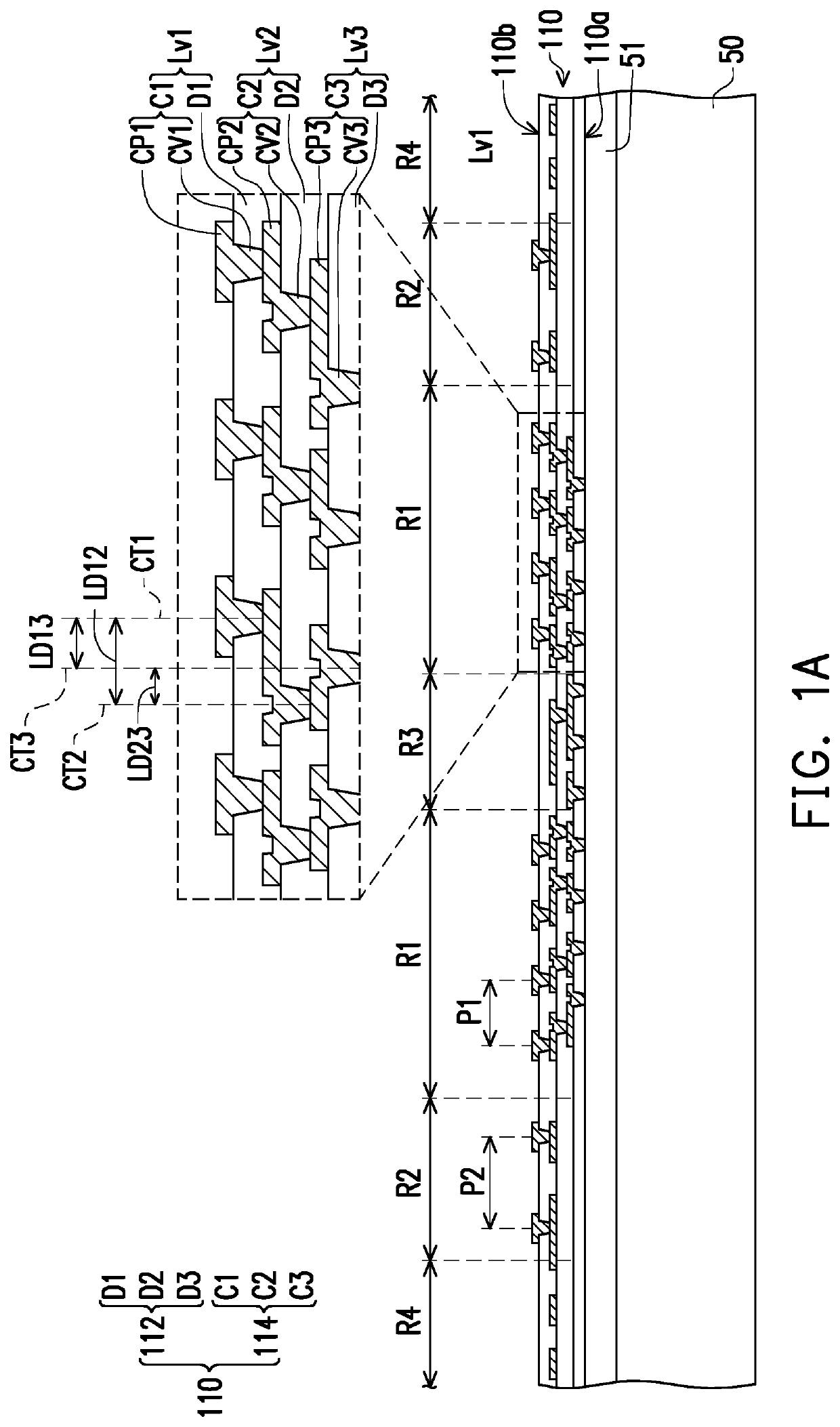

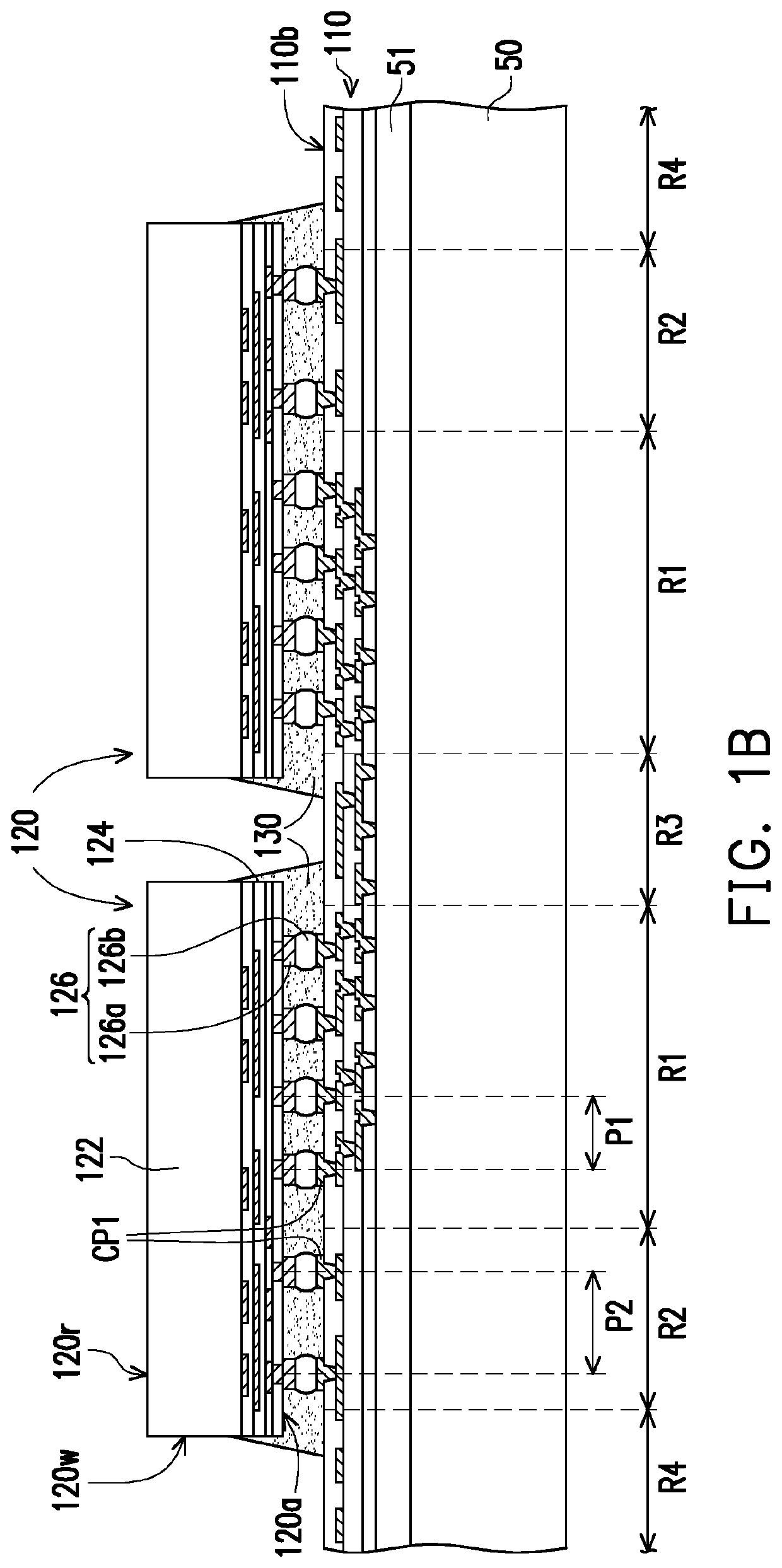

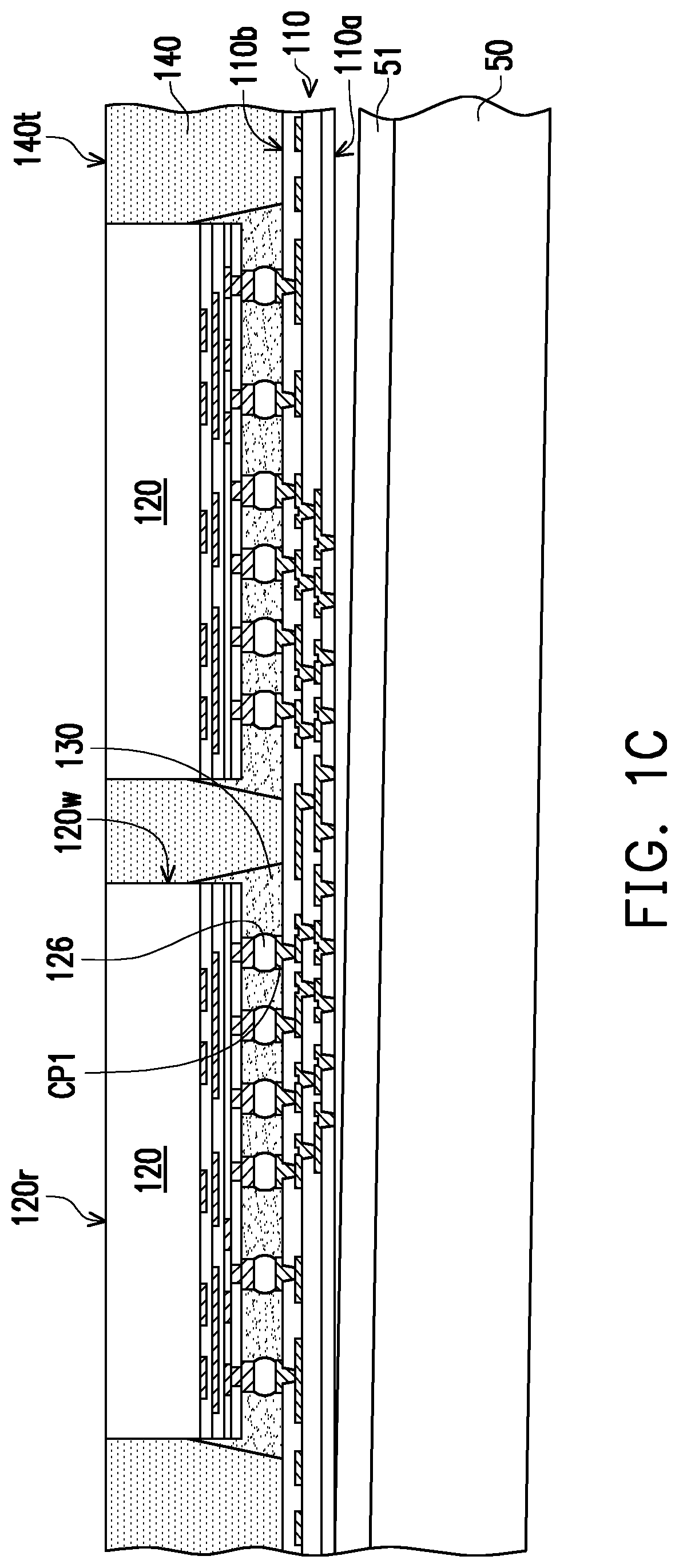

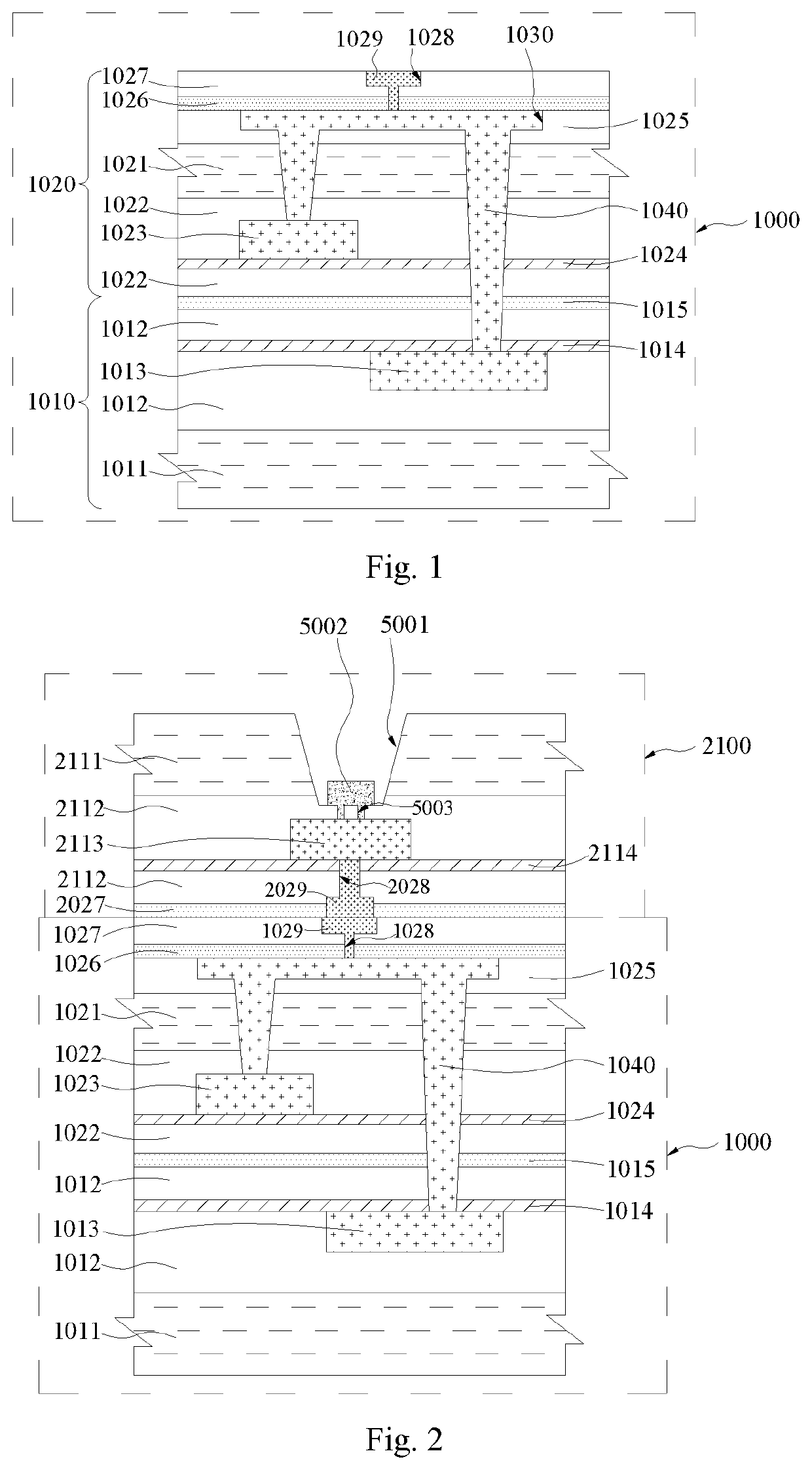

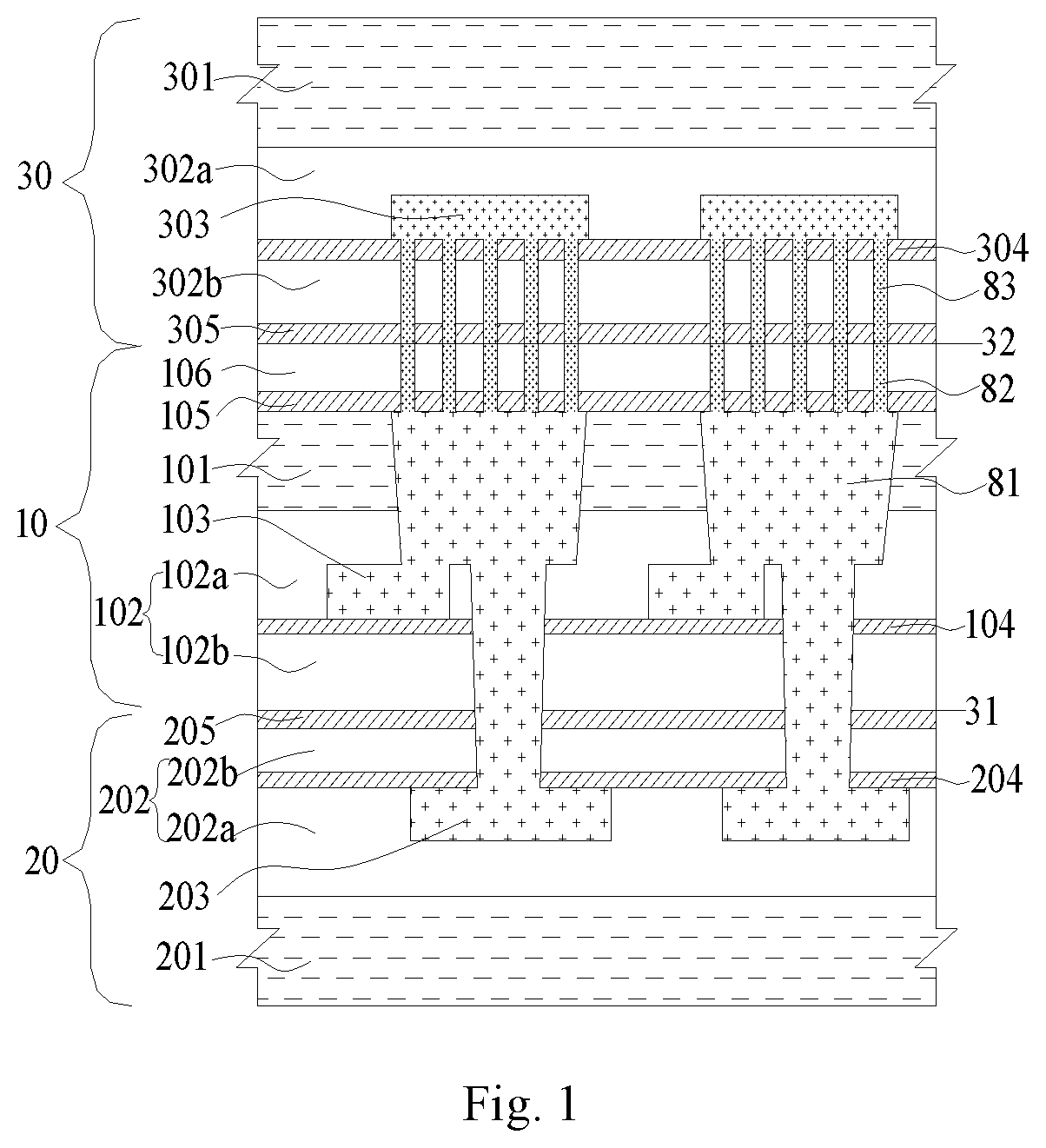

Semiconductor package and manufacturing method thereof

ActiveUS20200273829A1Improve electrical performanceGood workmanshipSemiconductor/solid-state device detailsSolid-state devicesSemiconductor packageElectrical connection

A semiconductor package and a manufacturing method thereof are provided. The semiconductor package includes first dies, an insulating encapsulation laterally encapsulating the first dies, a second die disposed over the portion of the insulating encapsulation and at least partially overlapping the first dies, and a redistribution structure disposed on the insulating encapsulation and electrically connected to the first dies and the second die. A second active surface of the second die faces toward first active surfaces of the first dies. The redistribution structure includes a first conductive via disposed proximal to the first dies, and a second conductive via disposed proximal to the second die. The first and second conductive vias are electrically coupled and disposed in a region of the redistribution structure between the second die and one of the first dies. The first conductive via is staggered from the second conductive via by a lateral offset.

Owner:POWERTECH TECHNOLOGY

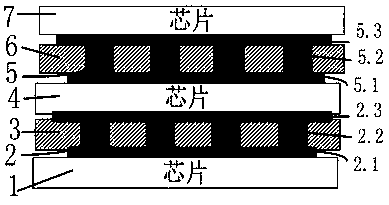

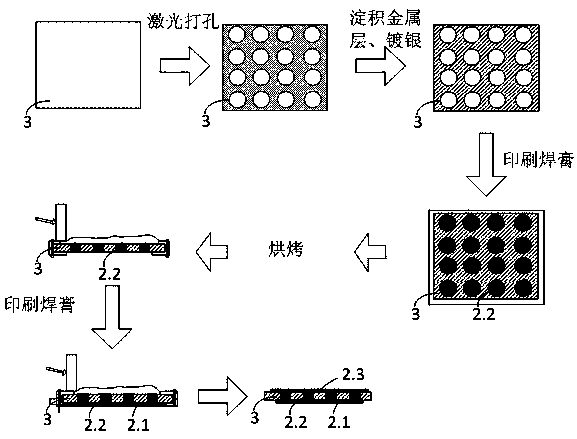

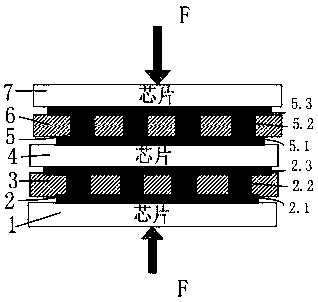

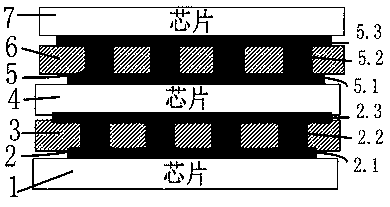

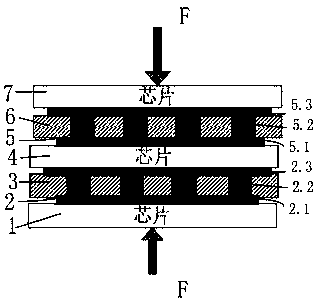

Three-dimensional stacked interconnection structure for SiC device based on nano-silver soldering paste, and preparation method

ActiveCN108550566AImprove thermal conductivityImprove insulation performanceMaterial nanotechnologySemiconductor/solid-state device detailsInterconnectionTemperature resistance

The invention provides a three-dimensional stacked interconnection structure for a SiC device based on nano-silver soldering paste, and a preparation method. The interconnection structure comprises the nano-silver soldering paste and a ceramic plate. The nano-silver soldering paste is disposed in through holes in the ceramic plate, and a conductive circuit is formed after sintering. Furthermore, the nano-silver soldering paste is sintered to achieve the stacked interconnection of chip electrodes. The ceramic plate serves as an insulating plate and an underlay layer, thereby increasing the distance between two chips, and avoiding the edge breakdown effect between the chips. The connection of the interconnection structure can achieve the longitudinal interconnection of a plurality of chips,and the selected material comprises a ceramic substrate and a nano-silver soldering paste. The main component of the sinter nano-silver soldering paste is silver, and the conductivity and temperatureresistance of the sintered nano-silver soldering paste are close to the conductivity and temperature resistance of pure silver. The nano-silver soldering paste and the ceramic substrate are both madeof high temperature resistant materials, and can be used for the interconnection of a big power chip. Compared with other parking modes, the structure is simple in structure, is high in operability, is wide in application range, and can achieve the simple and effective high-temperature and high-voltage stacked packaging.

Owner:INST OF ELECTRONICS ENG CHINA ACAD OF ENG PHYSICS

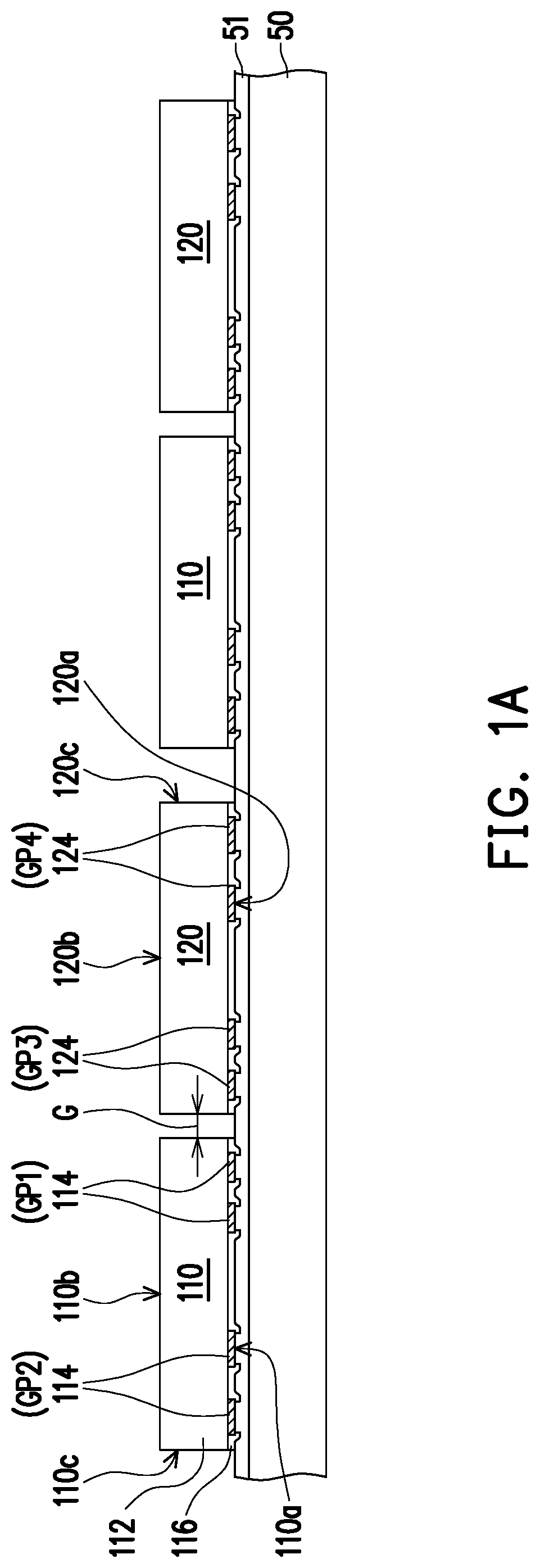

Semiconductor package and manufacturing method thereof

ActiveUS20200273803A1Improve electrical performanceGood workmanshipSemiconductor/solid-state device detailsSolid-state devicesRedistribution layerSemiconductor package

A semiconductor package and a manufacturing method thereof are provided. The semiconductor package includes a first and a second active dies separately arranged, an insulating encapsulation at least laterally encapsulating the first and the second active dies, a redistribution layer disposed on the insulating encapsulation, the first and the second active dies, and a fine-pitched die disposed on the redistribution layer and extending over a gap between the first and the second active dies. The fine-pitched die has a function different from the first and the second active dies. A die connector of the fine-pitched die is connected to a conductive feature of the first active die through a first conductive pathway of the redistribution layer. A first connecting length of the first conductive pathway is substantially equal to a shortest distance between the die connector of the fine-pitched die and the conductive feature of the first active die.

Owner:POWERTECH TECHNOLOGY

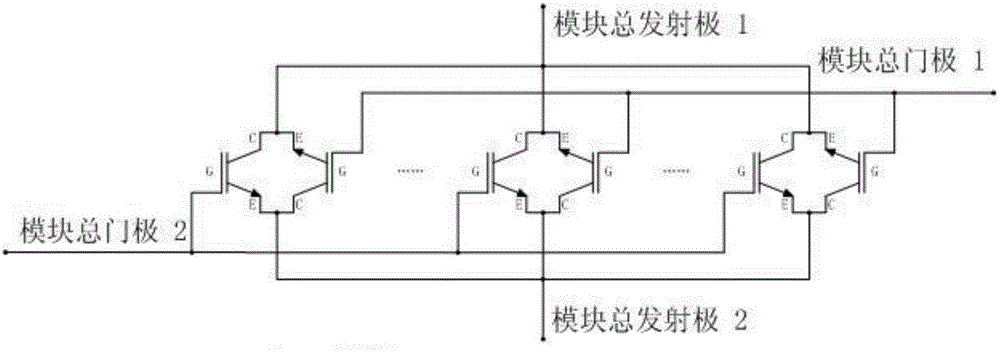

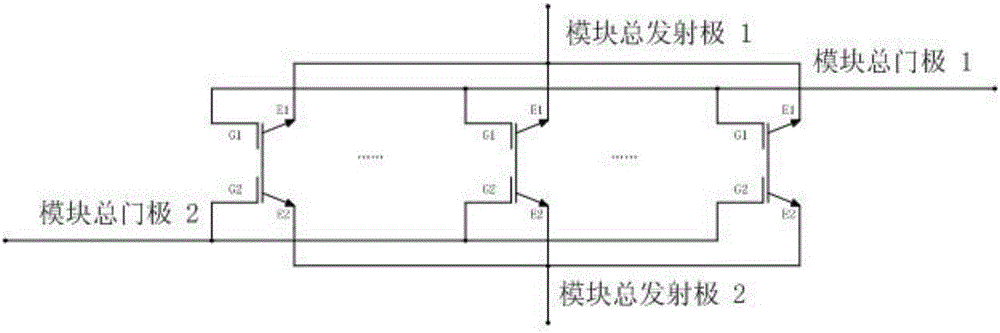

Packaging structure of single-chip bidirectional IGBT module

InactiveCN105789293ASolving Thermo-Mechanical Fatigue FailuresImprove current shock resistance and reliabilitySemiconductor/solid-state device detailsSolid-state devicesDBcCopper

The invention relates to a packaging structure of a single-chip bidirectional IGBT module. The packaging structure comprises a bottom metal plate, a bottom DBC plate, a single-chip bidirectional IGBT device, a top DBC plate and a top metal plate. The bottom DBC plate comprises a second gate electrode copper clad region and a second emission electrode copper clad region. The second gate electrode and the second emission electrode of the single-chip bidirectional IGBT device are respectively connected with the second gate electrode copper clad region and the second emission electrode copper clad region. The top DBC plate comprises a first gate electrode copper clad region and a first emission electrode copper clad region. The electrodes of the upper and lower surfaces of the single-chip bidirectional IGBT device are respectively welded on the two DBC plates, and metal bonding line interconnection is replaced by welding interconnection so that the problem of thermal mechanical fatigue failure of metal bonding lines and the welding interface thereof can be solved, and current surge resistant capacity and reliability of the module can be enhanced; meanwhile, interconnection distance between external pins and the electrodes can be shortened by welding interconnection in comparison with that of metal bonding line interconnection so that the parasitic parameters of the module can be reduced.

Owner:HUNAN UNIV +1

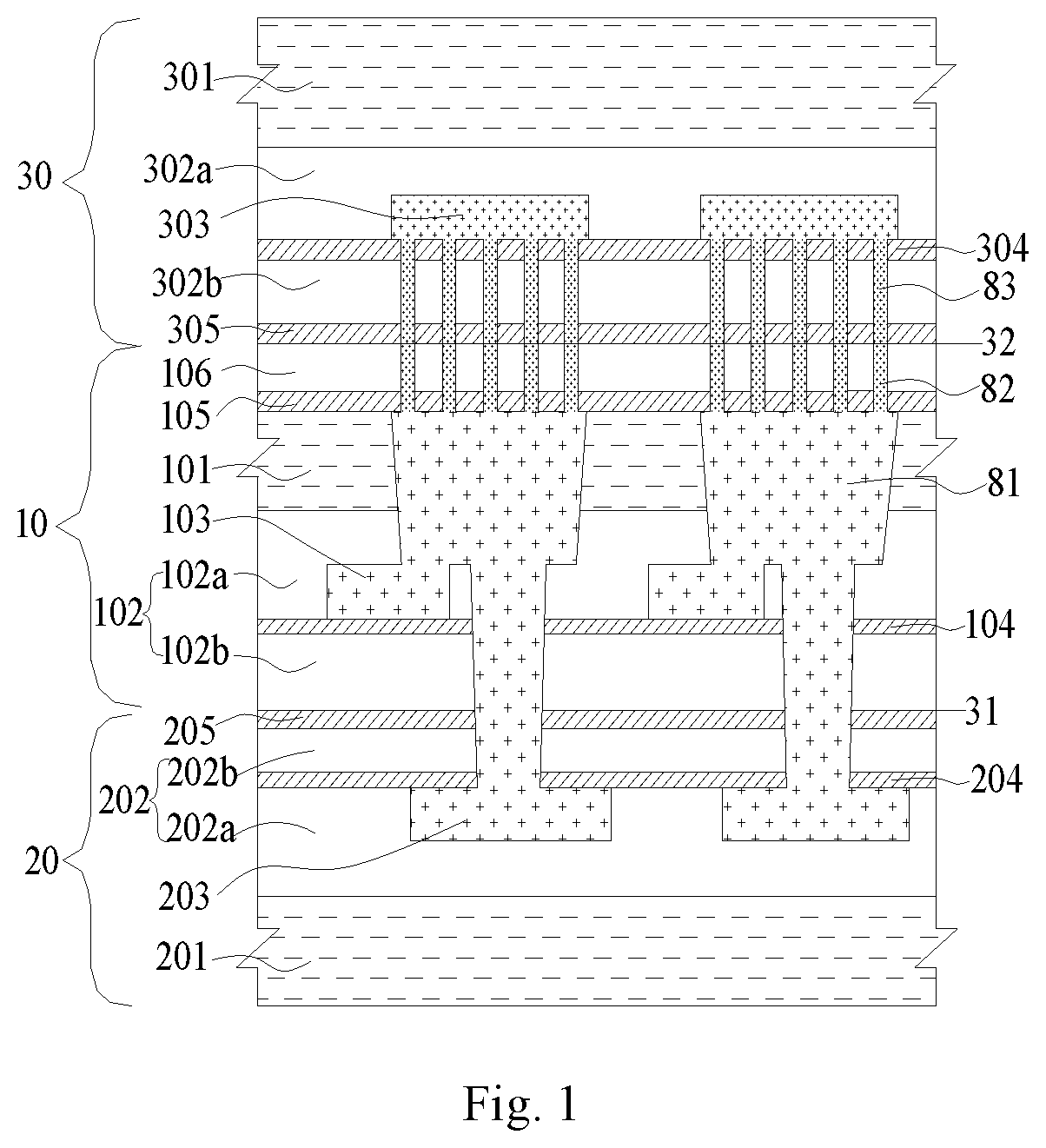

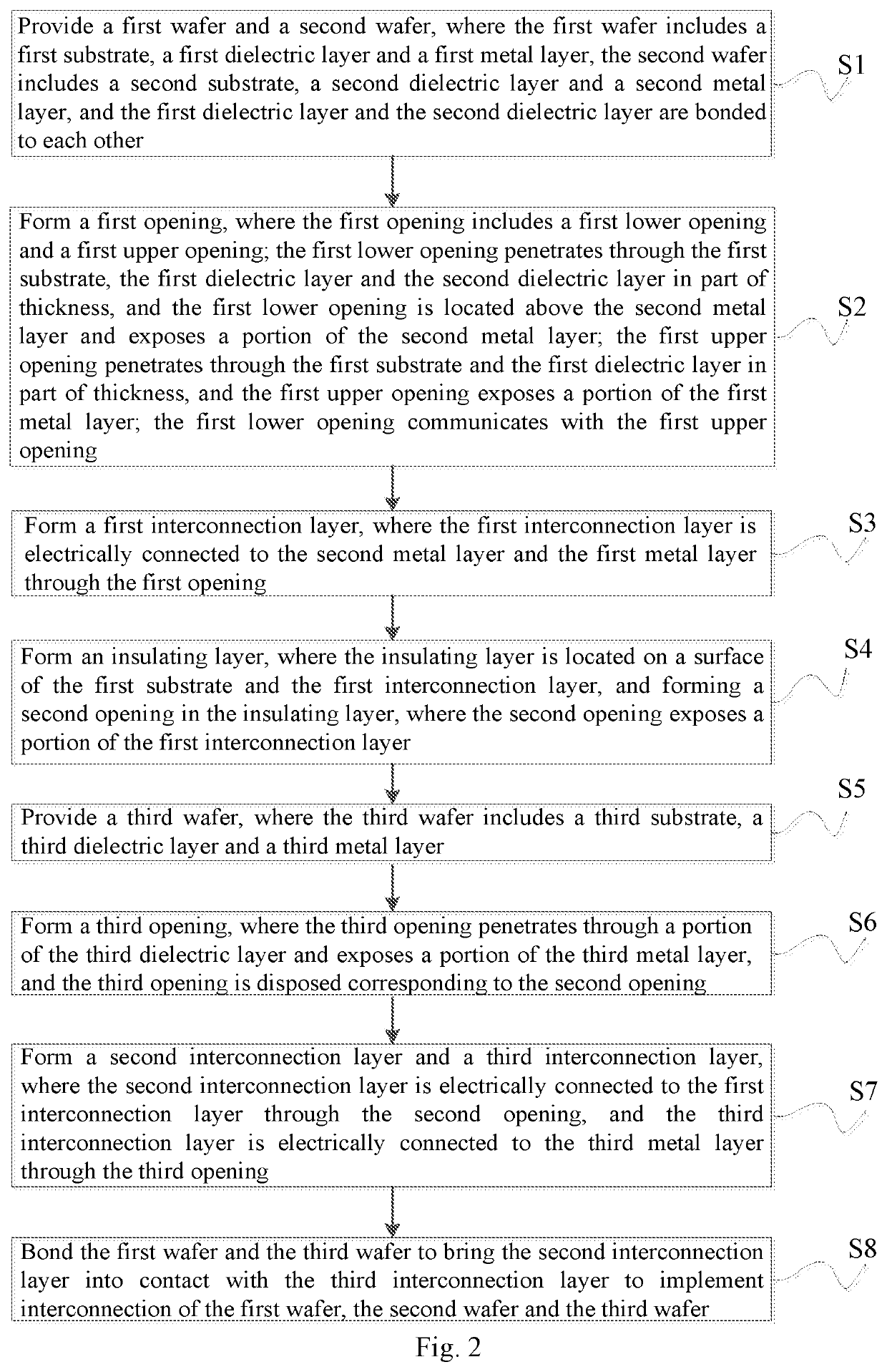

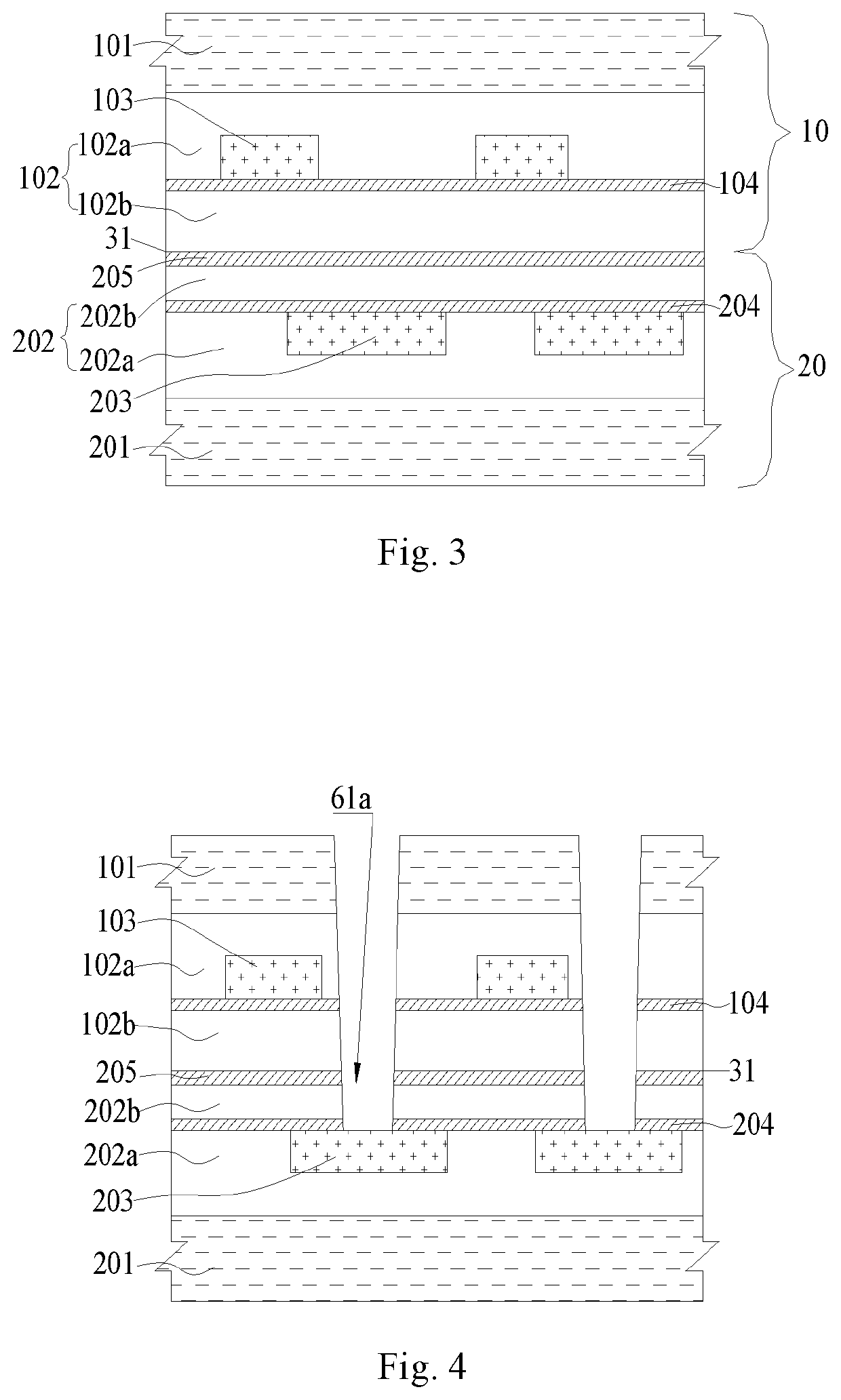

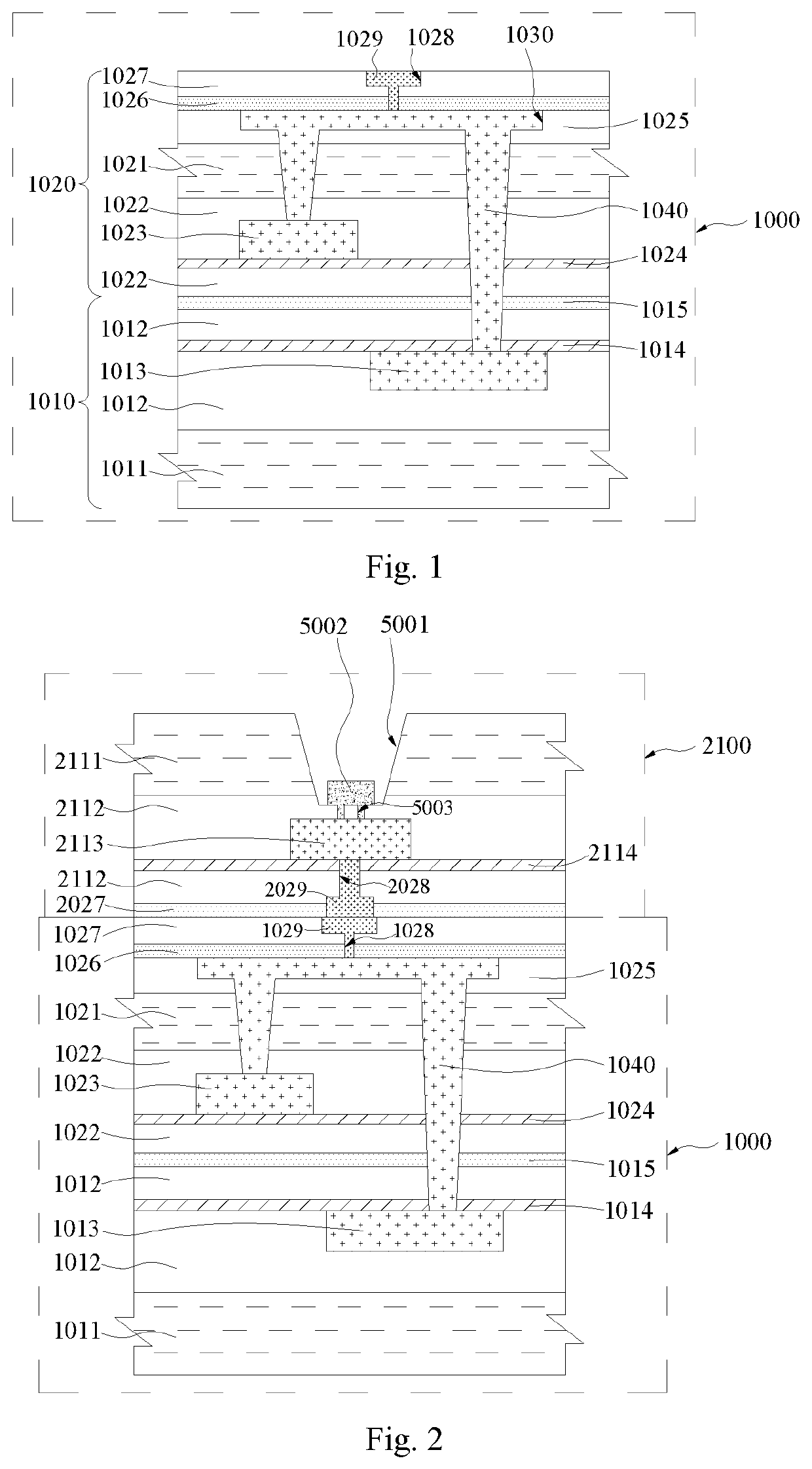

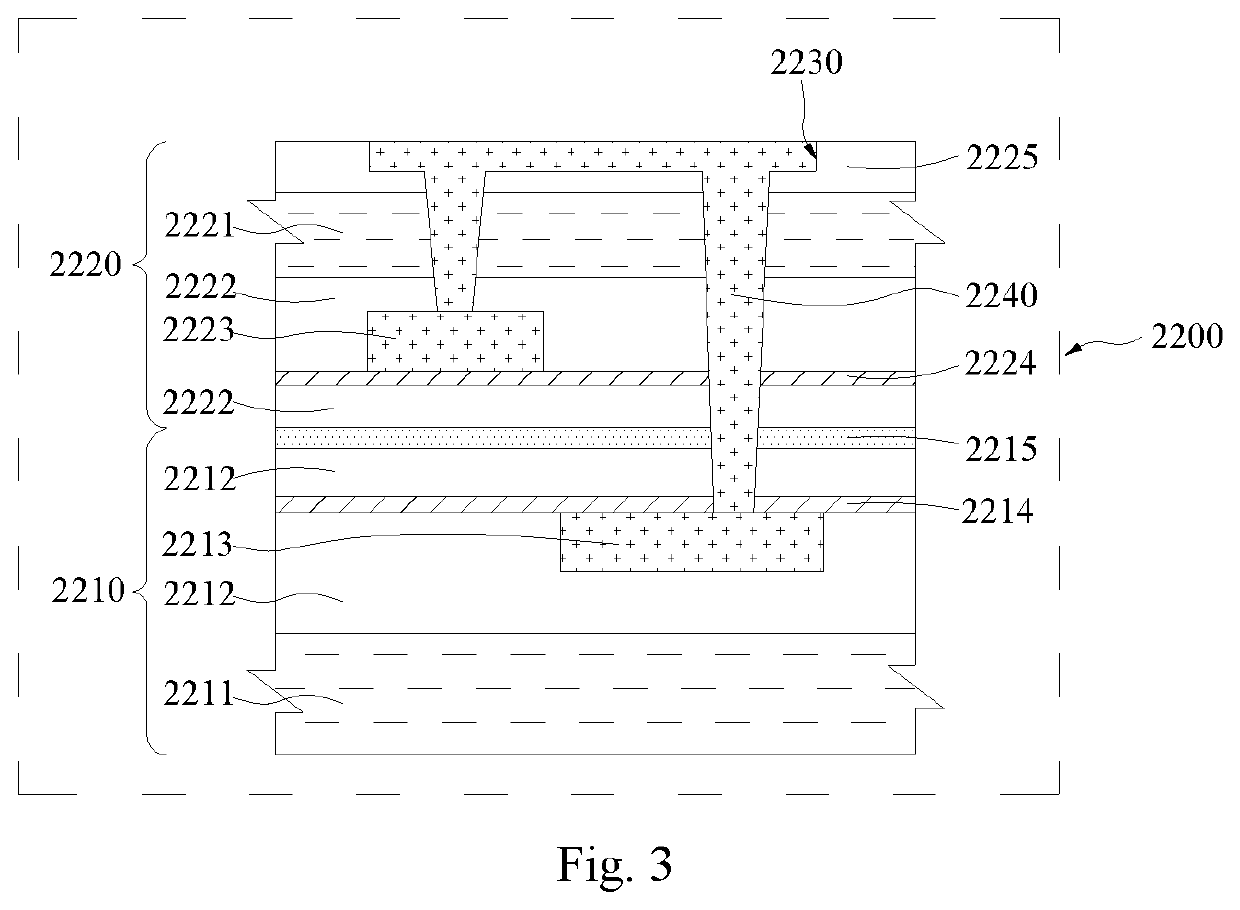

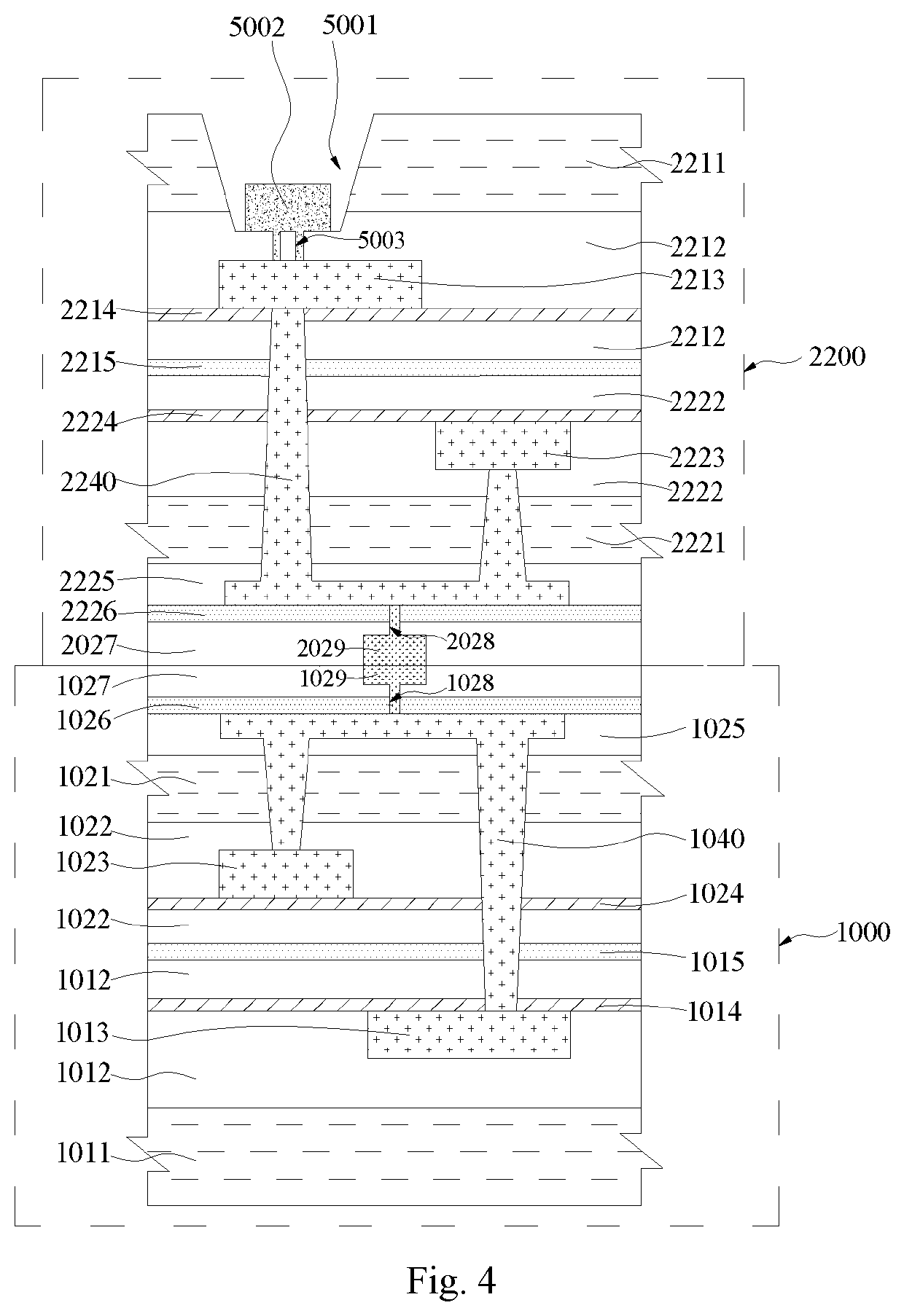

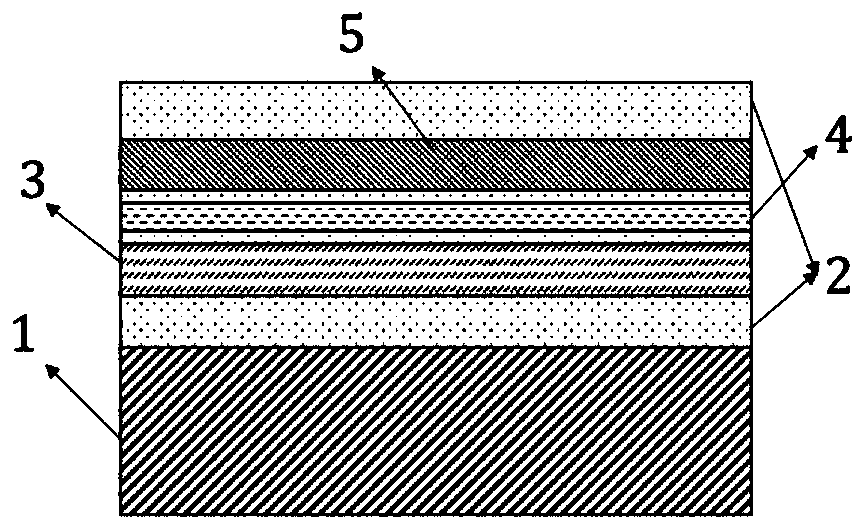

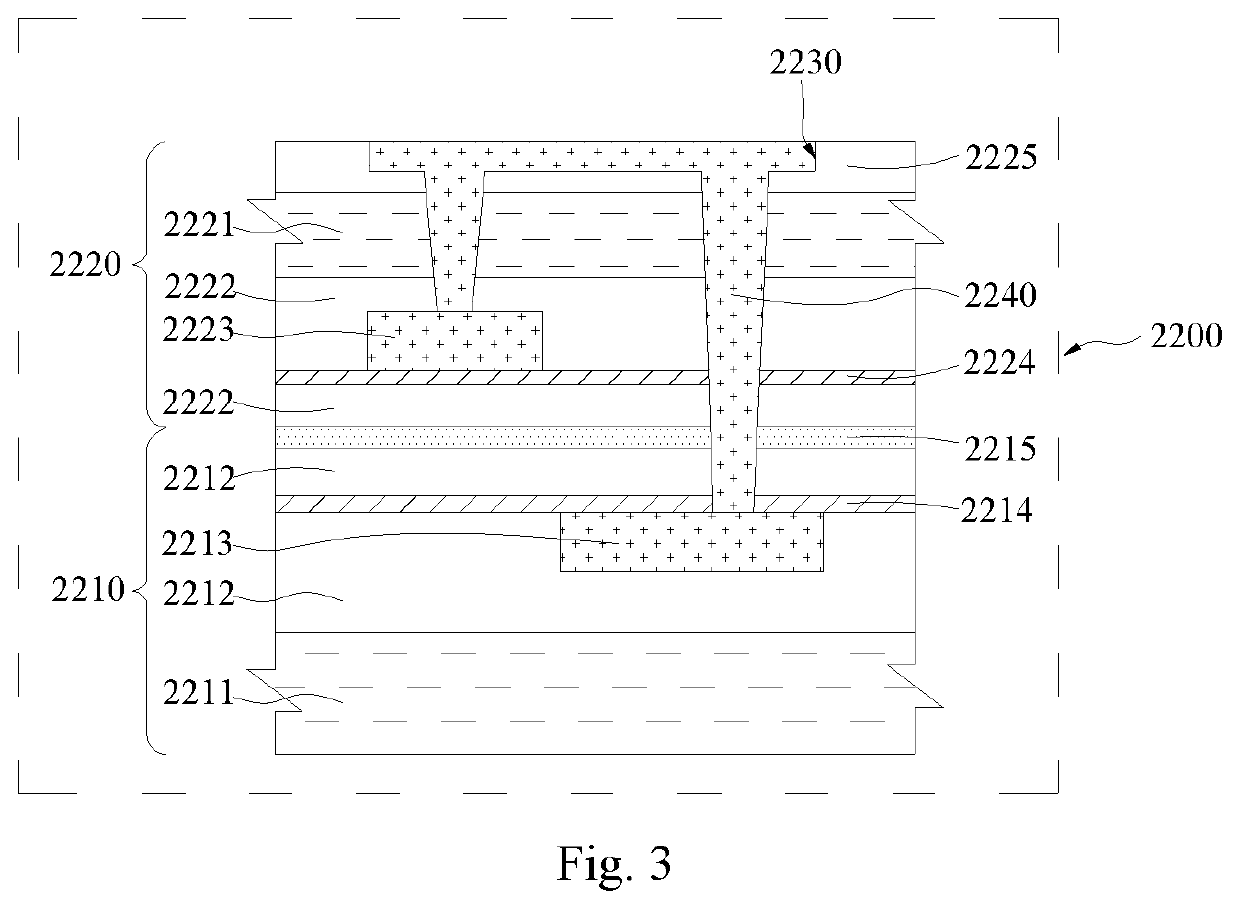

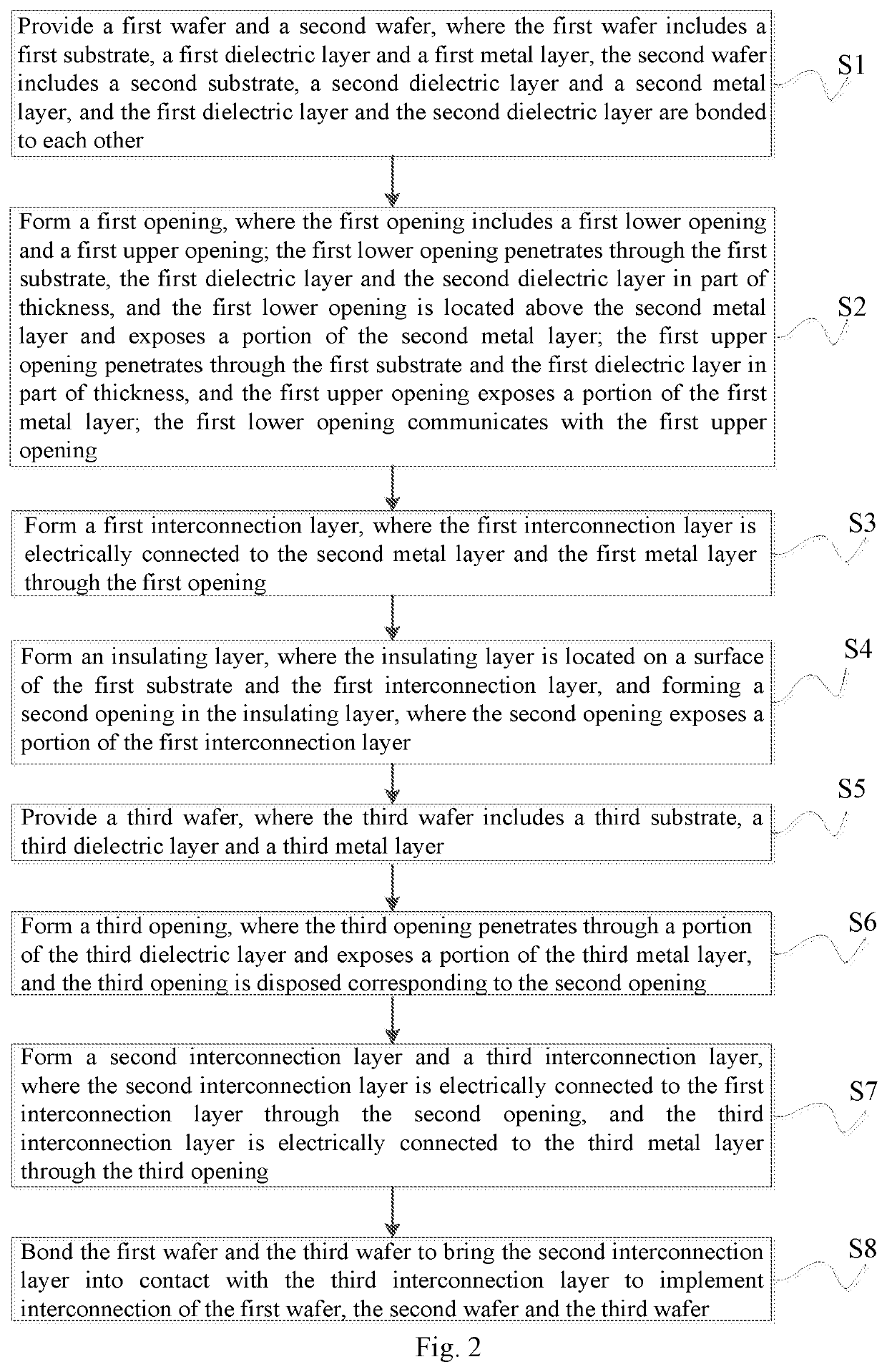

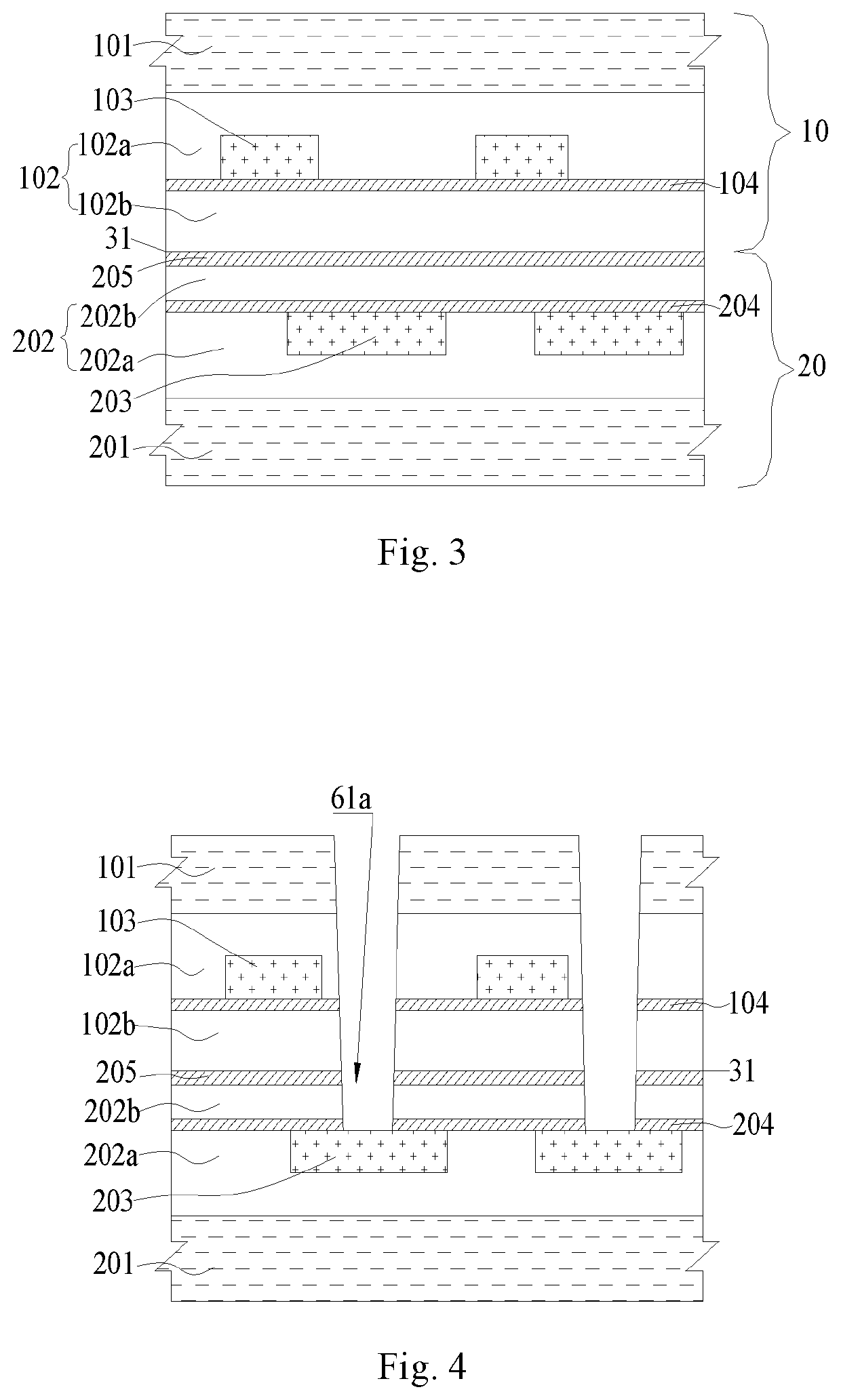

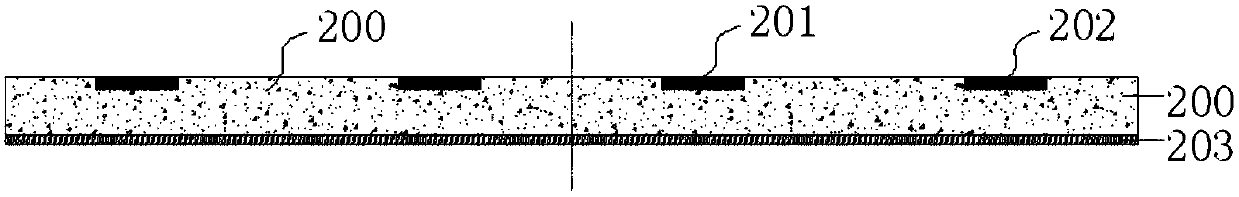

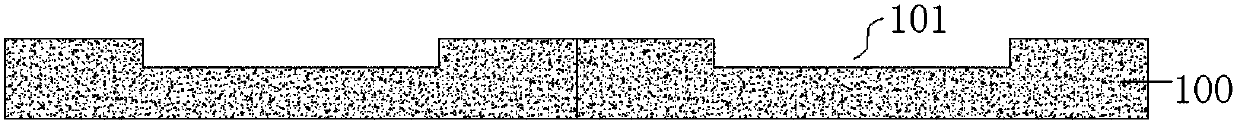

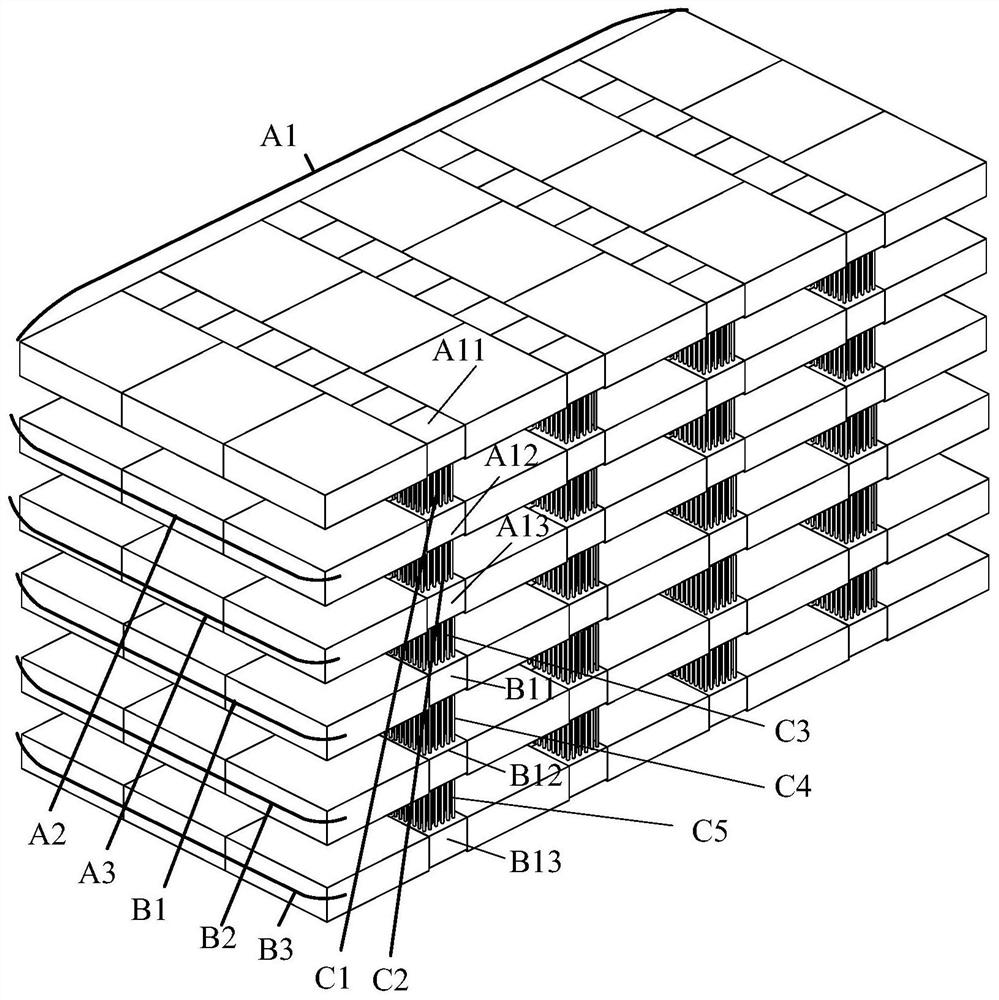

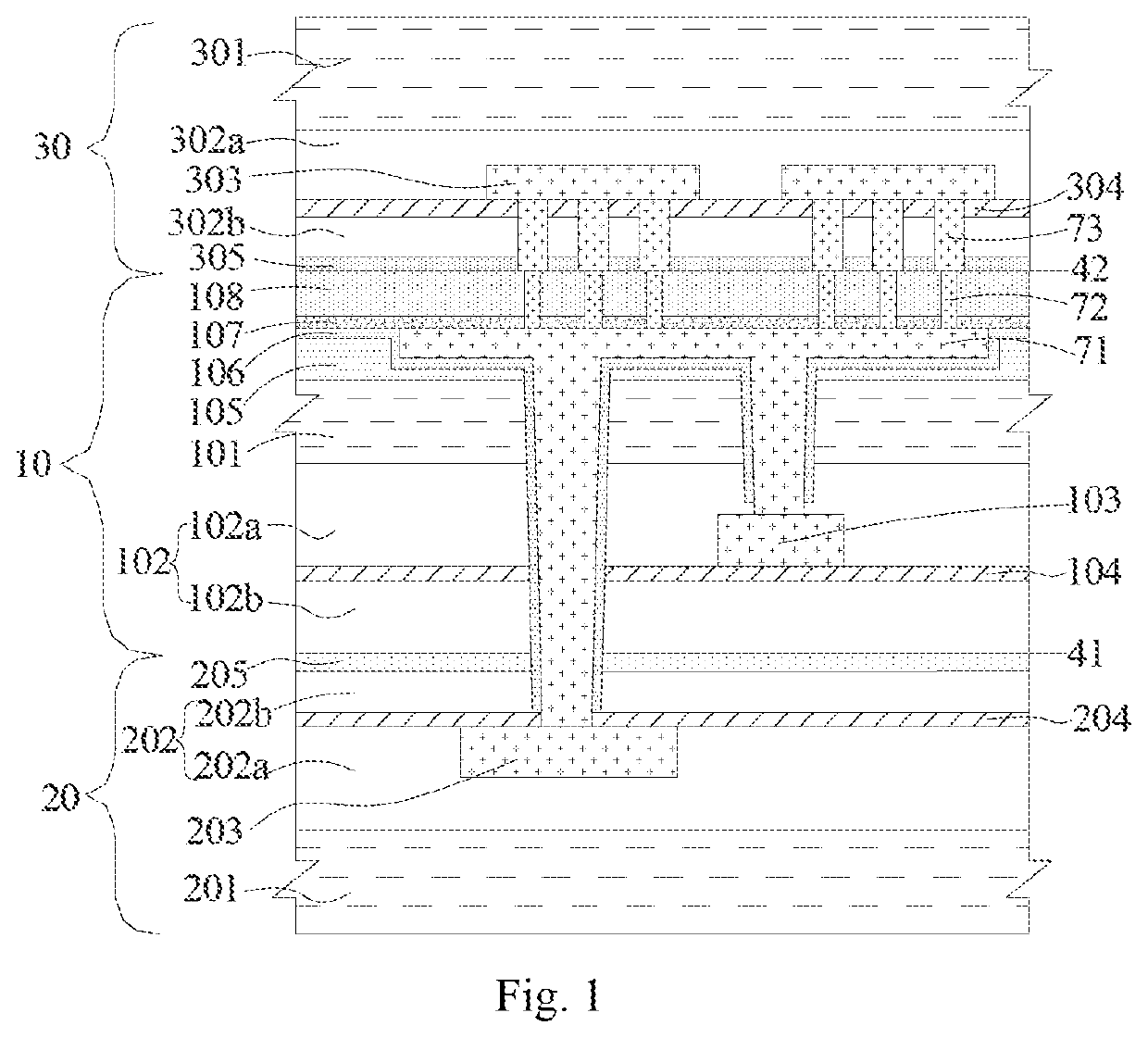

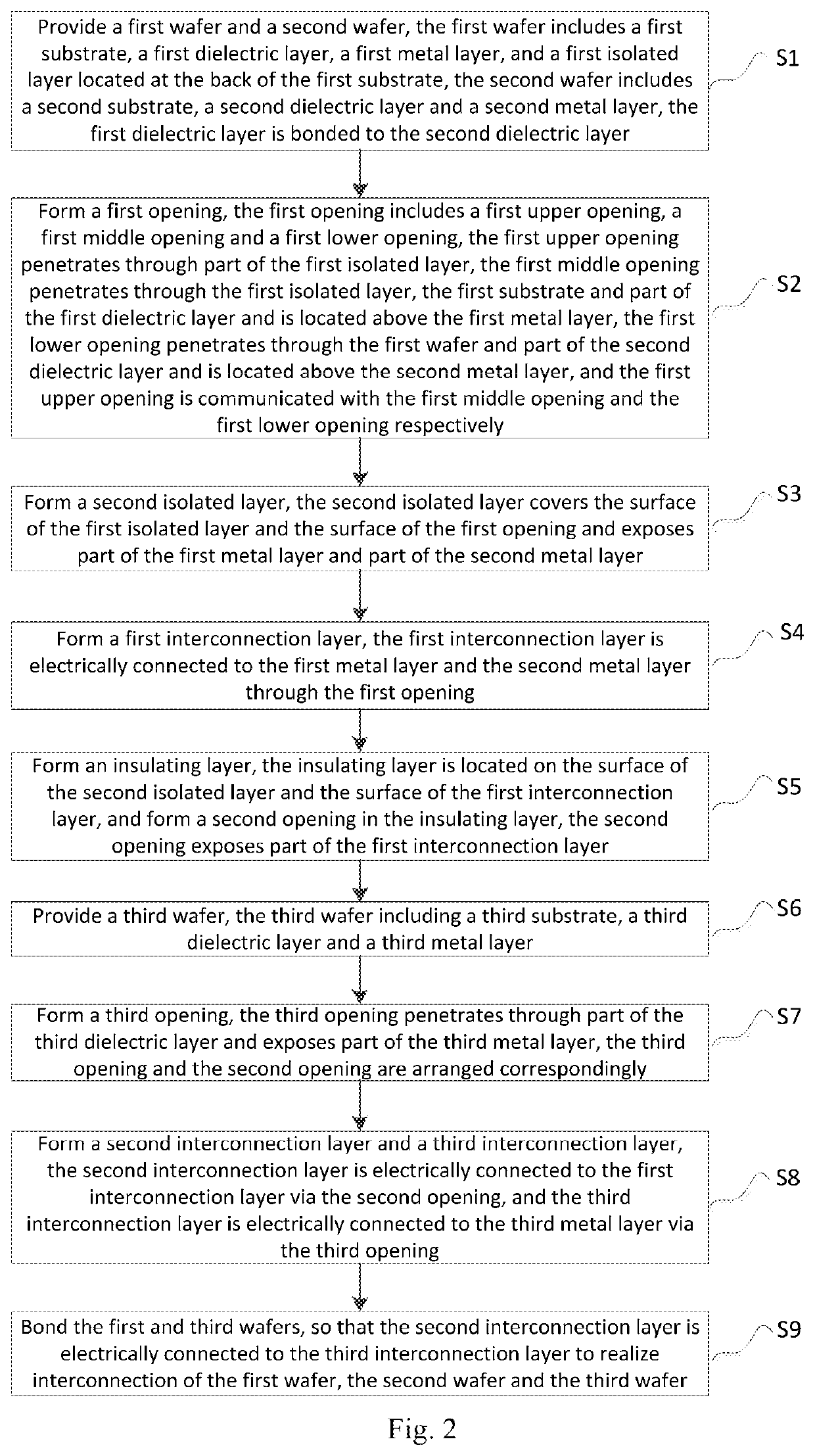

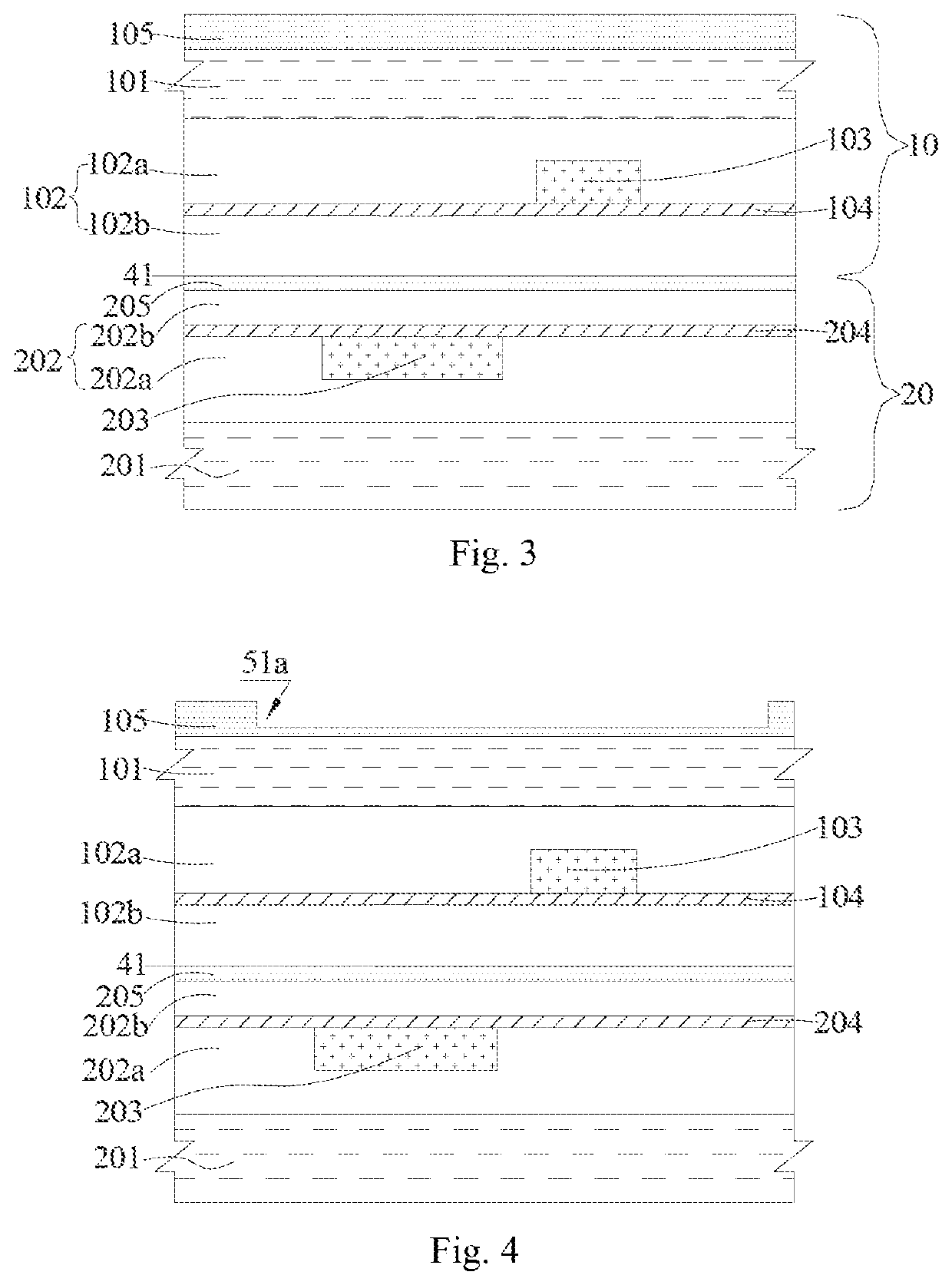

Multi-wafer stack structure and forming method thereof

ActiveUS11107794B2Reduce thicknessIncrease transfer speedSemiconductor/solid-state device detailsSolid-state devicesWaferingWafer stacking

A multi-wafer stack structure and fabricating method thereof are disclosed. In the multi-wafer stack structure, the first interconnection layer is electrically connected to the second metal layer and the first metal layer via the first opening, the second interconnection layer is electrically connected to the first interconnection layer via the second openings, the third interconnection layer is electrically connected to the third metal layer via the third openings, and the second interconnection layer is in contact with the third interconnection layer, so that there is no need to reserve the wire pressure welding space between the wafers and a silicon substrate is eliminated, the overall device thickness of the multi-wafer stack package is reduced. Moreover, the design processing of the silicon substrate and a plurality of common pads on the silicon substrate is eliminated, thereby reducing the parasitic capacitance and power loss, and increasing the transmission speed.

Owner:WUHAN XINXIN SEMICON MFG CO LTD

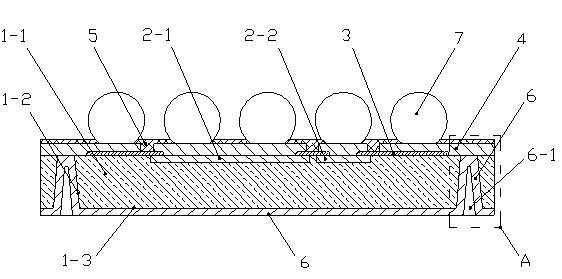

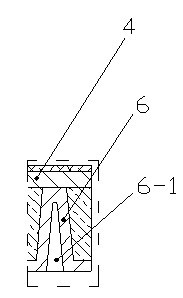

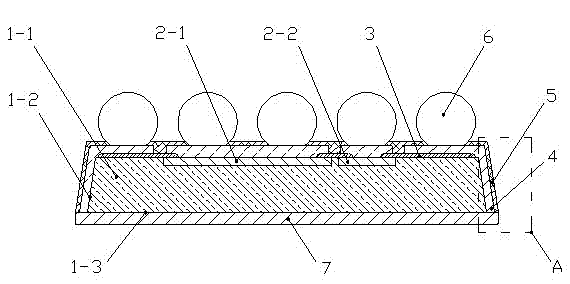

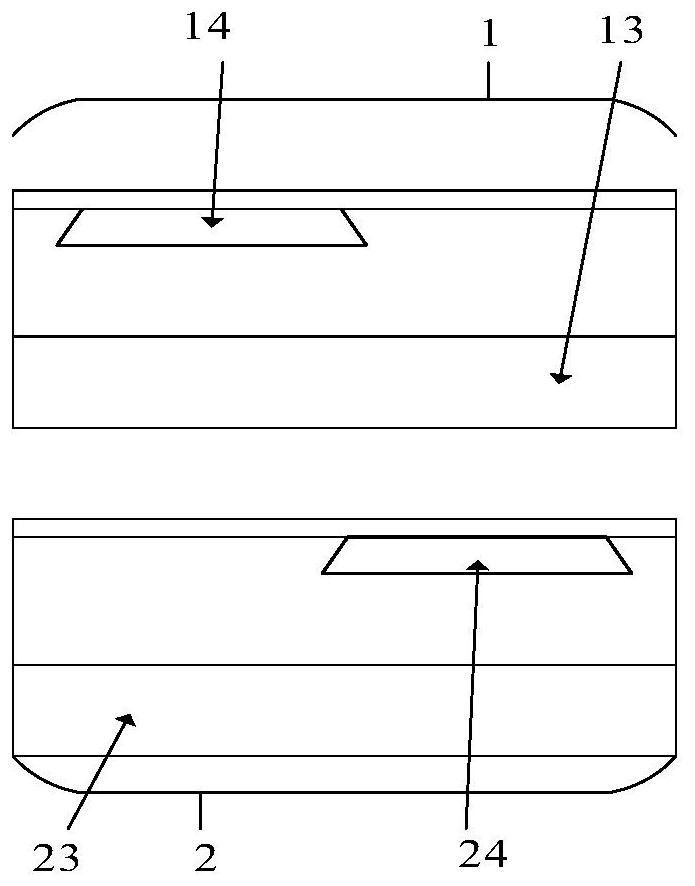

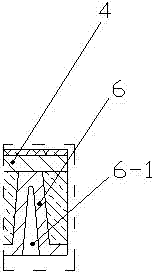

Rear through-hole interconnected wafer level MOSFET (metal oxide semiconductor field effect transistor) packaging structure and implementation method

ActiveCN102122671AImprove current carrying capacityImprove cooling effectSemiconductor/solid-state device detailsSolid-state devicesMOSFETSolder ball

The invention relates to a rear through-hole interconnected wafer level MOSFET (metal oxide semiconductor field effect transistor) packaging structure and an implementation method. A chip source electrode (2-1) and a chip gate electrode (2-2) are arranged on the front surface of a chip body (1-1); chip surface protecting layers (3) are arranged on the front surfaces of the chip body, the chip source electrode and the chip gate electrode; front surface circuit layers (4) are arranged on the surfaces of the chip body, the chip source electrode, the chip gate electrode and the chip surface protecting layers; circuit surface protecting layers (5) are arranged on the surfaces of the front surface circuit layers and the chip surface protecting layers; solder balls (7) are arranged on the surfaces of the front surface circuit layers; a chip through hole (1-2) is arranged by penetrating the front surface and the back surface of the chip body; and a circuit layer (6) is arranged on the back surface of the chip body, the circuit layer (6) is filled in the chip through hole, and the circuit layer filled in the chip through hole is in direct contact with the side wall of the chip through hole and interconnected with the front surface circuit layers. According to the invention, the packaging structure has high performance; and the process method which is used for implementing the structure and has the advantages of high production efficiency and low packaging cost.

Owner:JIANGYIN CHANGDIAN ADVANCED PACKAGING CO LTD

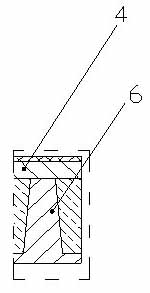

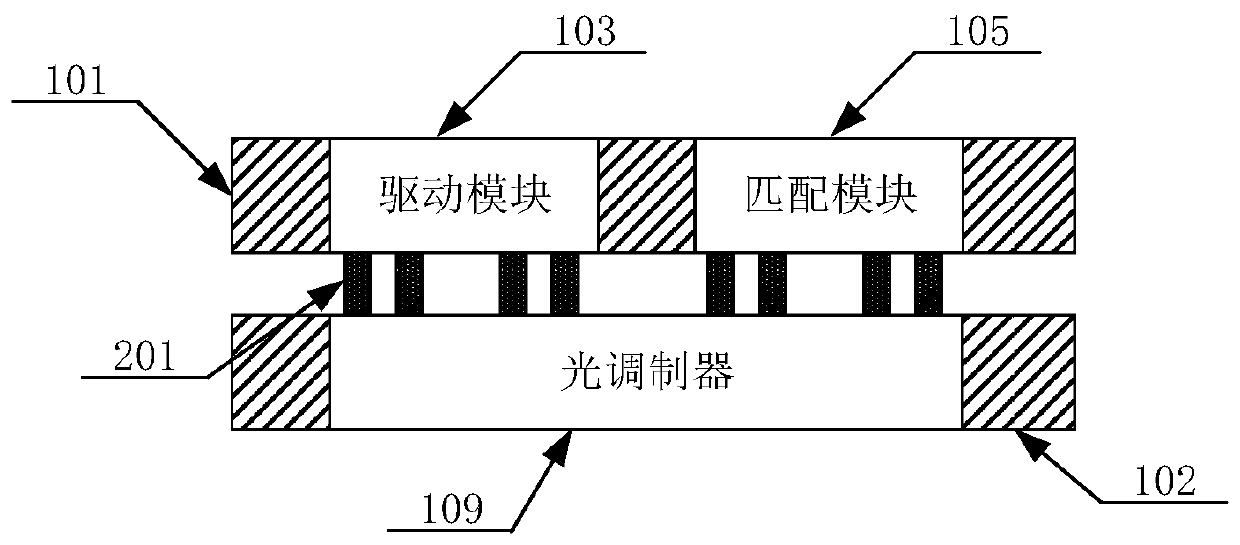

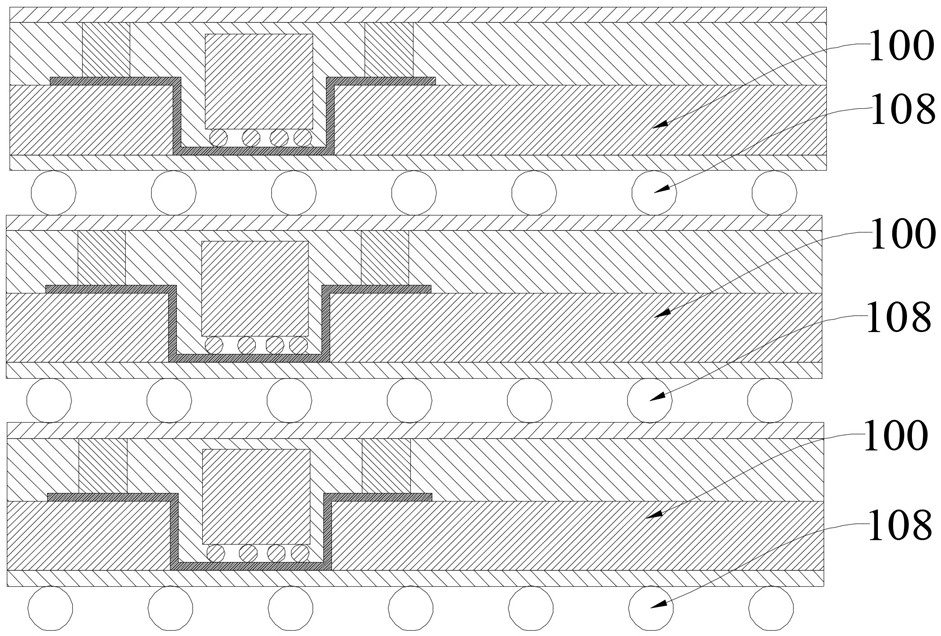

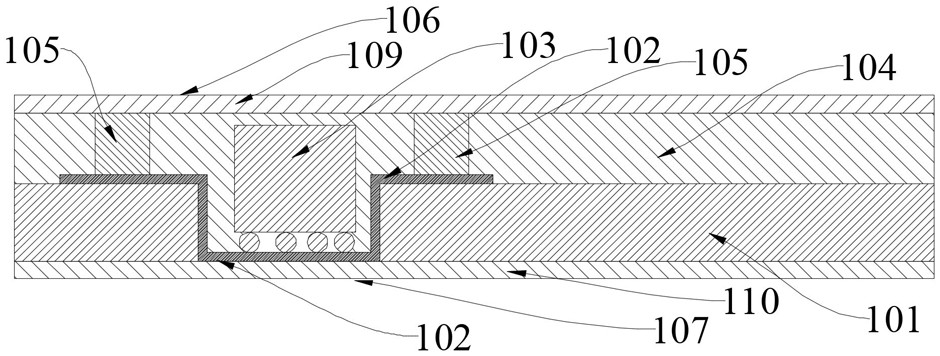

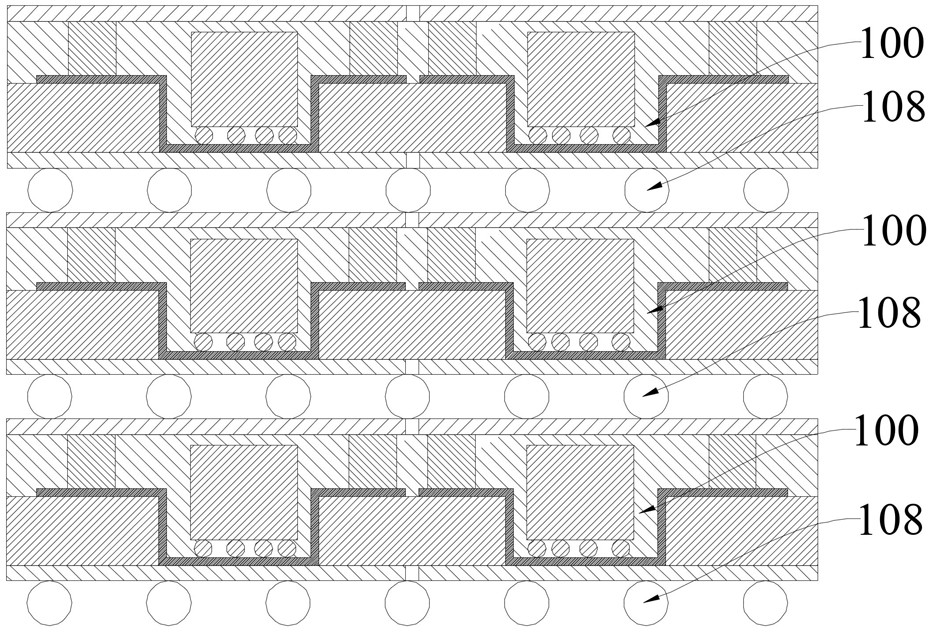

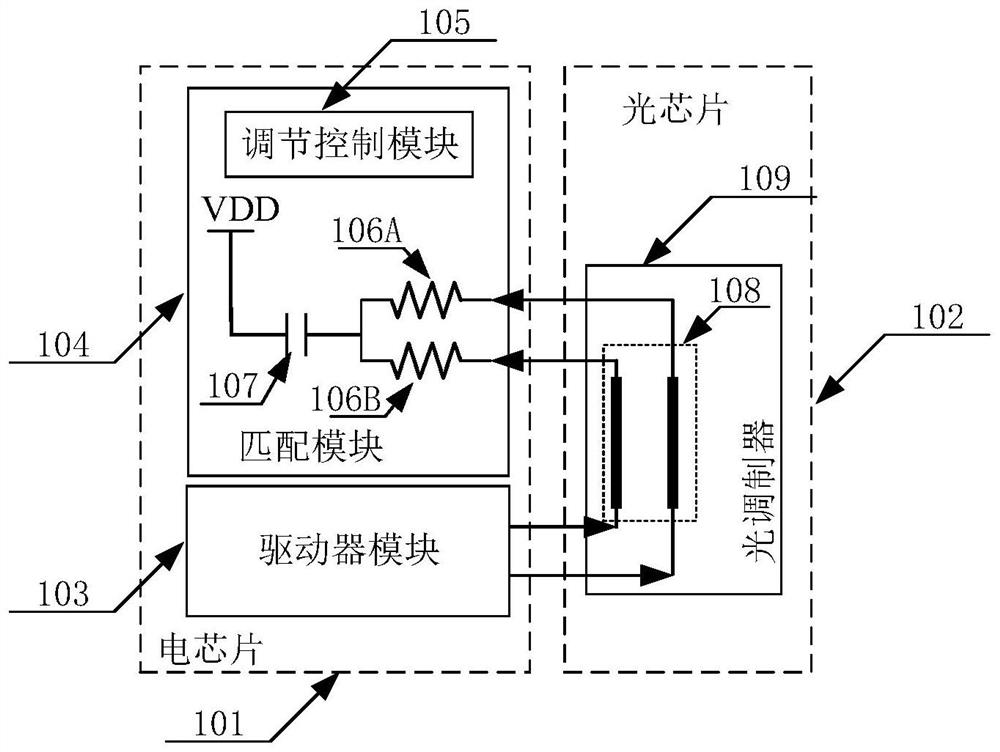

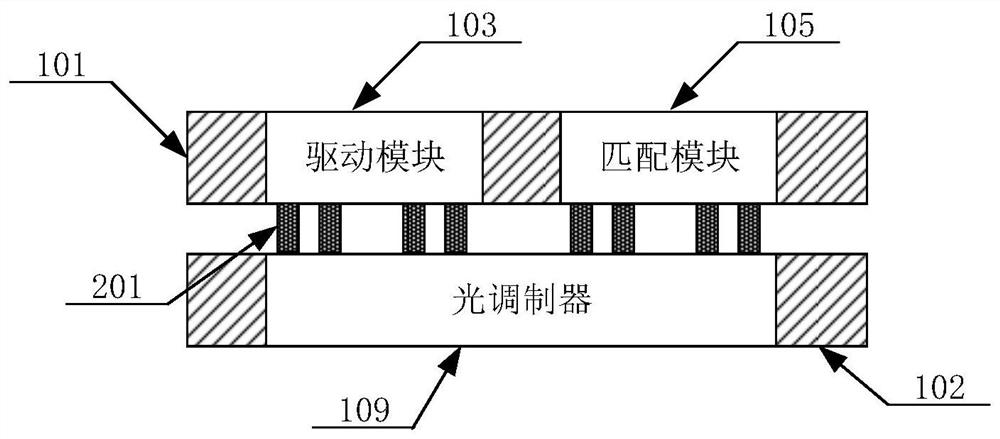

Optical emitter

ActiveCN110311735AImprove transmission performanceImprove signal qualityElectromagnetic transmittersEngineeringImpedance matching

Owner:SHANGHAI JIAO TONG UNIV

Three-dimensional fan-out packaging structure and preparation method thereof

InactiveCN114566482AEasy to stack in three dimensionsReduce packaging processSemiconductor/solid-state device detailsSolid-state devicesPlastic packagingSolder ball

The invention discloses a three-dimensional fan-out packaging structure and a preparation method thereof, and the method comprises the steps: digging a groove in a carrier plate, preparing a metal wiring layer at the groove and the periphery of the groove, then pasting a core particle, leading out a part of pins of the core particle to the front surface of the carrier plate through the metal wiring layer, carrying out the plastic packaging, preparing a conductive column at a plastic packaging layer, and leading out the part of pins. Then preparing a first rewiring layer and a first dielectric layer on the plastic packaging layer to complete front packaging; and thinning the back surface of the carrier plate until the metal wiring layer is formed and the other part of pins of the core particles are exposed, then preparing a second rewiring layer and a second dielectric layer, completing preparation of fan-out packaging units of double-sided fan-out, stacking the fan-out packaging units according to needs, and then connecting the fan-out packaging units by adopting solder balls to obtain the three-dimensional fan-out packaging structure. According to the fan-out packaging unit with the two fan-out surfaces, the interconnection distance can be effectively reduced, three-dimensional stacking is facilitated, the fan-out packaging unit has great advantages in electrical interconnection performance, the loss is smaller, the efficiency is higher, the packaging process difficulty is greatly reduced, and the packaging cost is reduced.

Owner:WUHAN UNIV

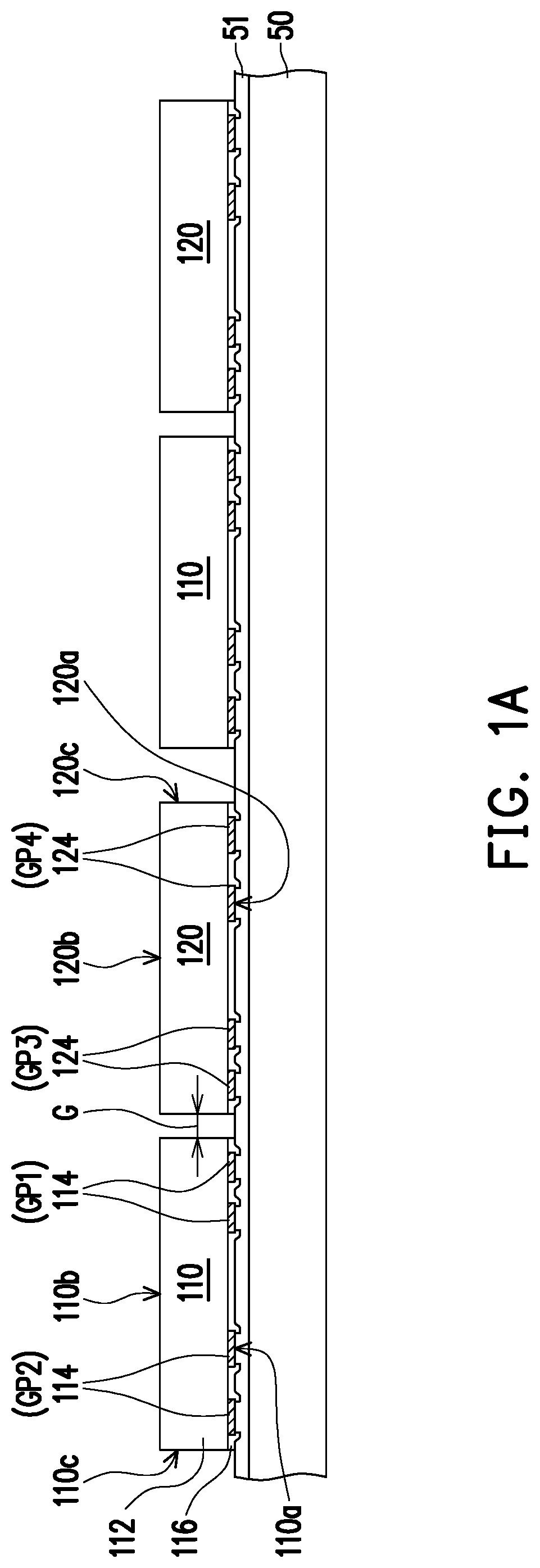

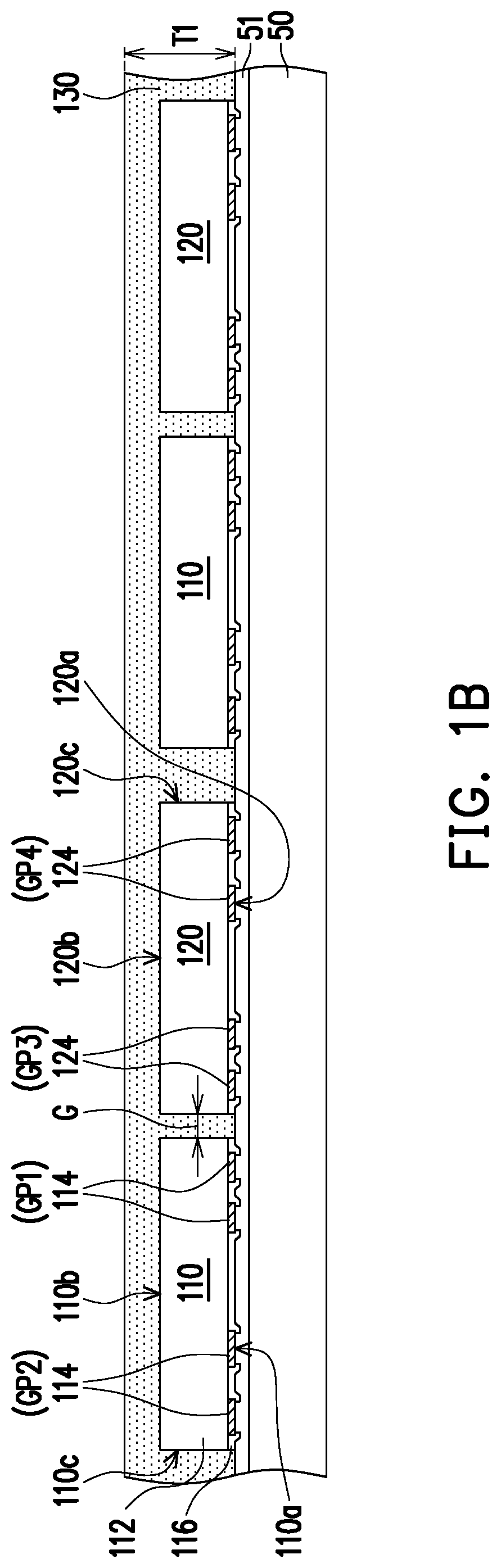

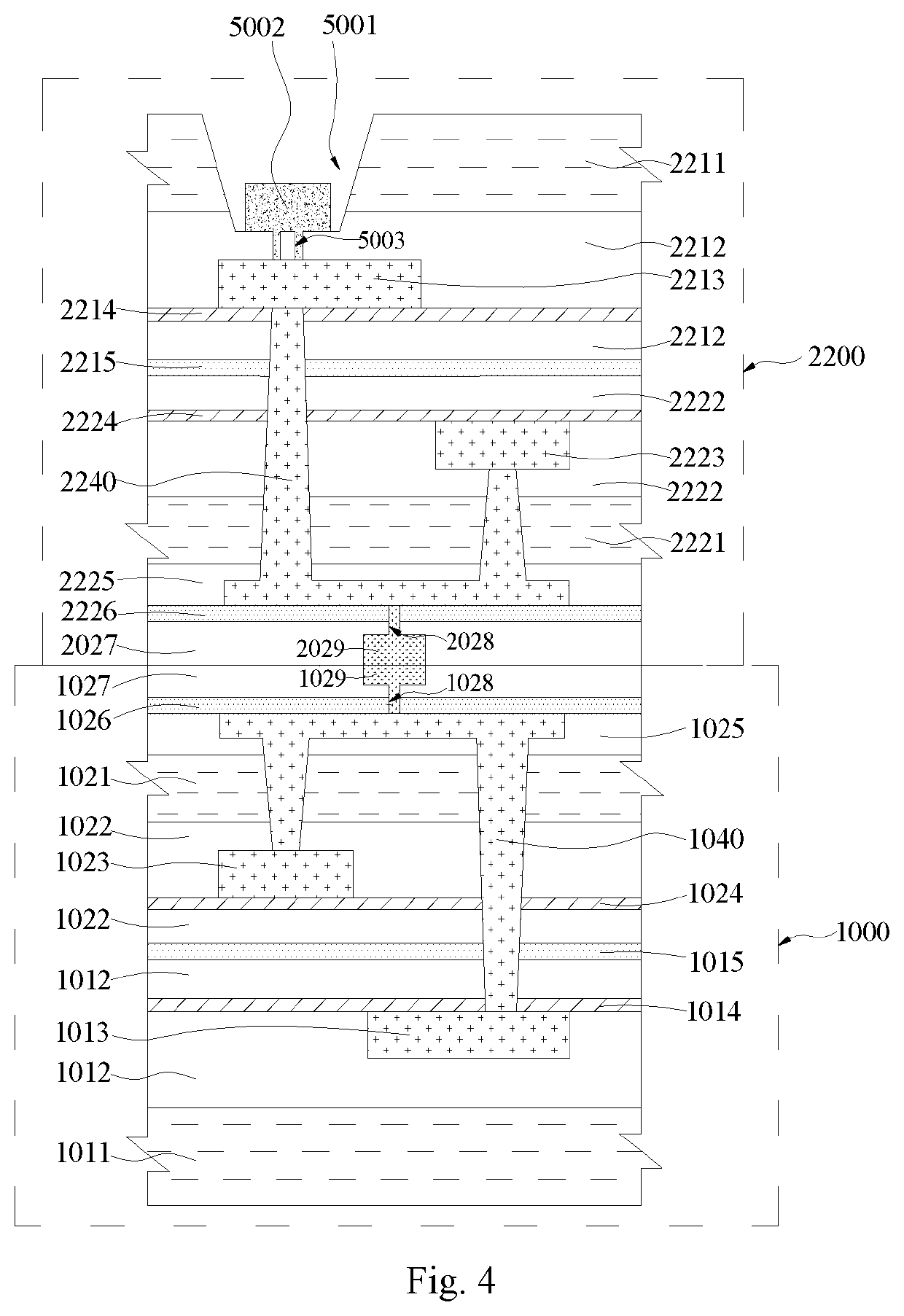

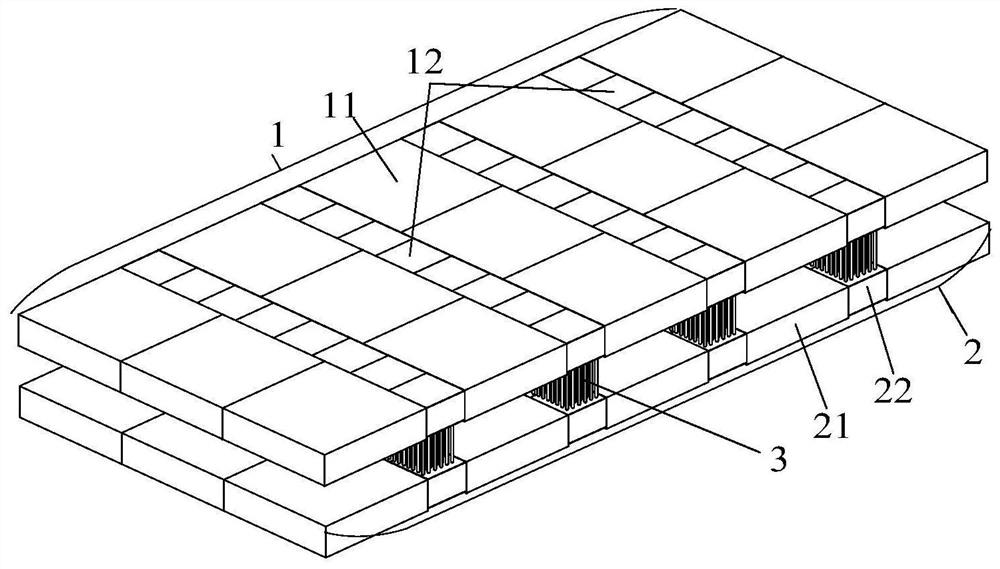

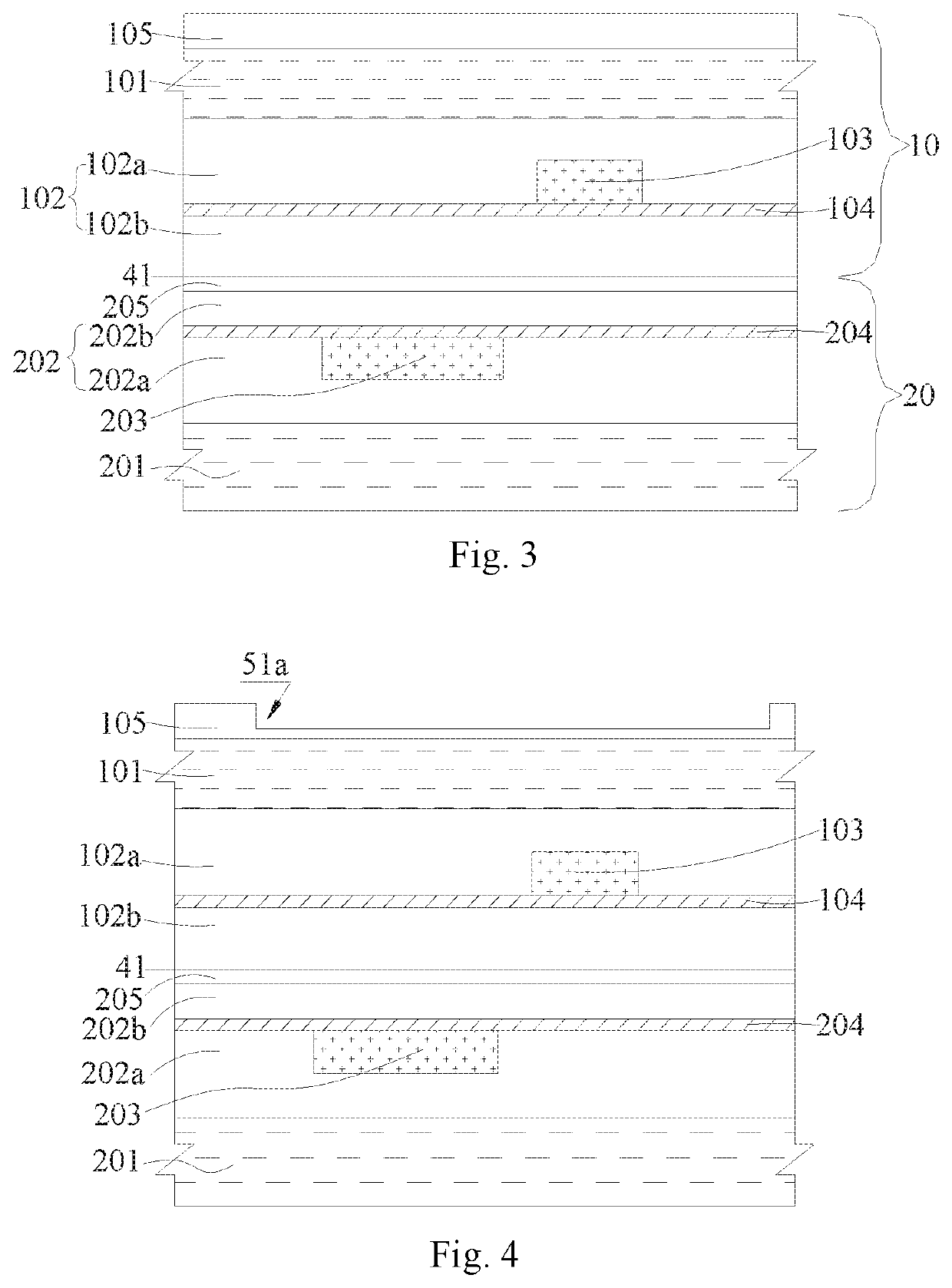

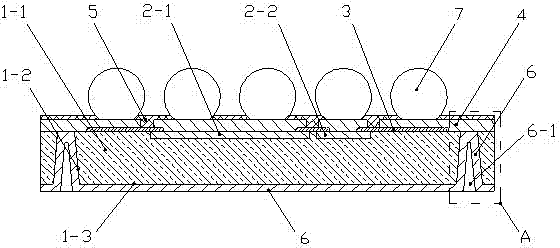

Multi-wafer bonding structure and bonding method

ActiveUS10930619B2Shorten the interconnection distanceIncrease transfer speedSemiconductor/solid-state device detailsSolid-state devicesWaferingElectrical connection

A multi-wafer bonding structure and bonding method are disclosed. The multi-wafer bonding structure includes a first unit and a second unit, a metal layer of each wafer in the first unit electrically connected to an interconnection layer of the first unit, a first bonding layer in the first unit electrically connected to the interconnection layer of the first unit, a second bonding layer in the second unit electrically connected to a metal layer of the second unit, and the first bonding layer being in contact with the second bonding layer to achieve an electrical connection, thereby achieving the electrical connection among the interconnection layer of the first unit, the first bonding layer, the second bonding layer and the metal layer of each wafer.

Owner:WUHAN XINXIN SEMICON MFG CO LTD

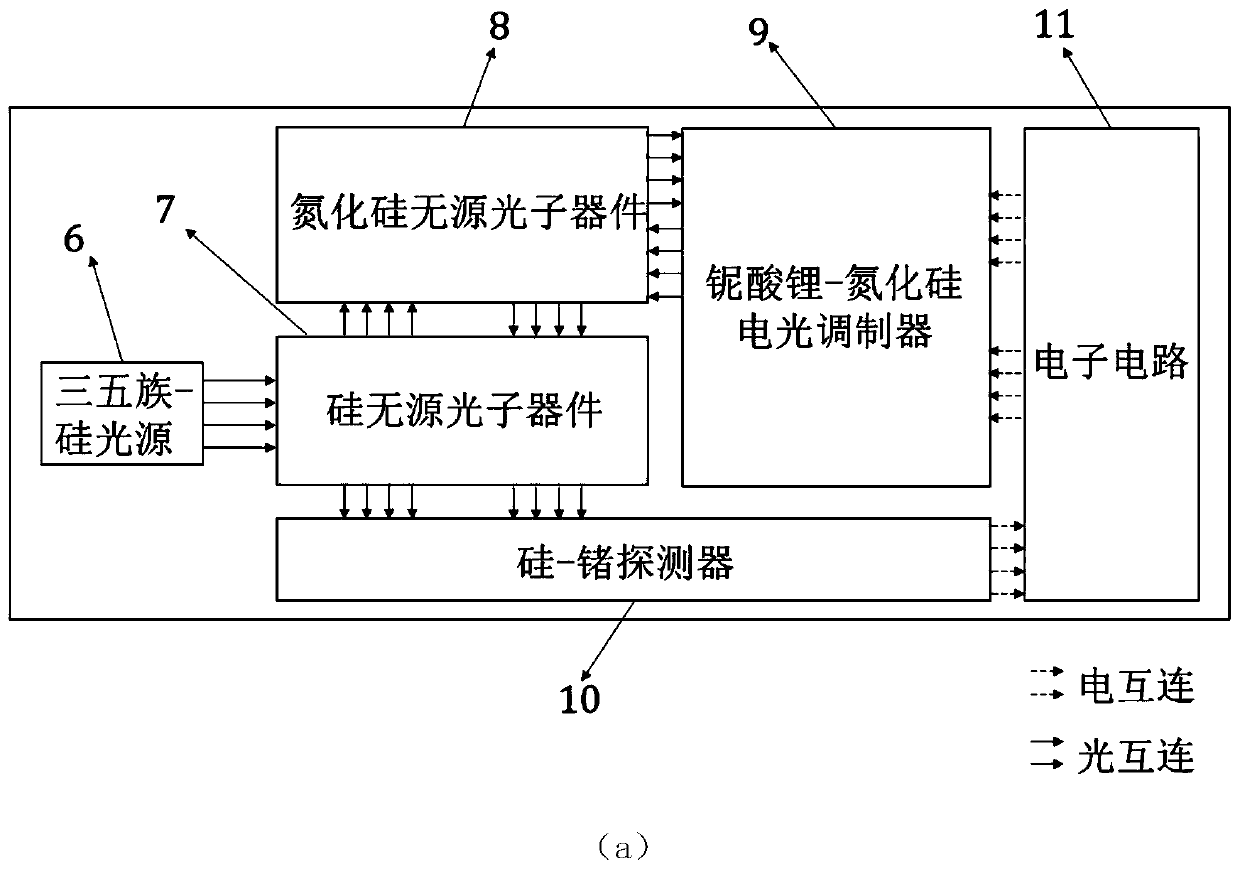

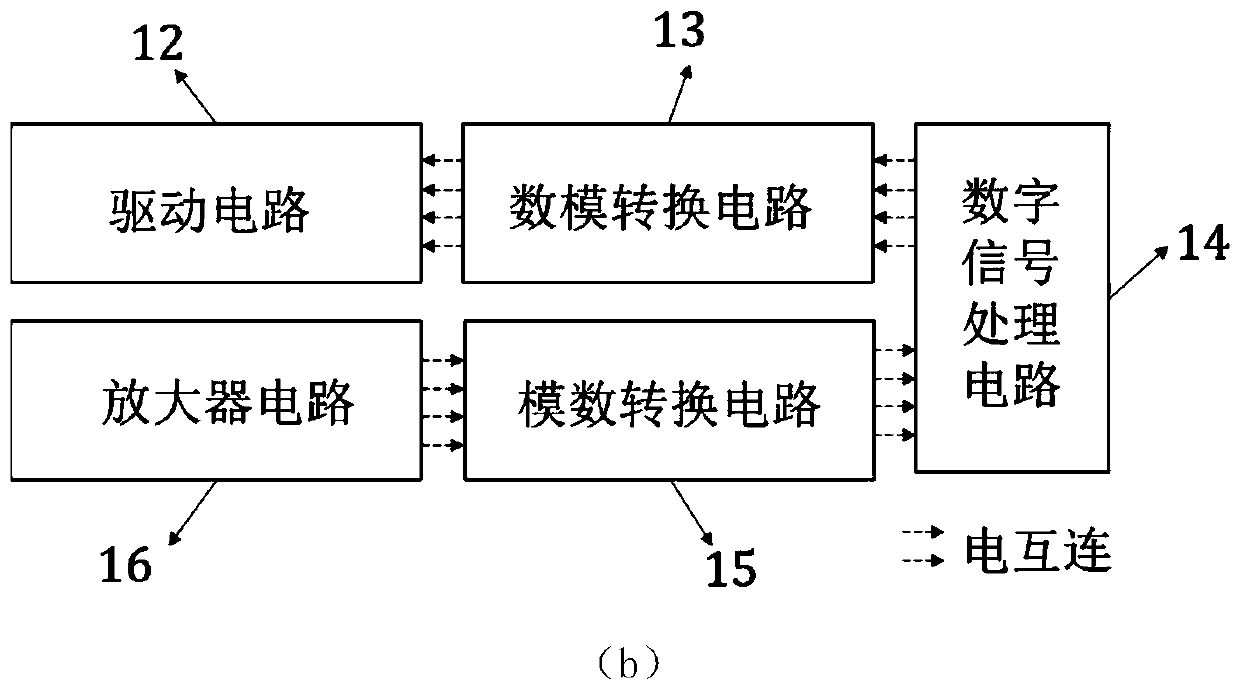

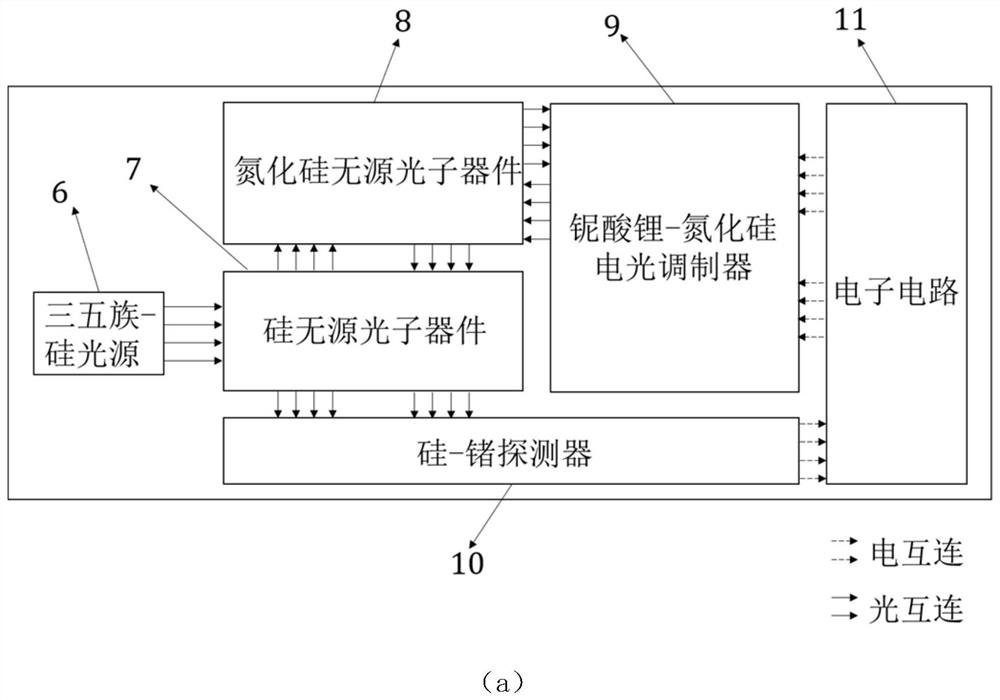

Photoelectric monolithic integration system based on multi-material system

ActiveCN111474745ASmall sizeReduce adverse effectsCoupling light guidesOptical waveguide light guideHemt circuitsRefractive index

The invention provides a photoelectric monolithic integration system based on a multi-material system. According to the system, an indium phosphide-silicon laser, a silicon passive photonic device, asilicon nitride passive photonic device, a silicon nitride-lithium niobate electro-optical modulator, a germanium-silicon detector and an electronic circuit are integrated on the same substrate, so that the size of a photoelectric system is reduced, the electrical and optical interconnection distance is reduced, and the adverse effect of parasitic parameters on the integrated system is greatly reduced. The packaging between the optical path module and the circuit module is avoided, and the packaging cost is reduced. The advantages of excellent electro-optical performance of the lithium niobatematerial, low loss, low polarization sensitivity and high process tolerance of the silicon nitride material and high refractive index of the silicon material are exerted, and a monolithic photoelectric integrated system with excellent performance is realized.

Owner:SHANGHAI JIAO TONG UNIV

Semiconductor package and manufacturing method thereof

ActiveUS11088100B2Improve electrical performanceGood workmanshipSemiconductor/solid-state device detailsSolid-state devicesRedistribution layerSemiconductor package

A semiconductor package and a manufacturing method thereof are provided. The semiconductor package includes a first and a second active dies separately arranged, an insulating encapsulation at least laterally encapsulating the first and the second active dies, a redistribution layer disposed on the insulating encapsulation, the first and the second active dies, and a fine-pitched die disposed on the redistribution layer and extending over a gap between the first and the second active dies. The fine-pitched die has a function different from the first and the second active dies. A die connector of the fine-pitched die is connected to a conductive feature of the first active die through a first conductive pathway of the redistribution layer. A first connecting length of the first conductive pathway is substantially equal to a shortest distance between the die connector of the fine-pitched die and the conductive feature of the first active die.

Owner:POWERTECH TECHNOLOGY

Multi-wafer bonding structure and bonding method

ActiveUS20200075550A1Short interconnection distanceHigh signal transmission rateSemiconductor/solid-state device detailsSolid-state devicesWaferingElectrical connection

A multi-wafer bonding structure and bonding method are disclosed. The multi-wafer bonding structure includes a first unit and a second unit, a metal layer of each wafer in the first unit electrically connected to an interconnection layer of the first unit, a first bonding layer in the first unit electrically connected to the interconnection layer of the first unit, a second bonding layer in the second unit electrically connected to a metal layer of the second unit, and the first bonding layer being in contact with the second bonding layer to achieve an electrical connection, thereby achieving the electrical connection among the interconnection layer of the first unit, the first bonding layer, the second bonding layer and the metal layer of each wafer.

Owner:WUHAN XINXIN SEMICON MFG CO LTD

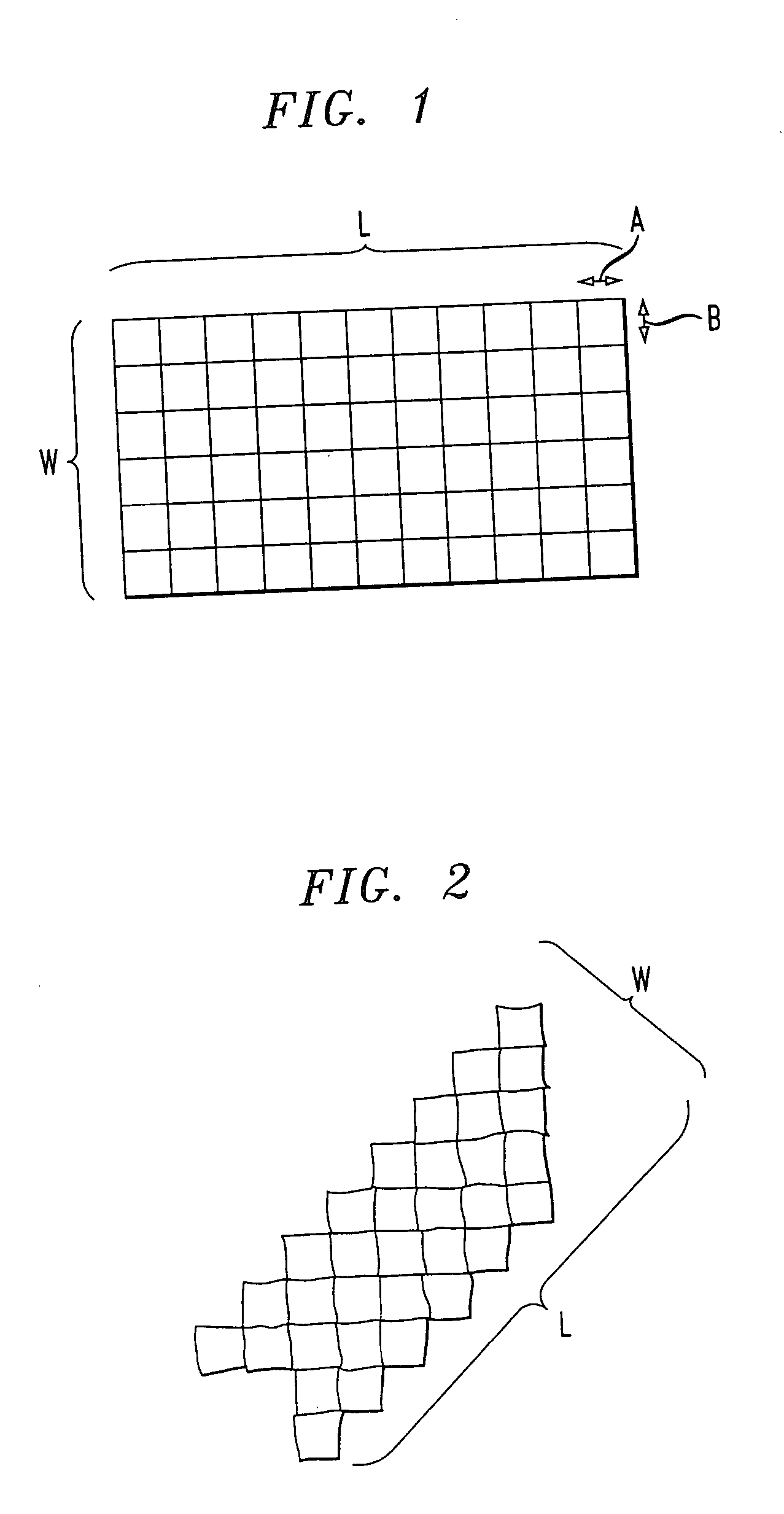

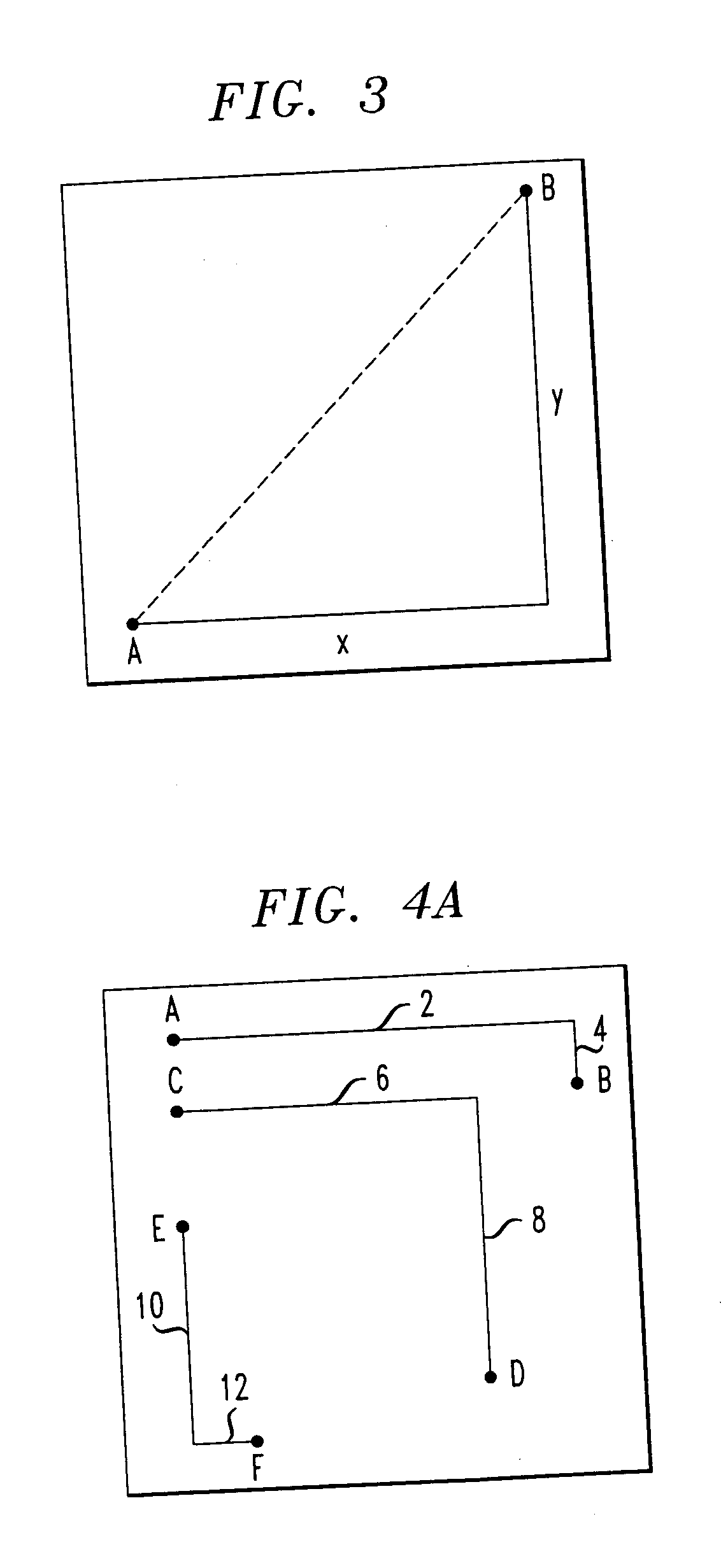

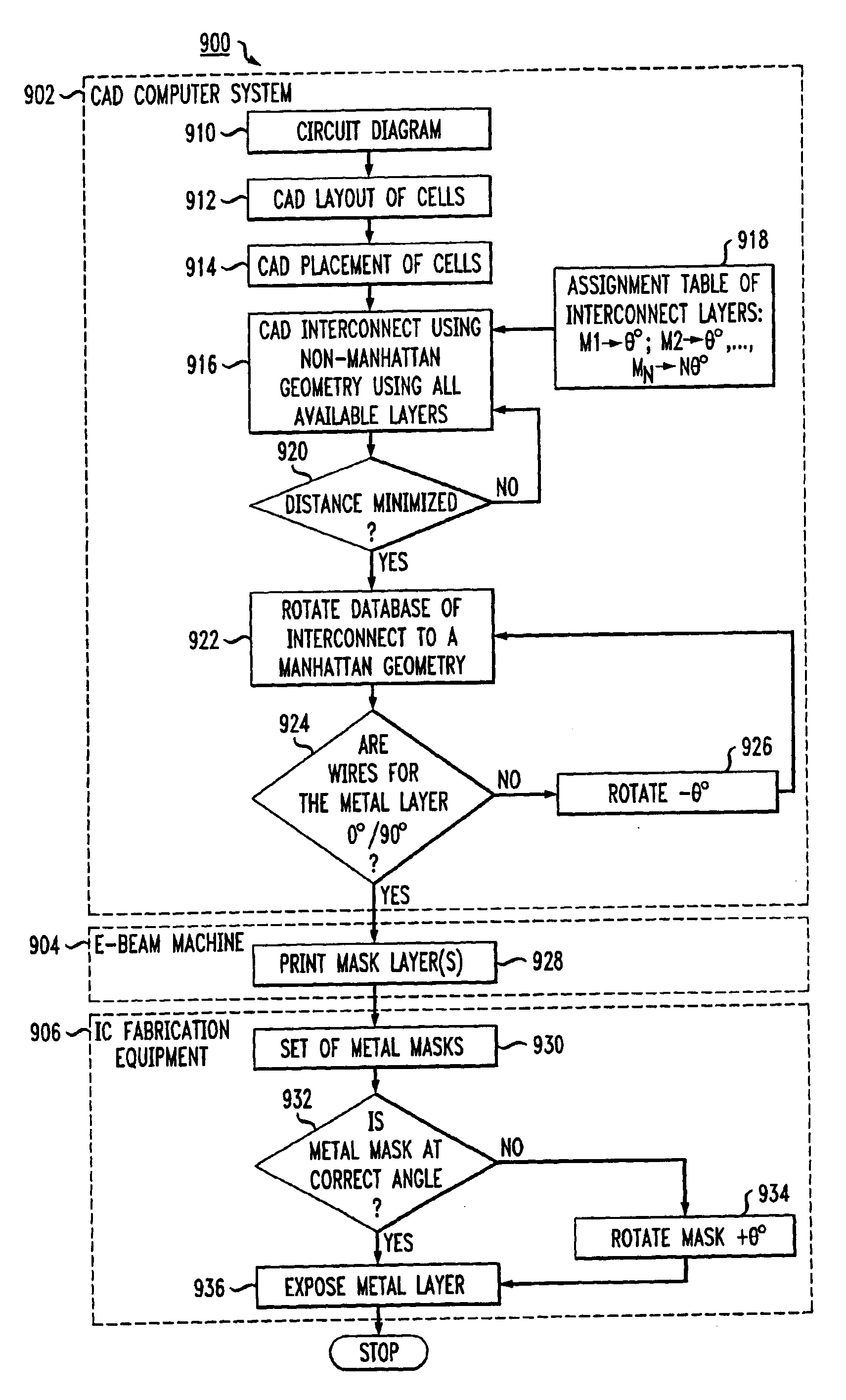

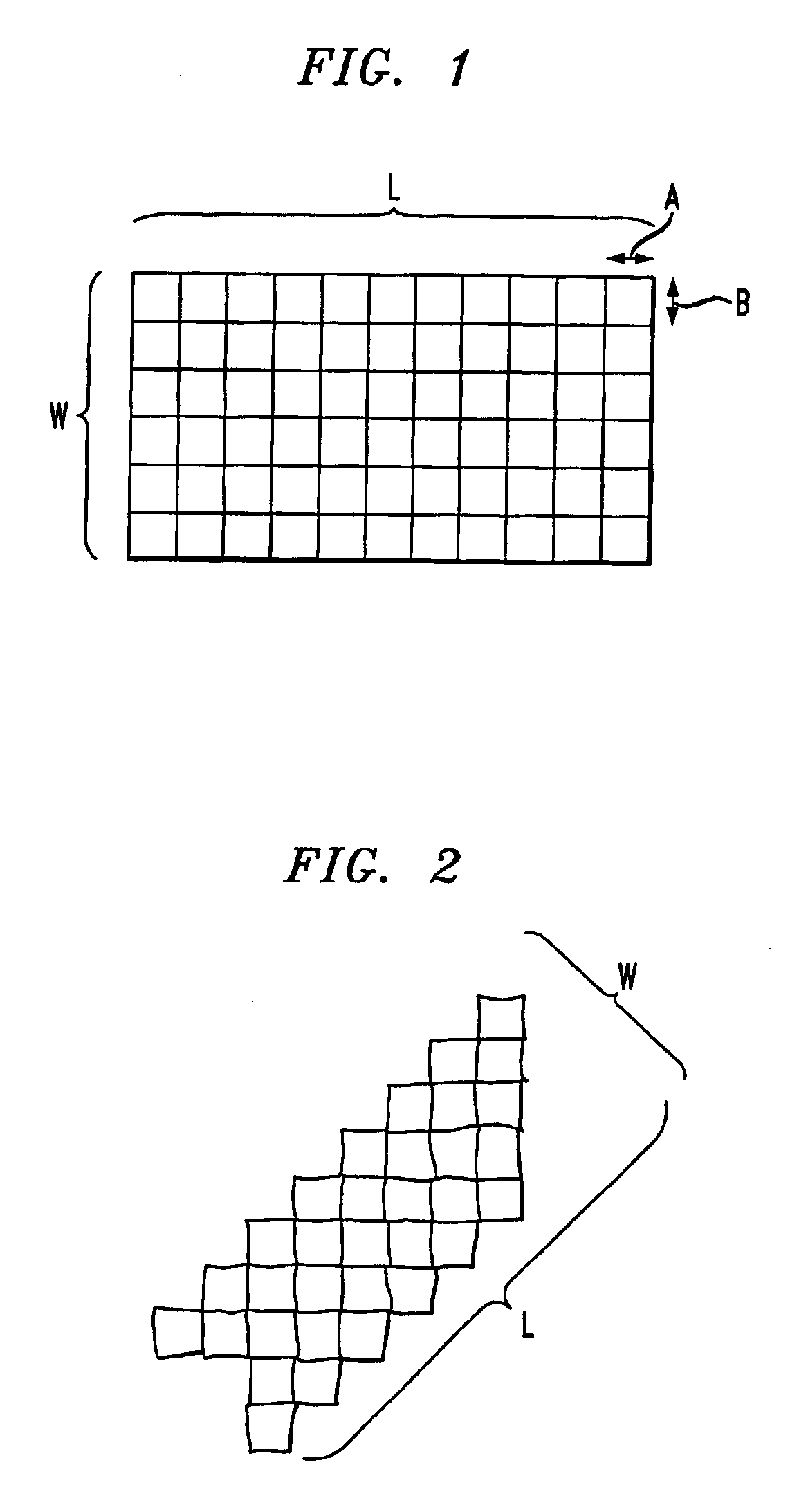

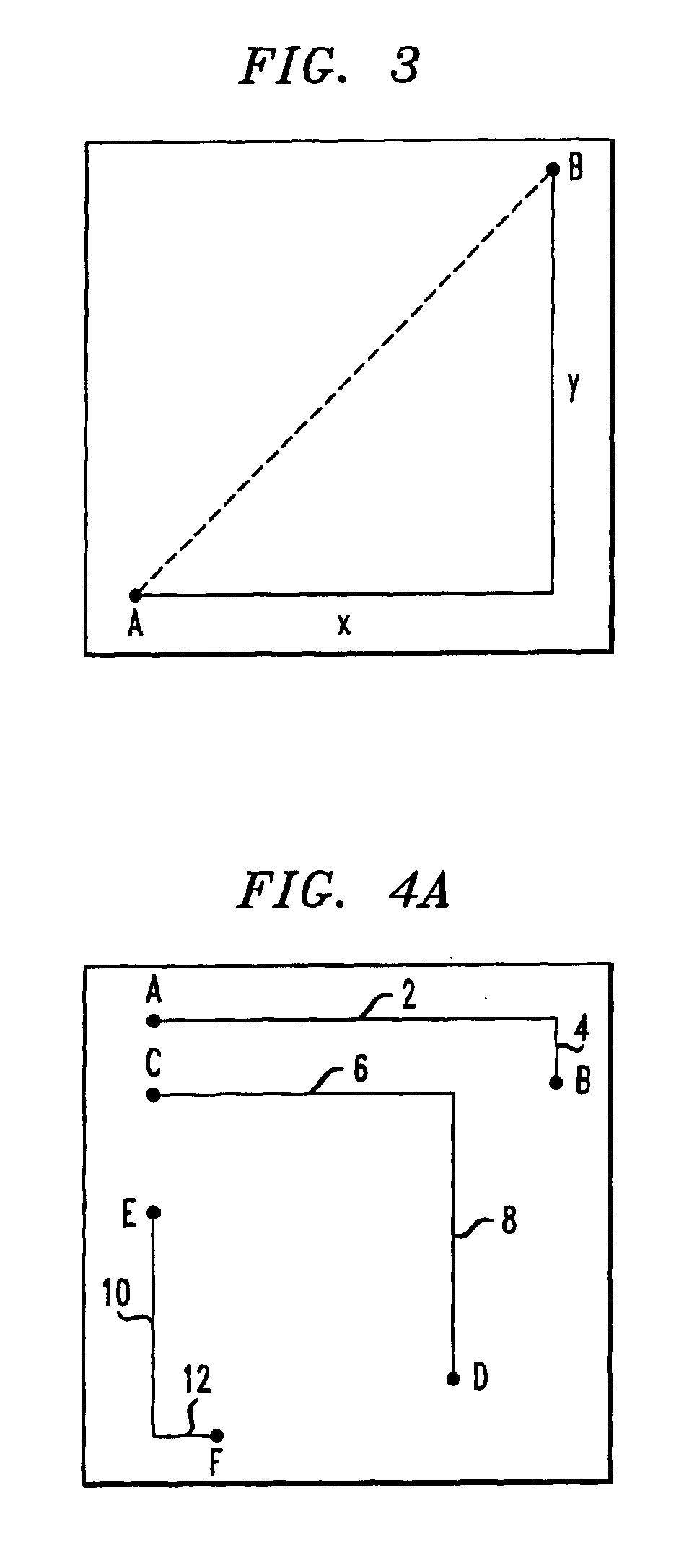

Variable rotational assignment of interconnect levels in integrated circuit fabrication

InactiveUS20050079654A1Saving on interconnect distanceShorten the interconnection distanceTransistorSemiconductor/solid-state device detailsCapacitanceAssignment methods

Integrated circuit fabrication techniques are provided which allow non-horizontal / non-vertical wires to traverse the entire chip surface, rather than just the comers as in the conventional Manhattan geometry, while interconnecting circuit points. This is achieved by employing a variable rotational assignment methodology with respect to the interconnect layers or levels during the IC fabrication operation. These techniques thus eliminate the litho step problem, reduce interconnect distances and lessen the influence of capacitance interaction between interconnect wires.

Owner:LUCENT TECH INC

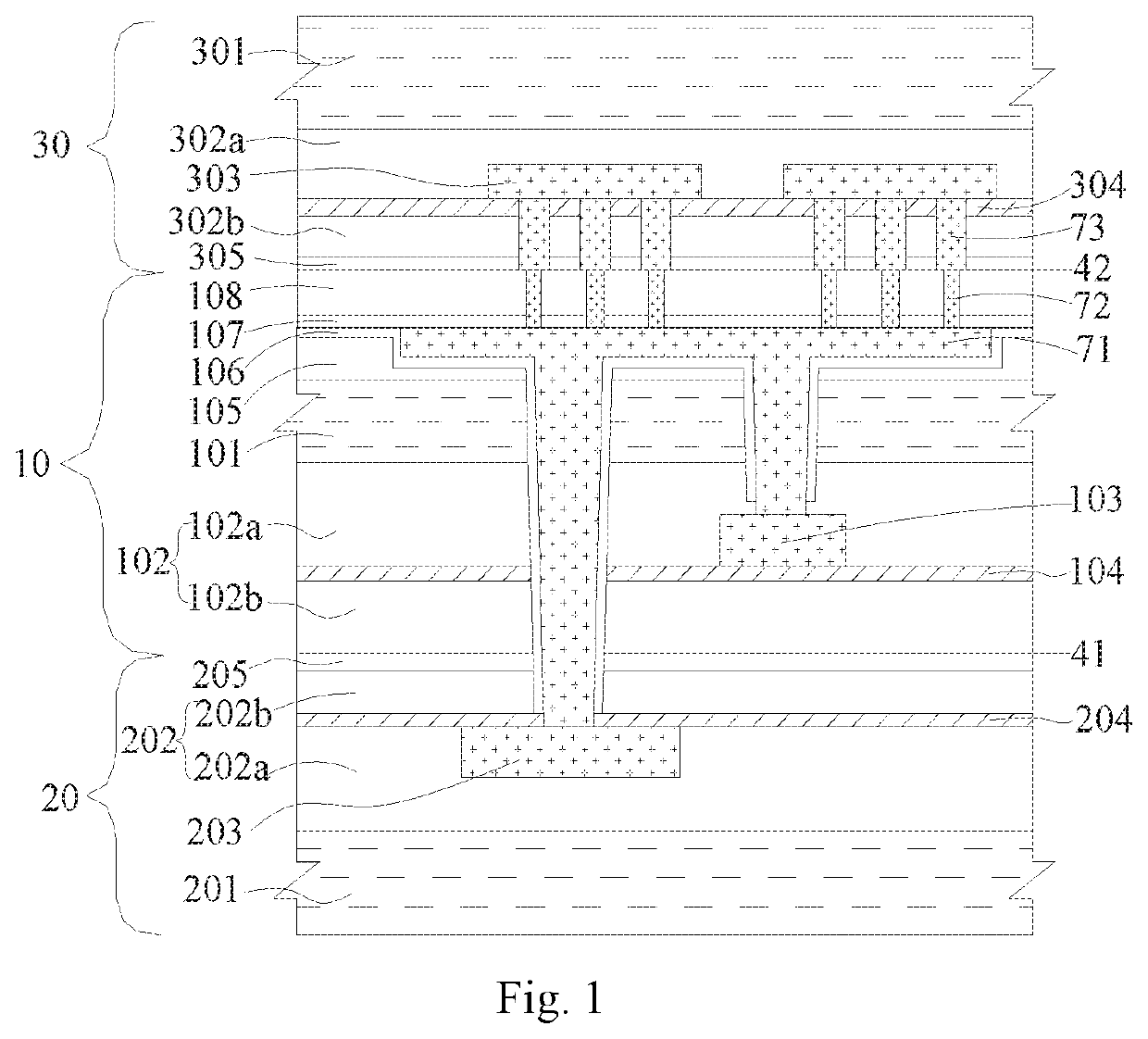

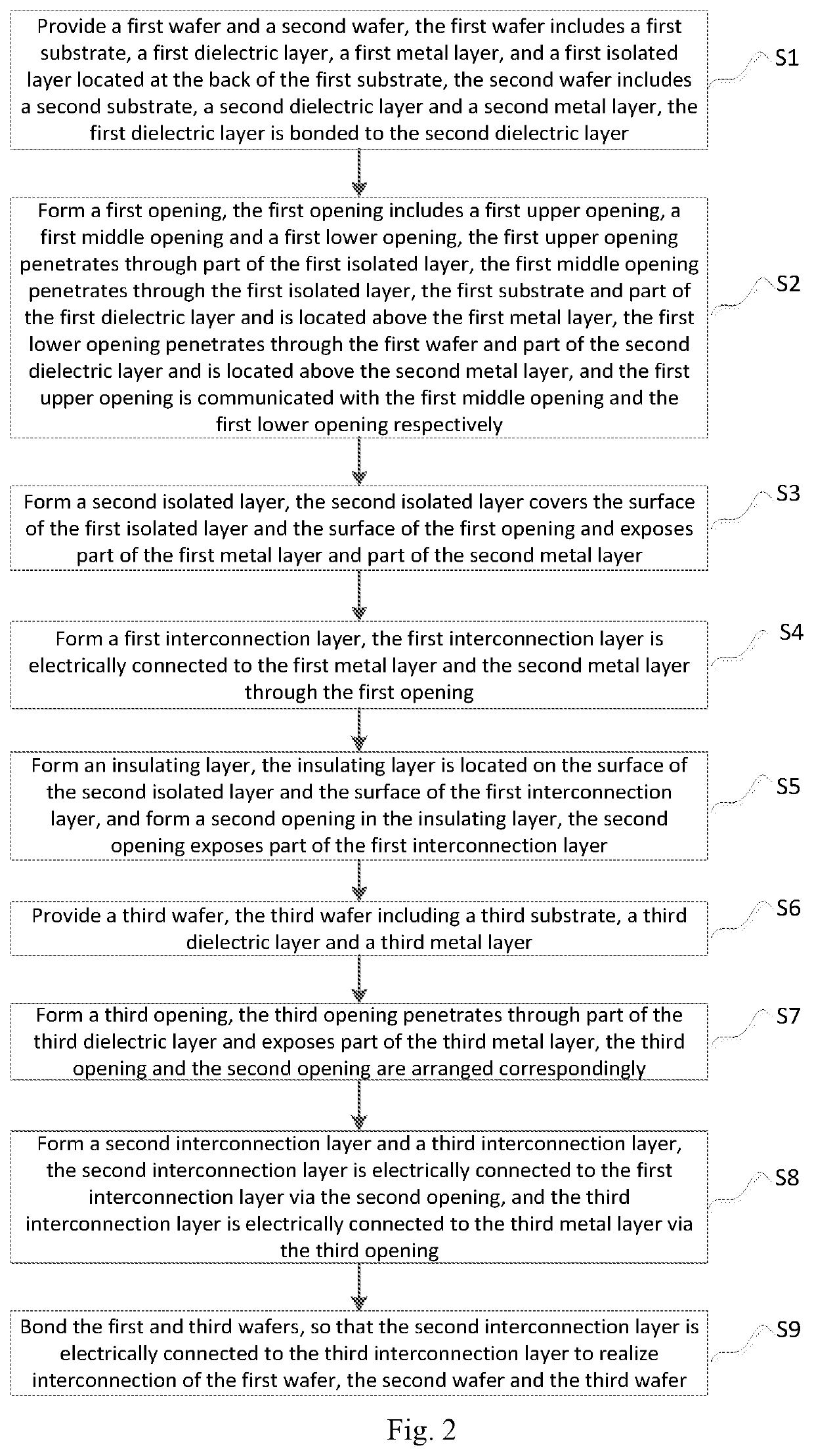

Multi-wafer stack structure and forming method thereof

ActiveUS20200075552A1Reduce thicknessIncrease transfer speedSemiconductor/solid-state device detailsSolid-state devicesWaferingWafer stacking

A multi-wafer stack structure and fabricating method thereof are disclosed. In the multi-wafer stack structure, the first interconnection layer is electrically connected to the second metal layer and the first metal layer via the first opening, the second interconnection layer is electrically connected to the first interconnection layer via the second openings, the third interconnection layer is electrically connected to the third metal layer via the third openings, and the second interconnection layer is in contact with the third interconnection layer, so that there is no need to reserve the wire pressure welding space between the wafers and a silicon substrate is eliminated, the overall device thickness of the multi-wafer stack package is reduced. Moreover, the design processing of the silicon substrate and a plurality of common pads on the silicon substrate is eliminated, thereby reducing the parasitic capacitance and power loss, and increasing the transmission speed.

Owner:WUHAN XINXIN SEMICON MFG CO LTD

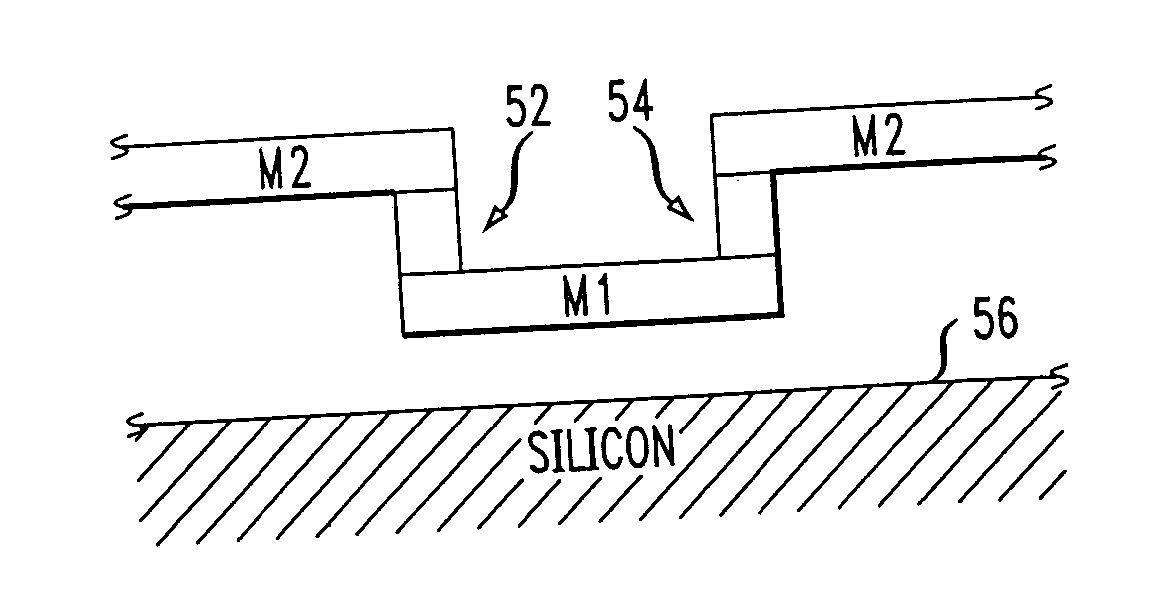

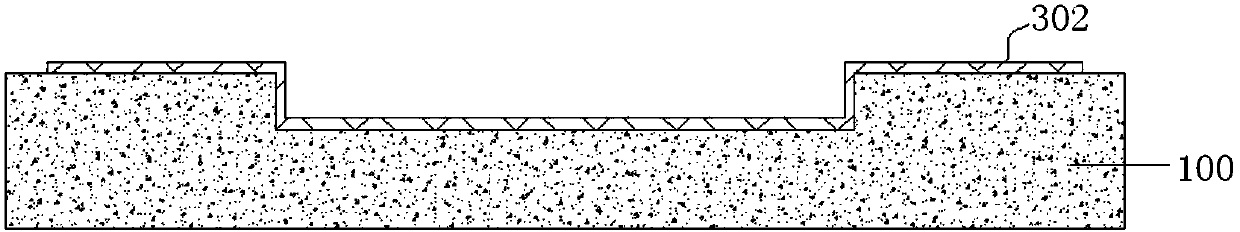

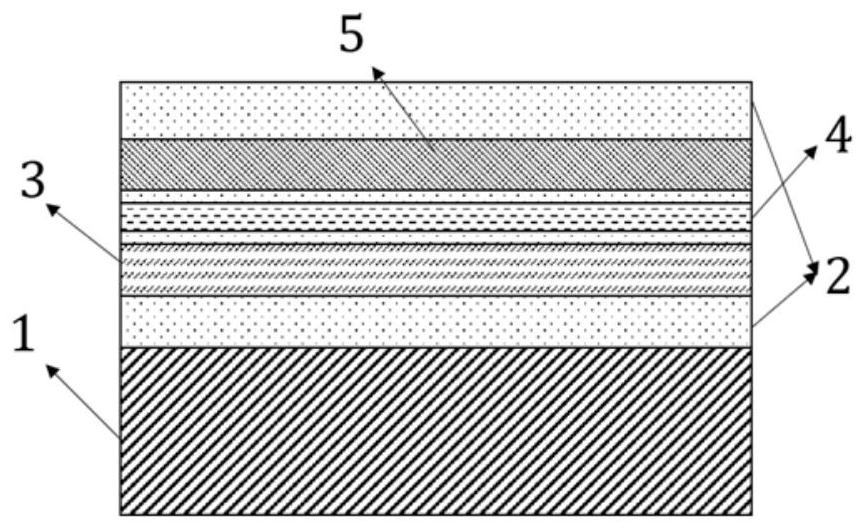

Mosfet packaging structure and its manufacturing method

ActiveCN105870098BImprove conductivityShorten the interconnection distanceSemiconductor/solid-state device detailsSolid-state devicesMOSFETPower flow

The invention discloses a MOSFET packaging structure and a manufacturing method thereof. The packaging structure includes a silicon substrate and a MOSFET chip. The front side of the MOSFET chip includes a source conductive pad and a gate conductive pad, and the back side includes a drain region and a metal layer. There is a sinking groove on the surface of the substrate, and the bottom of the sinking groove is laid with a conductive layer extending to the surface of the substrate as a drain conductive pad. The back of the MOSFET chip is mounted on the bottom of the sinking groove, and the metal layer and the sinking groove The conductive layer at the bottom is connected by metal bonding, the conductors interconnected with the outside are formed on the source conductive pad, the gate conductive pad and the drain conductive pad, and the part other than the conductor on the front side of the silicon substrate is encapsulated by the protective layer. The present invention guides the drain current on the back of the MOSFET with a vertical structure to the front of the MOSFET, realizes that the source, gate, and drain are electrically on the same side for wafer-level packaging, and the large-area conductive layer ensures a good chip Heat dissipation effect; avoiding the TSV process through silicon vias, simplifying the process steps and reducing the packaging cost.

Owner:HUATIAN TECH KUNSHAN ELECTRONICS

Variable rotational assignment of interconnect levels in integrated circuit fabrication

InactiveUS6849937B2Fine granularitySaving on interconnect distanceTransistorSemiconductor/solid-state device detailsCapacitanceEngineering

Integrated circuit fabrication techniques are provided which allow non-horizontal / non-vertical wires to traverse the entire chip surface, rather than just the corners as in the conventional Manhattan geometry, while interconnecting circuit points. This is achieved by employing a variable rotational assignment methodology with respect to the interconnect layers or levels during the IC fabrication operation. These techniques thus eliminate the litho step problem, reduce interconnect distances and lessen the influence of capacitance interaction between interconnect wires.

Owner:LUCENT TECH INC

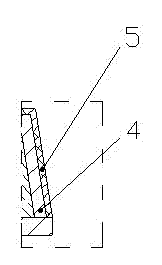

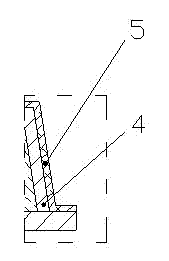

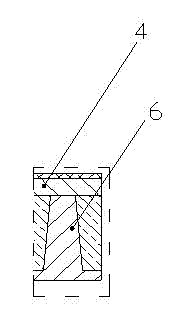

Groove-interconnected wafer level MOSFET encapsulation structure and implementation method

ActiveCN102122670BImprove current carrying capacityImprove cooling effectSemiconductor/solid-state device detailsSolid-state devicesMOSFETEngineering

The invention relates to a groove-interconnected wafer level metal-oxide-semiconductor field effect transistor (MOSFET) encapsulation structure and an implementation method. The structure comprises a chip body (1-1); a chip source electrode (2-1) and a chip gate electrode (2-2) are arranged on the front surface of the chip body; chip surface protection layers (3) are arranged on the front surfaces of the chip source electrode and the chip gate electrode of the chip body; chip grooves (1-2) pass through the front surface and the back surface of the chip body; circuit layers (4) are arranged onthe surface of the chip source electrode, the surface of the chip gate electrode and the surfaces of the chip surface protection layers (3) and in the chip grooves (1-2); a circuit surface protectionlayer (5) is arranged on the surface of the circuit layer; welded balls (6) are arranged on the surfaces of the circuit layers (4) on the front surface of the chip body (1-1); a back surface metal layer (7) is arranged on the back surface (1-3) of the chip body (1-1); and the back surface metal layer (7) is interconnected with the circuit layers (4). The encapsulation structure with high performance, and a process method which is used for implementing the structure and has high production efficiency and is low in encapsulation cost are provided.

Owner:JIANGYIN CHANGDIAN ADVANCED PACKAGING CO LTD

Three-dimensional integrated chip

PendingCN113793844AShorten the interconnection distanceReduce power consumptionSolid-state devicesArchitecture with single central processing unitComputer hardwareComputer architecture

The invention provides a three-dimensional integrated chip. The chip comprises: a first programmable array assembly which comprises a first bonding region; a first storage array assembly which comprises a second bonding region; and a second storage array assembly which comprises a third bonding region. The first bonding region is in bonding connection with the second bonding region, and the second bonding region is in bonding connection with the third bonding region, so that the first programmable array assembly, the first storage array assembly and the second storage array assembly are bonded. Therefore, the storage space of the first programmable array assembly is expanded, the first programmable array assembly, the first storage array assembly and the second storage array assembly are bonded through the three-dimensional bonding technology, the interconnection distance is reduced, high bandwidth and low power consumption of storage access are achieved, and the storage wall problem existing in the prior art is solved.

Owner:XI AN UNIIC SEMICON CO LTD

A Photoelectric Monolithic Integrated System Based on Multi-material System

ActiveCN111474745BSmall sizeReduce adverse effectsCoupling light guidesOptical waveguide light guideRefractive indexHemt circuits

The invention provides a photoelectric monolithic integrated system based on a multi-material system, the system includes an indium phosphide-silicon laser, a silicon passive photonic device, a silicon nitride passive photonic device, and a silicon nitride-lithium niobate electro-optic modulator The germanium-silicon detector and the electronic circuit are integrated on the same substrate, which is used to reduce the size of the optoelectronic system, reduce the electrical and optical interconnection distance, thereby greatly reducing the adverse effects of parasitic parameters on the integrated system; avoiding the optical path The packaging between the module and the circuit module reduces the packaging cost. Take advantage of the excellent electro-optical performance of lithium niobate material, low loss, low polarization sensitivity, high process tolerance and high refractive index of silicon nitride material to realize a monolithic optoelectronic integrated system with excellent performance.

Owner:SHANGHAI JIAOTONG UNIV

Multi-wafer stacking structure and fabrication method thereof

ActiveUS10700042B2Reduce thicknessIncrease transfer speedSemiconductor/solid-state device detailsSolid-state devicesWaferingWafer stacking

Owner:WUHAN XINXIN SEMICON MFG CO LTD

a light emitter

ActiveCN110311735BReduce demandImproving Impedance Matching PerformanceElectromagnetic transmittersImpedance matchingLight signal

Owner:SHANGHAI JIAOTONG UNIV

Multi-wafer stacking structure and fabrication method thereof

ActiveUS20200286861A1Reduce thicknessIncrease transfer speedSemiconductor/solid-state device detailsSolid-state devicesWaferingWafer stacking

A multi-wafer stacking structure is disclosed. In which a first interconnection layer is electrically connected to a second metal layer and a first metal layer via a first opening, a second interconnection layer is electrically connected to the first interconnection layer via a second opening, a third interconnection layer is electrically connected to a third metal layer via a third opening, and the second interconnection layer is electrically connected to the third interconnection layer. It is unnecessary to reserve a bonding lead space between wafers, a silicon substrate is eliminated, and the multi-wafer stacking thickness is reduced while multi-wafer interconnection is realized, so that the overall device thickness is reduced after multi-wafer stacked package. Moreover, there is no need of leads, so as to eliminate design processing of a silicon substrate and a plurality of shared bonding pads on the silicon substrate.

Owner:WUHAN XINXIN SEMICON MFG CO LTD

Rear through-hole interconnected wafer level MOSFET (metal oxide semiconductor field effect transistor) packaging structure and implementation method

ActiveCN102122671BImprove current carrying capacityImprove cooling effectSemiconductor/solid-state device detailsSolid-state devicesMOSFETSolder ball

The invention relates to a rear through-hole interconnected wafer level MOSFET (metal oxide semiconductor field effect transistor) packaging structure and an implementation method. A chip source electrode (2-1) and a chip gate electrode (2-2) are arranged on the front surface of a chip body (1-1); chip surface protecting layers (3) are arranged on the front surfaces of the chip body, the chip source electrode and the chip gate electrode; front surface circuit layers (4) are arranged on the surfaces of the chip body, the chip source electrode, the chip gate electrode and the chip surface protecting layers; circuit surface protecting layers (5) are arranged on the surfaces of the front surface circuit layers and the chip surface protecting layers; solder balls (7) are arranged on the surfaces of the front surface circuit layers; a chip through hole (1-2) is arranged by penetrating the front surface and the back surface of the chip body; and a circuit layer (6) is arranged on the back surface of the chip body, the circuit layer (6) is filled in the chip through hole, and the circuit layer filled in the chip through hole is in direct contact with the side wall of the chip through holeand interconnected with the front surface circuit layers. According to the invention, the packaging structure has high performance; and the process method which is used for implementing the structureand has the advantages of high production efficiency and low packaging cost.

Owner:JIANGYIN CHANGDIAN ADVANCED PACKAGING CO LTD

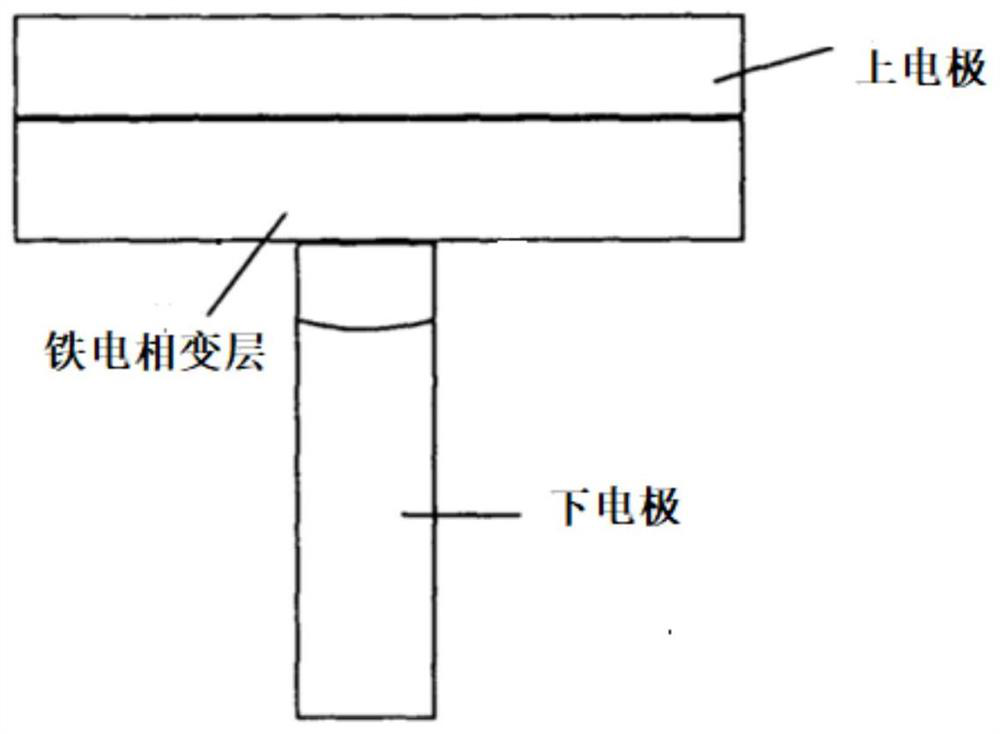

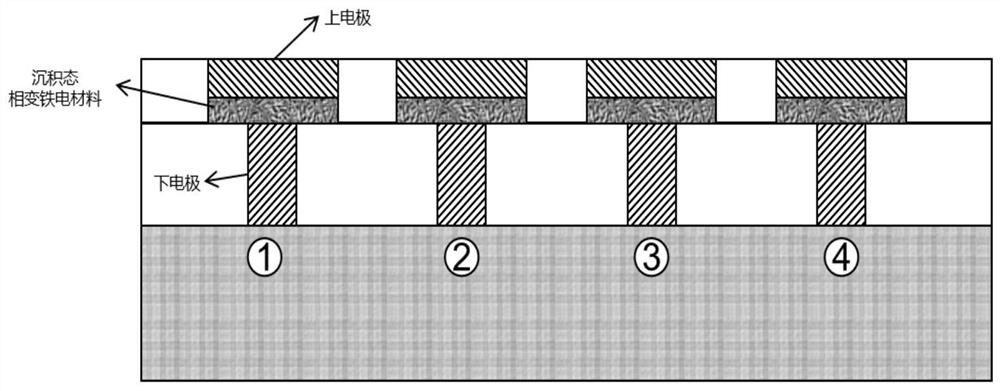

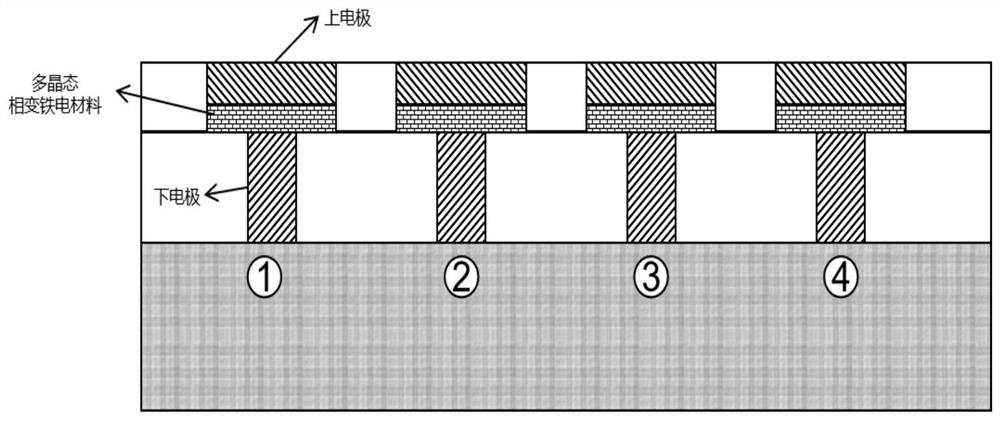

A kind of ferroelectric phase change hybrid memory unit, memory and operation method

ActiveCN110544742BSimplify interconnectionFast communication speedSolid-state devicesDigital storageMemory cellEngineering

The invention relates to a ferroelectric phase transition hybrid memory unit, memory and operation method. The ferroelectric phase change hybrid storage unit includes: a lower electrode, a functional layer and an upper electrode arranged in sequence; the lower electrode is a low work function electrode, and the upper electrode is a high work function electrode; the functional layer is a ferroelectric phase change material. By adopting the above structure, the ferroelectric phase-change hybrid storage unit can selectively work in the ferroelectric storage state or the phase-change storage state.

Owner:HUAZHONG UNIV OF SCI & TECH

Bipolar integrated circuit chip based on groove dielectric isolation

ActiveCN108336044AImprove conductivityImprove thermal conductivitySemiconductor/solid-state device detailsSolid-state devicesHeat conductingInterconnection

The invention discloses a bipolar integrated circuit chip based on groove dielectric isolation. The bipolar integrated circuit chip comprises a barrier layer, a first copper sheet, a plastic body, a concave groove, a fixed hole, a fixed base plate, a LOGO mark, a second copper sheet, a line surface protection layer, a pad, a chip source electrode, a chip gate electrode, a chip surface protection layer, a line layer, a metal line, an integrated circuit chip, a metal layer, a chip body and a chip groove. The bipolar integrated circuit chip has the beneficial effects that a form drain is led to the front side of the chip body through the line layer in the chip groove, thereby realizing interconnection between the front side of the chip body and the outside through the pad, shortening the interconnection distance between the chip body and the outside, and enhancing the current conducting and heat conducting effects of the chip. The bipolar integrated circuit chip has the characteristics ofhigh production efficiency and low package cost.

Owner:SHANXI YUXIANG INFORMATION TECH CO LTD

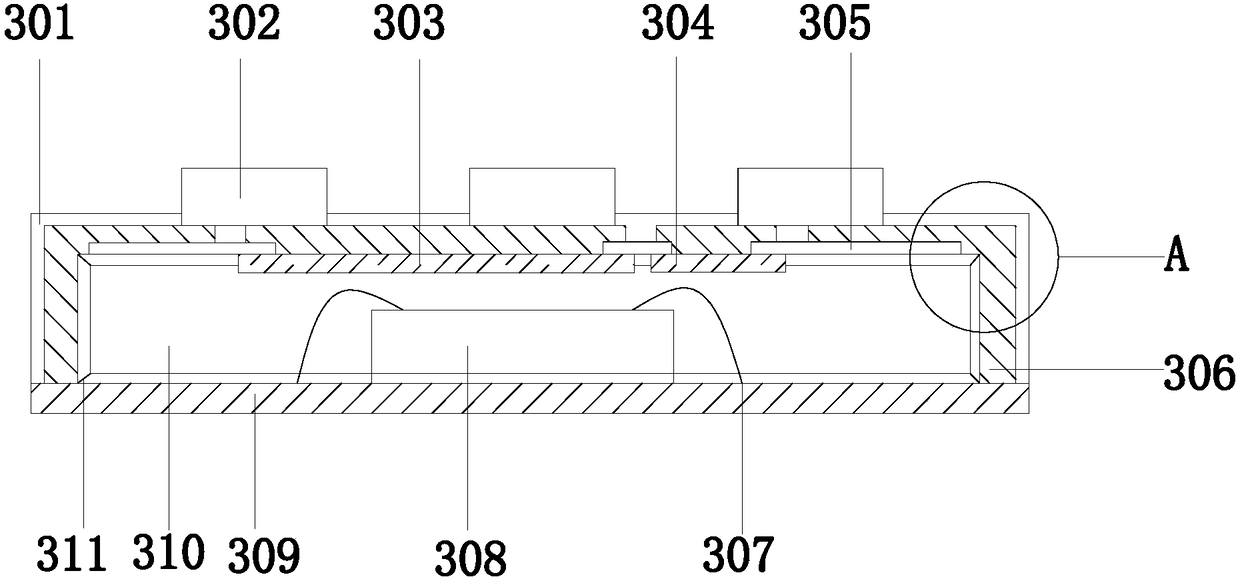

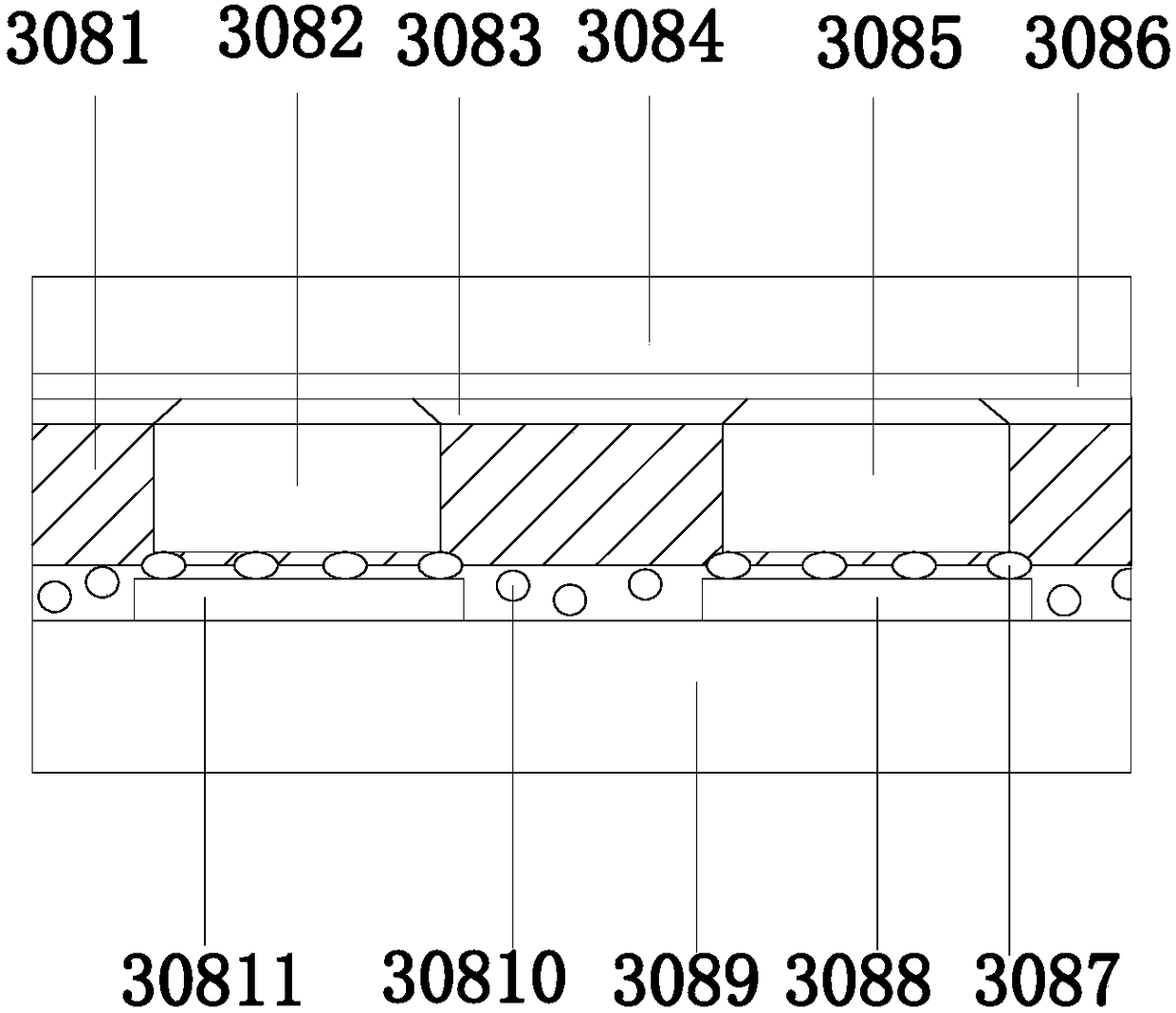

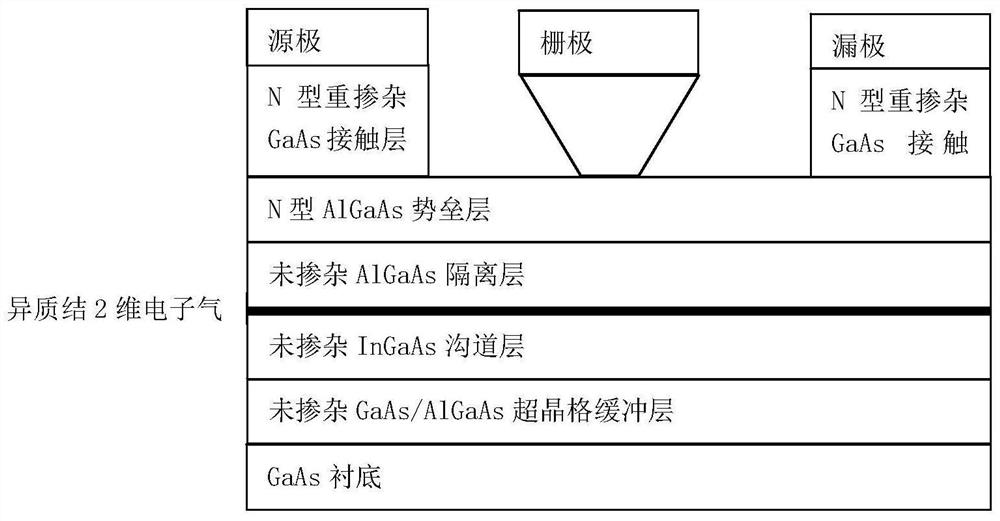

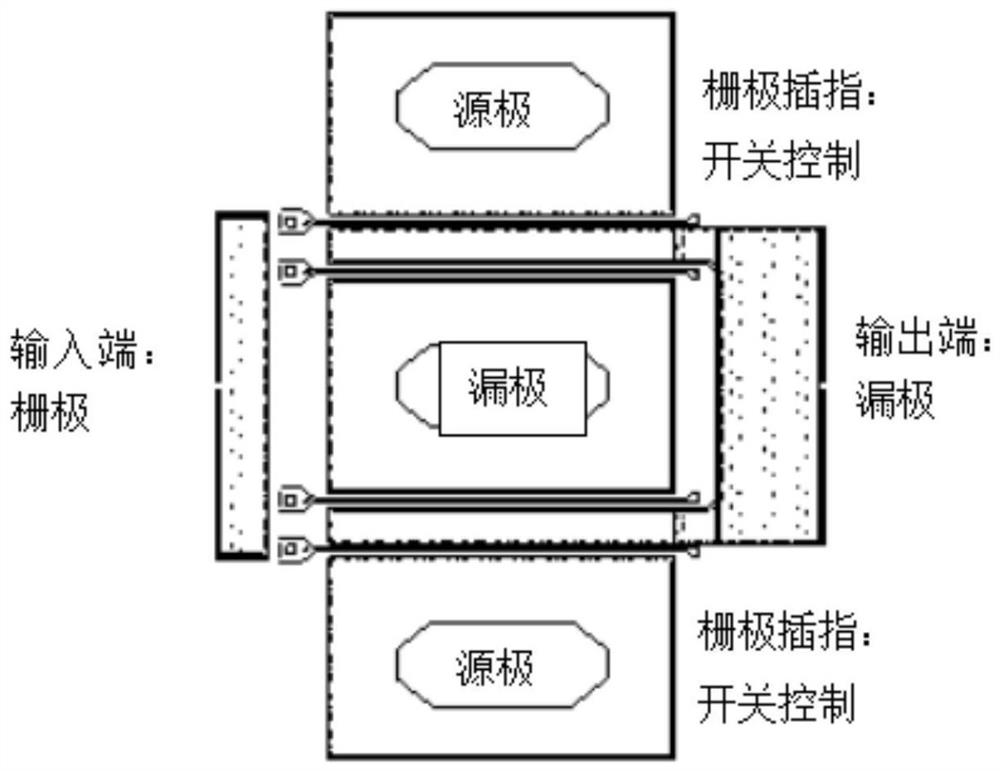

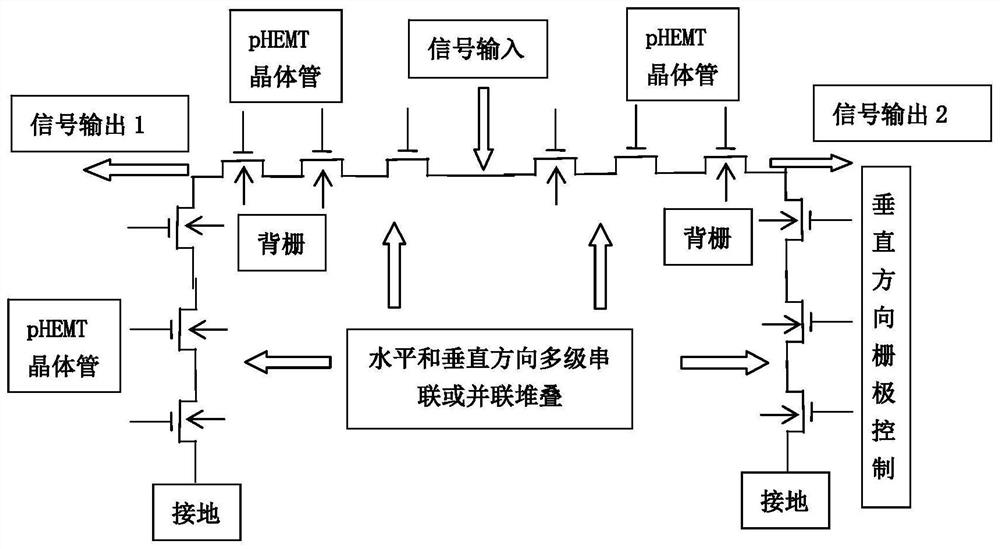

Vertical pHEMT transistor structure and switch chip

ActiveCN112420826AImprove isolationStrong barrier control abilitySemiconductor/solid-state device detailsSolid-state devicesIsolation layerBroadbanding

The invention discloses a vertical pHEMT transistor structure and a switch chip. The transistor comprises a buffer layer, a channel layer, a first isolation layer and a barrier layer which are sequentially arranged around a metallized through hole from the inner layer to the outer layer, the metallized through hole, the buffer layer, the channel layer, the first isolation layer and the barrier layer are each of a columnar structure, the axial direction of the metallized through hole is the same as the normal direction of a substrate, a source electrode, a grid electrode and a drain electrode are arranged on the barrier layer, the source electrode, the grid electrode and the drain electrode are horizontally or vertically arranged, and the grid electrode surrounds the columnar side wall fora circle during vertical arrangement. The switch chip is formed by connecting a plurality of vertical pHEMT transistors in series or in parallel in the vertical direction. The transistor and the switch chip provided by the invention have the characteristics of high isolation, large power capacity, small size, good integration, low power consumption, high efficiency and good broadband characteristic.

Owner:成都挚信电子技术有限责任公司

Three-dimensional stack interconnection structure and preparation method of SIC devices based on nano-silver solder paste

ActiveCN108550566BImprove thermal conductivityImprove insulation performanceMaterial nanotechnologySemiconductor/solid-state device detailsSolder pasteSilver Nano

The invention provides a three-dimensional stacked interconnection structure for a SiC device based on nano-silver soldering paste, and a preparation method. The interconnection structure comprises the nano-silver soldering paste and a ceramic plate. The nano-silver soldering paste is disposed in through holes in the ceramic plate, and a conductive circuit is formed after sintering. Furthermore, the nano-silver soldering paste is sintered to achieve the stacked interconnection of chip electrodes. The ceramic plate serves as an insulating plate and an underlay layer, thereby increasing the distance between two chips, and avoiding the edge breakdown effect between the chips. The connection of the interconnection structure can achieve the longitudinal interconnection of a plurality of chips,and the selected material comprises a ceramic substrate and a nano-silver soldering paste. The main component of the sinter nano-silver soldering paste is silver, and the conductivity and temperatureresistance of the sintered nano-silver soldering paste are close to the conductivity and temperature resistance of pure silver. The nano-silver soldering paste and the ceramic substrate are both madeof high temperature resistant materials, and can be used for the interconnection of a big power chip. Compared with other parking modes, the structure is simple in structure, is high in operability, is wide in application range, and can achieve the simple and effective high-temperature and high-voltage stacked packaging.

Owner:INST OF ELECTRONICS ENG CHINA ACAD OF ENG PHYSICS

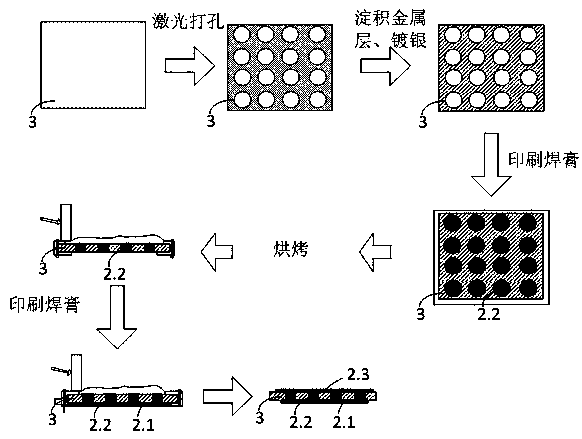

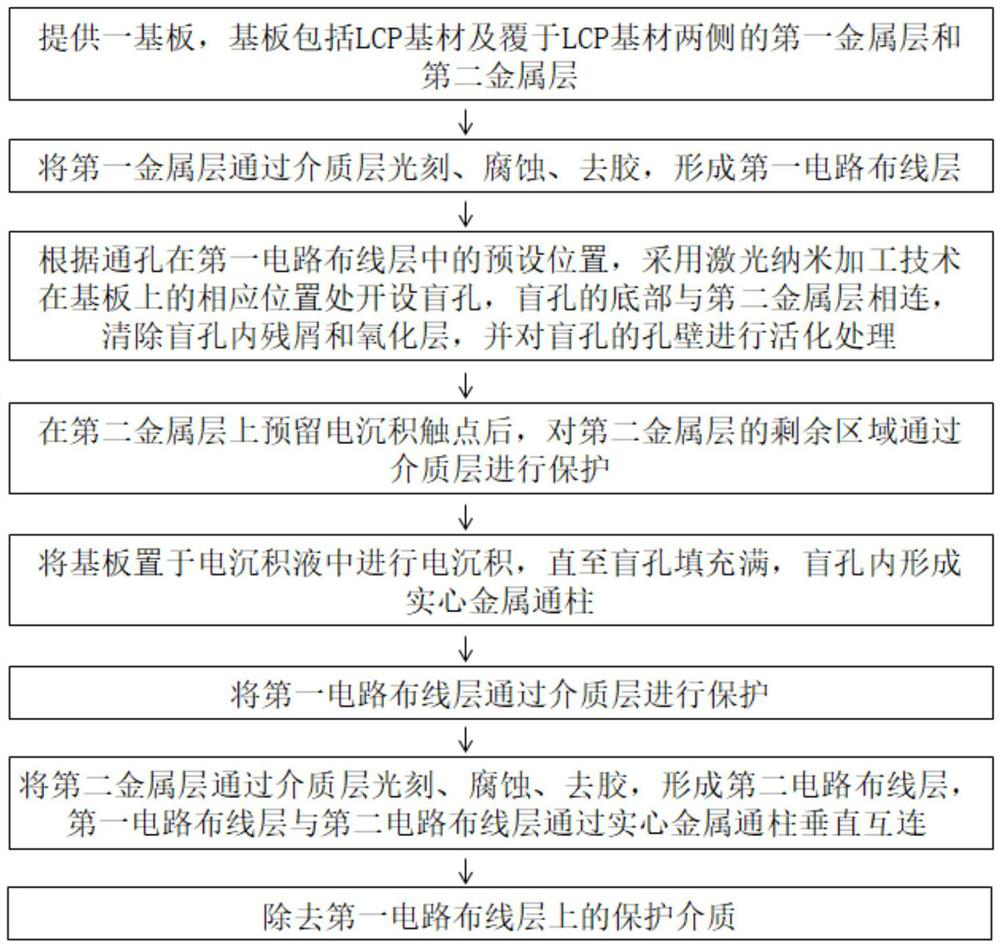

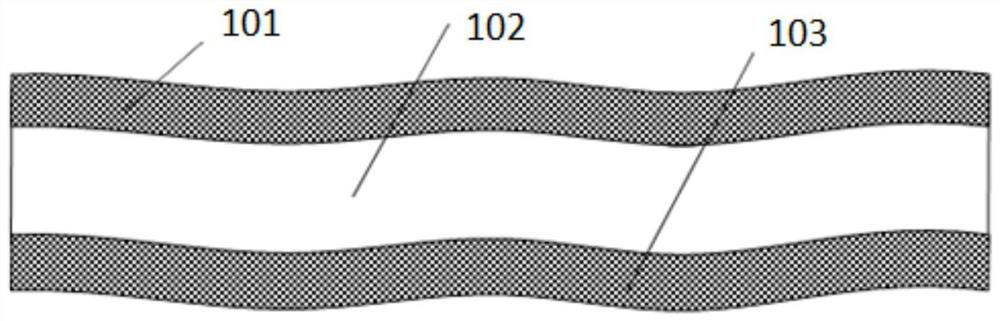

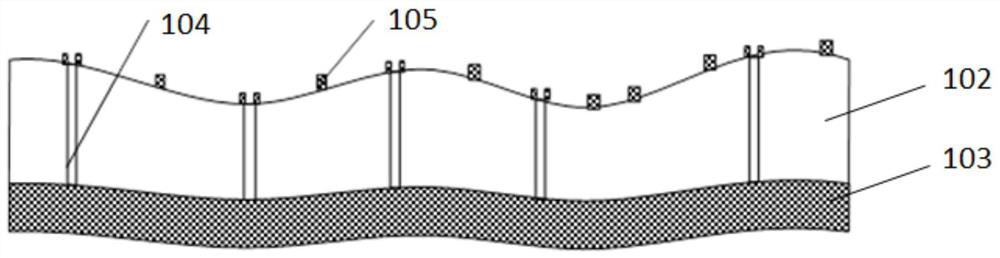

A vertical interconnect substrate based on laser nanoprocessing technology and its manufacturing method

ActiveCN111163582BHigh precisionHigh densityConductive pattern formationConductive material mechanical removalCapacitanceHemt circuits

The invention discloses a method for manufacturing vertically interconnected substrates based on laser nano-processing technology. Firstly, a first circuit wiring layer is formed on one side of the substrate through photolithography, corrosion, and glue removal of the dielectric layer, and then the laser nano-processing technology is used to form the first circuit wiring layer on one side of the substrate. Blind holes are opened at the corresponding positions on the substrate, and then the substrate is placed in the electrodeposition solution for electrodeposition to fill the blind holes, and finally the second circuit is formed on the other side of the substrate through photolithography, corrosion, and degumming of the dielectric layer Wiring layer, the manufacturing method has a simple process, high precision of laser nano-processing technology, no void inside the through hole, reliable interconnection, and improves the density and reliability of the three-dimensional packaging of the LCP flexible substrate. At the same time, the metallized through hole is used to realize the double The vertical interconnection between the surface circuit wiring layers can effectively shorten the interconnection distance, reduce signal delay, reduce parasitic inductance and capacitance, improve high-frequency characteristics, and thus improve system integration performance.

Owner:SHANGHAI SPACEFLIGHT ELECTRONICS & COMM EQUIP RES INST

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com