Three-dimensional stacked interconnection structure for SiC device based on nano-silver soldering paste, and preparation method

An interconnect structure, three-dimensional stacking technology, applied in semiconductor/solid-state device manufacturing, nanotechnology for materials and surface science, nanotechnology, etc. Parasitic inductance and resistance, etc., to alleviate the edge breakdown effect, shorten the interconnection distance, and increase the contact area.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] The technical solutions in the embodiments of the present invention will be clearly and completely described below in conjunction with the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some of the embodiments of the present invention, not all of them. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

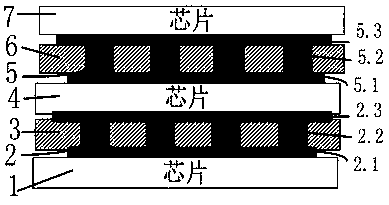

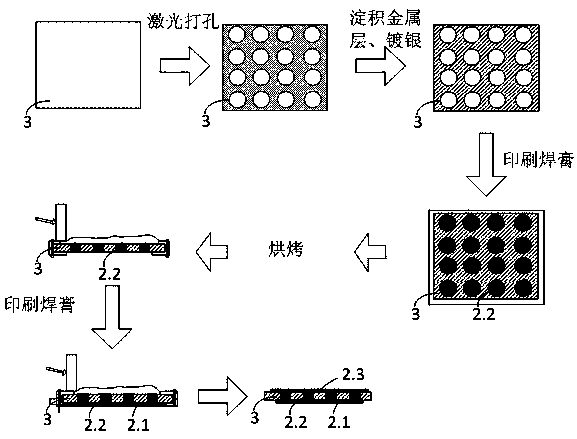

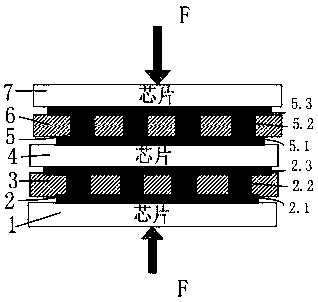

[0026] Embodiments of the present invention provide a three-dimensional stacked structure of SiC devices based on nano-silver solder paste such as figure 1 As shown, it includes: three silicon carbide power chips 1, 4, 7, all of which are vertical structure diodes; two-layer interconnection structures 2, 3, 5, 6. The interconnection structure is composed of ceramic substrates 3 and 6 with through holes and nano-silver solder paste 2 and 5. The diam...

PUM

| Property | Measurement | Unit |

|---|---|---|

| pore size | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More