Groove-interconnected wafer level MOSFET encapsulation structure and implementation method

A technology of packaging structure and implementation method, which is applied in electrical components, electrical solid devices, circuits, etc., to achieve the effects of low packaging cost, shortened interconnection distance, and improved current carrying capacity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

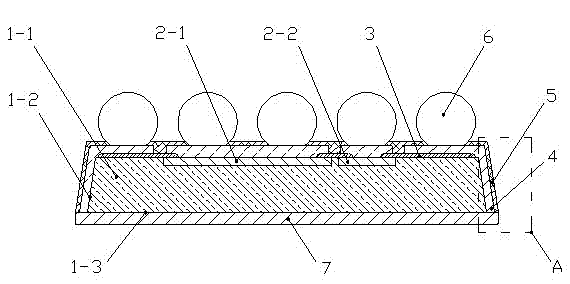

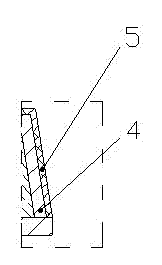

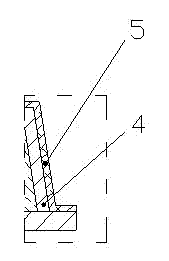

[0023] see figure 1 , figure 1 It is a cross-section schematic diagram of the packaging structure of the trench-interconnected wafer-level MOSFET of the present invention. Depend on figure 1 It can be seen that the trench interconnection wafer-level MOSFET packaging structure of the present invention includes a chip body 1-1, a chip trench 1-2, a chip source electrode 2-1, a chip gate electrode 2-2, and a chip surface protection layer 3 , circuit layer 4, circuit surface protective layer 5, solder ball 6 and back metal layer 7, the chip source electrode 2-1 and chip gate electrode 2-2 are arranged on the front of the chip body 1-1, and the chip surface protective layer 3 is arranged On the front of the chip body 1-1, the chip source electrode 2-1 and the chip gate electrode 2-2, the chip groove 1-2 runs through the front and back of the chip body 1-1, and the circuit layer 4 is arranged on the chip source electrode 2-1. The surface of the chip gate electrode 2-2 and the chi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com