Negative resistance clamping silicon controlled rectifier memory resistor device and manufacturing method thereof

A technology of memristive devices and silicon rectifiers, which is applied in the field of negative resistance clamped thyristor rectifier memristive devices and its production, can solve problems such as difficult integration of memristive devices, achieve good robustness, realize nonlinear characteristics, The effect of the simple production method

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] The present invention will be described in further detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

[0029]Unless otherwise defined, all technical and scientific terms used herein have the same meaning as commonly understood by one of ordinary skill in the technical field of the invention. The terms used herein in the description of the present invention are for the purpose of describing specific embodiments only, and are not intended to limit the present invention. As used herein, the term "and / or" includes any and all combinations of one or more of the associated listed items.

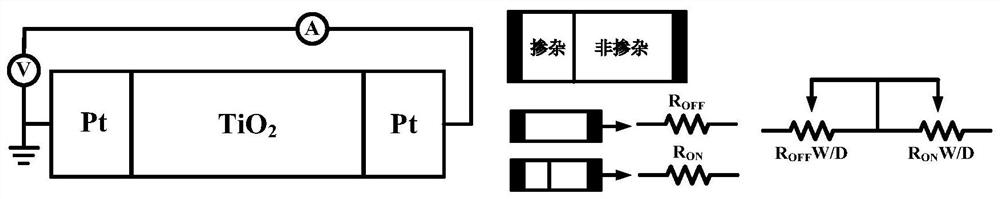

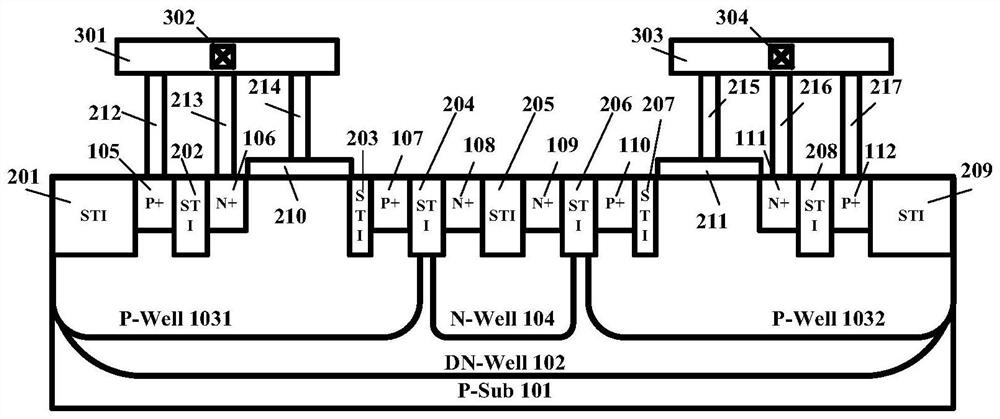

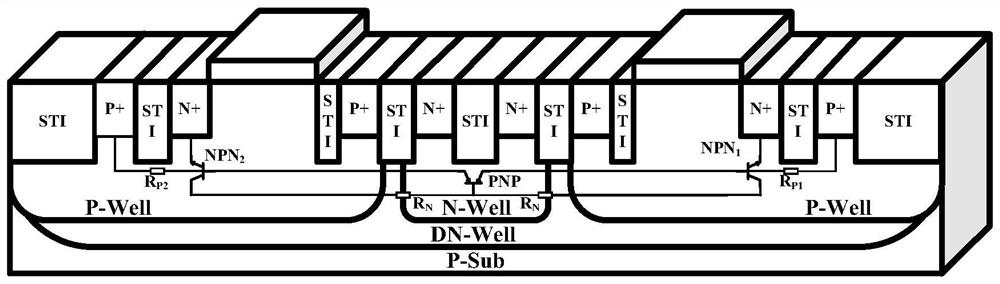

[0030] Such as Figure 2-Figure 5 As shown, a negative resistance clamp silicon controlled rectifier memristive device includes a substrate P-Sub101, and a DN-Well region 102 is provided on the substrate P-Sub101,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More