UVM-based transponder chip multi-module synchronous verification platform and verification method

A synchronous verification and transponder technology, applied in functional inspection, detection of faulty computer hardware, electrical components, etc., can solve the problems of low efficiency, difficult verification of extreme boundaries, poor signal visibility, etc., to improve verification efficiency, reduce effect of quantity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0060] In order to make the purpose, technical solutions and advantages of the embodiments of the present invention more clear, the technical solutions in the embodiments of the present invention will be clearly and completely described below in conjunction with the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments It is a part of embodiments of the present invention, but not all embodiments. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

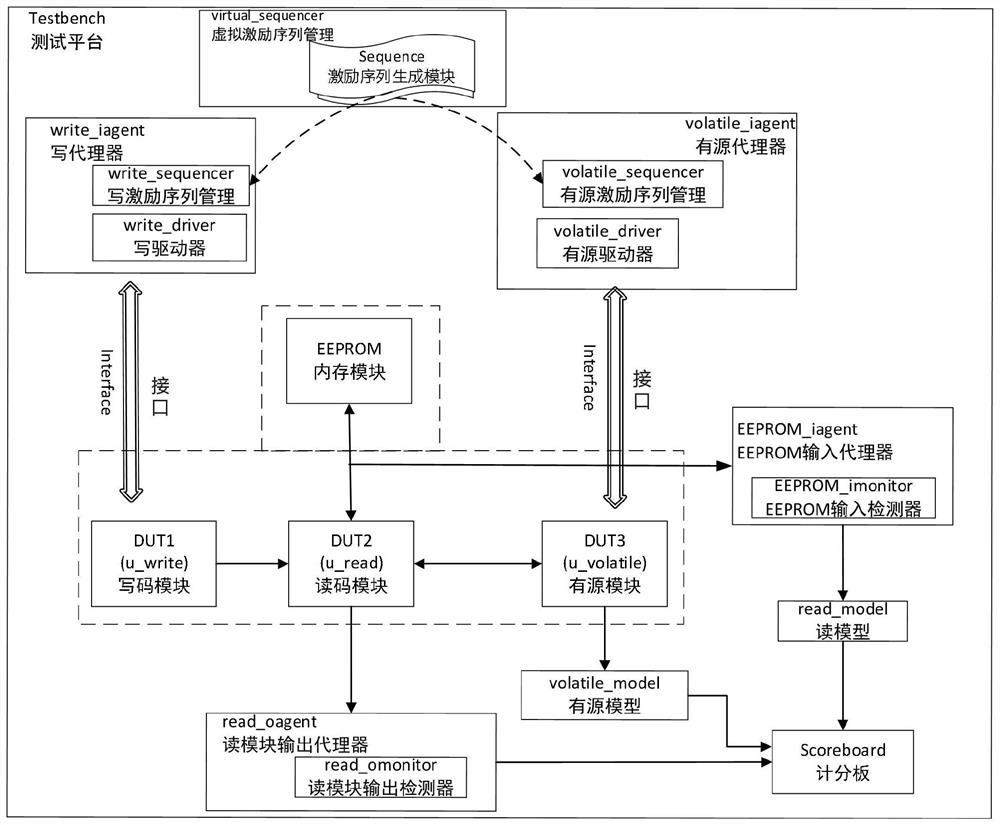

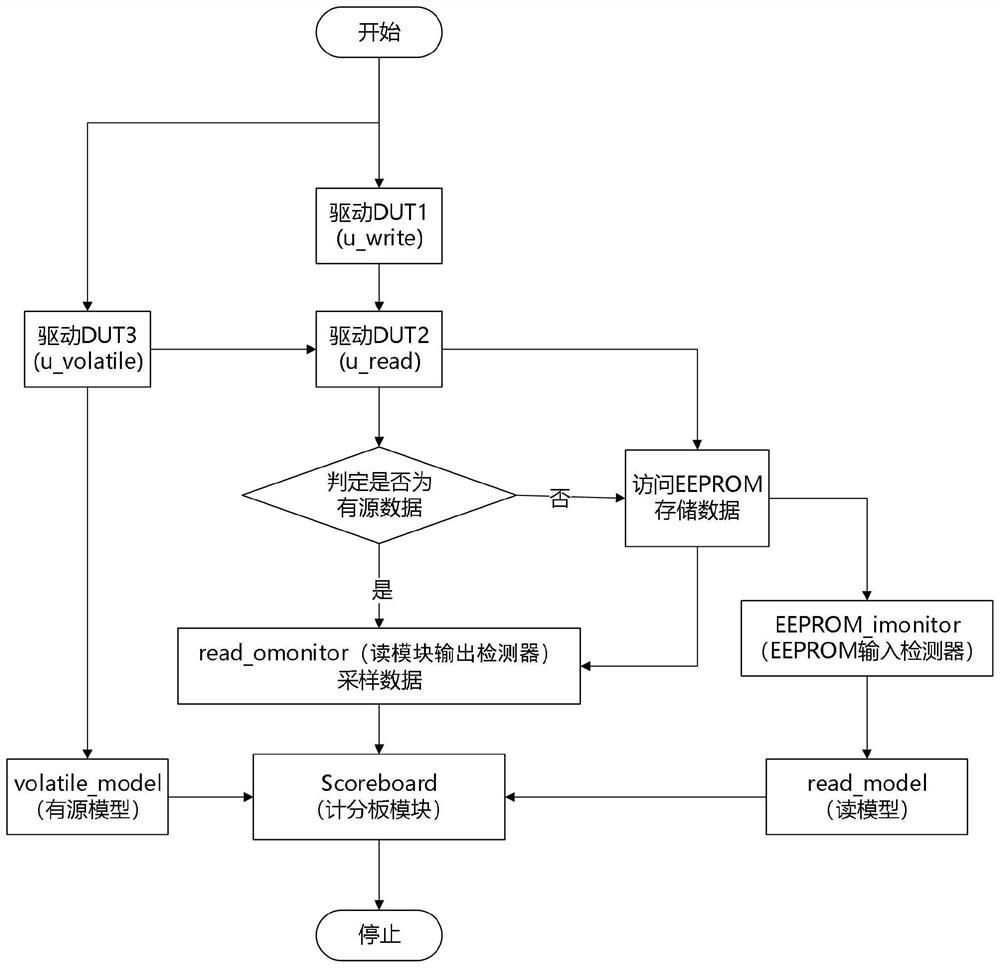

[0061] Universal Verification Methodology (UVM) is a verification platform development framework based on the SystemVerilog class library. Verification engineers can use its reusable components to build a functional verification environment with a standardized hierarchy and interface. In recent years, because the UVM verificat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More