Fan-out packaging method and fan-out packaging structure

A packaging method and fan-out technology, applied in electrical components, electric solid-state devices, circuits, etc., can solve the problems of inability to protect and clamp chips, plastic sealing warpage, chip surface cracking, etc., and improve wafer processing. Efficiency, preventing touch and damage, avoiding the effect of flipping and grasping

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

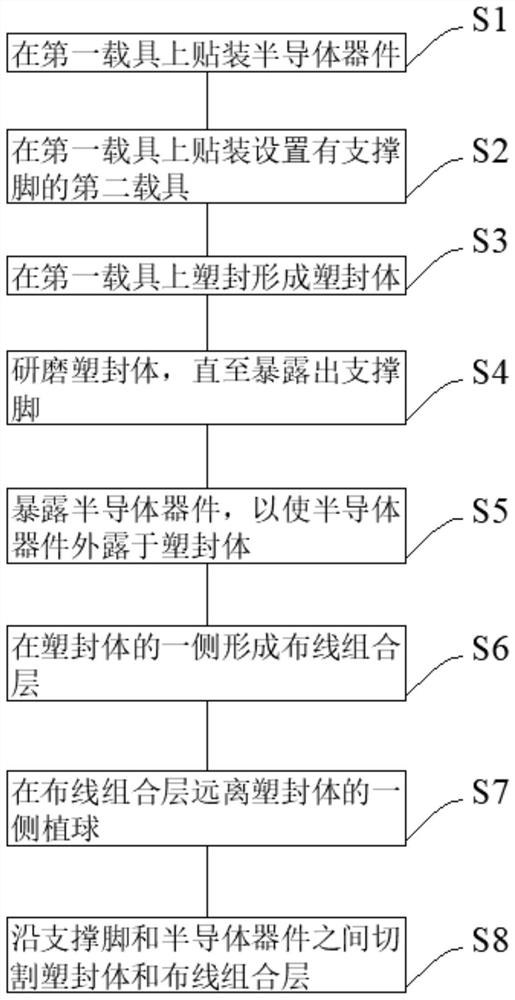

[0078] see figure 1 : This embodiment provides a fan-out packaging method, which is used to prepare a fan-out packaging structure 100, which can solve the problem of warpage of the plastic package in the packaging process, and prevent dust from causing defects, improve product quality, and facilitate Transport and turn over, helping to improve production efficiency.

[0079] The fan-out packaging method provided in this embodiment includes the following steps:

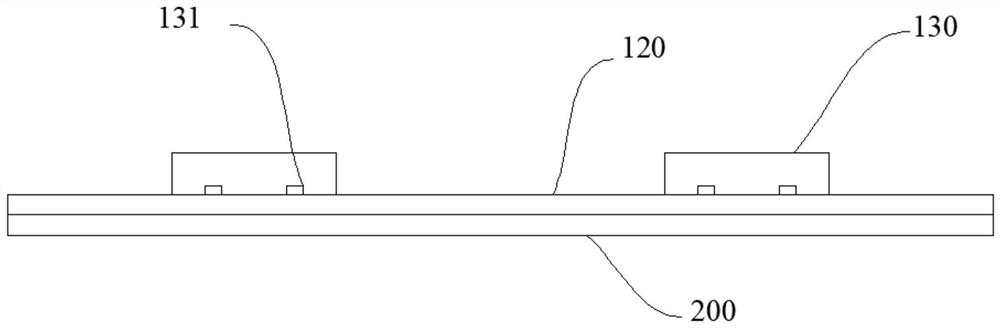

[0080] S1: mounting the semiconductor device 130 on the first carrier 200 .

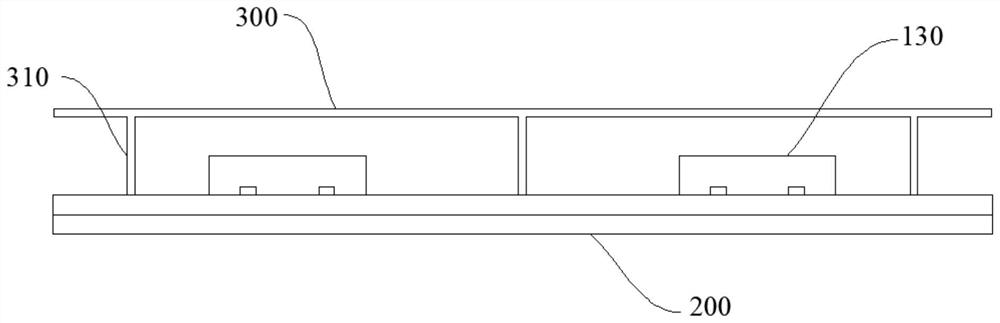

[0081] see in conjunction figure 2 Specifically, in this embodiment, the fan-out packaging structure 100 is prepared in multiple ways at the same time. Here, firstly, a carrier is provided, on which a plurality of semiconductor devices 130 are simultaneously mounted, and the plurality of semiconductor devices 130 are uniformly arranged in an array, so as to facilitate subsequent cutting to form a plurality of fan-out packaging structures ...

no. 2 example

[0137] This embodiment provides a fan-out packaging method, which is used to prepare the fan-out packaging structure 100, and the basic steps of the method are the same as those of the first embodiment. For details not mentioned in this embodiment, please refer to first embodiment.

[0138] The difference between this embodiment and the first embodiment lies in step S6. In this embodiment, when step S6 is executed, the following steps may be specifically included:

[0139] S61: Form a first dielectric layer 151 on one side of the plastic package 110 .

[0140] Specifically, the first dielectric layer 151 covers the semiconductor device 130 and blocks the conductive pad 131 on the semiconductor device 130 . The first dielectric layer 151 can be formed by spin-coating a dielectric layer, or the first dielectric layer 151 can be prepared by physical vapor deposition (PVD) or chemical vapor deposition (CVD).

[0141] S62: Grooving on the first dielectric layer 151 to form a firs...

no. 3 example

[0154] This embodiment provides a fan-out packaging method for preparing a fan-out packaging structure 100, and the basic steps of the method are the same as those of the first embodiment. For details not mentioned in this embodiment, please refer to Section 1. an embodiment.

[0155] The difference between this embodiment and the first embodiment lies in step S5 and step S6.

[0156] see in conjunction Figure 18 and Figure 19 , in this embodiment, the step of exposing the semiconductor device 130 , that is, when performing step S5 , specifically, grooves may be formed on the first carrier 200 to form a substrate groove 210 penetrating to the semiconductor device 130 .

[0157] Specifically, here, a groove is directly made on the first carrier 200 , so that the semiconductor device 130 is exposed to the plastic package 110 . Specifically, a substrate can be selected here as the first carrier 200, and the base groove 210 is formed by directly grooving on the substrate, and...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More