Multi-chip system of integrated antenna and manufacturing method thereof

An integrated antenna and manufacturing method technology, applied in antenna support/mounting device, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problem that antenna packaging cannot form a system-level packaging method, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

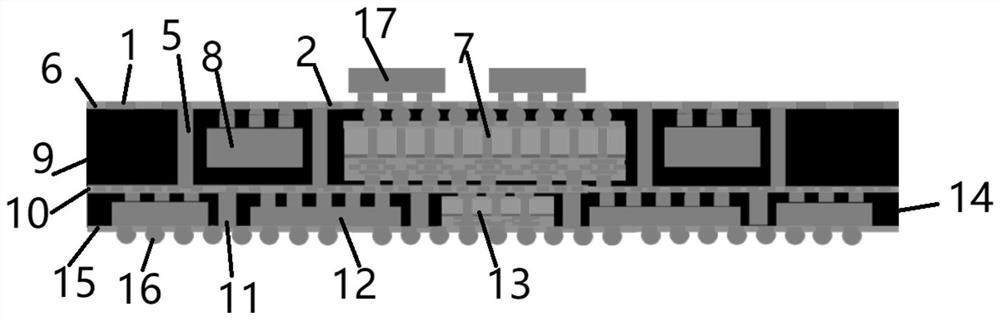

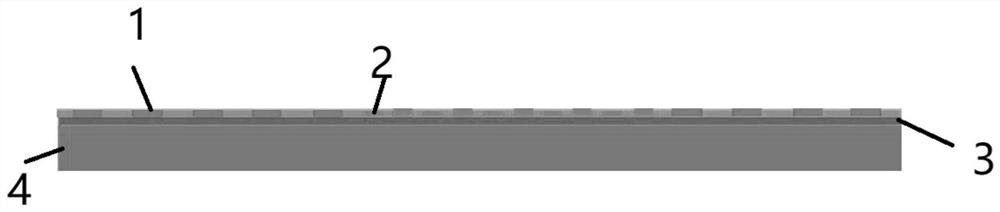

[0098] The present invention will be further described below in conjunction with specific embodiments with reference to the accompanying drawings.

[0099] It should be noted that components in the various figures may be shown exaggerated for the purpose of illustration and are not necessarily true to scale. In the various figures, identical or functionally identical components are assigned the same reference symbols.

[0100] In the present invention, unless otherwise specified, "arranged on", "arranged on" and "arranged on" do not exclude the presence of intermediates between the two. In addition, "arranged on or above" only means the relative positional relationship between two parts, and under certain circumstances, such as after the product direction is reversed, it can also be converted to "arranged under or below", and vice versa Of course.

[0101] In the present invention, each embodiment is only intended to illustrate the solutions of the present invention, and sho...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap