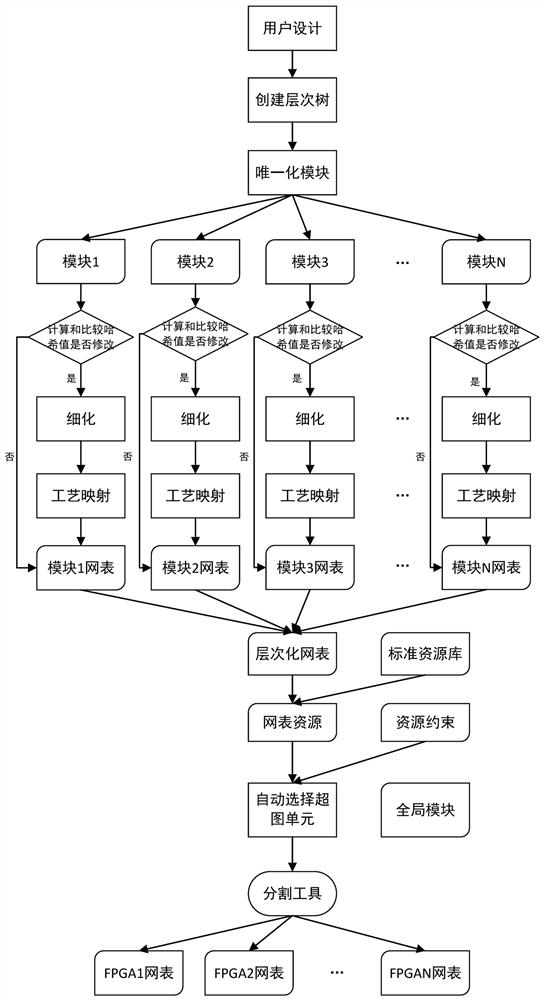

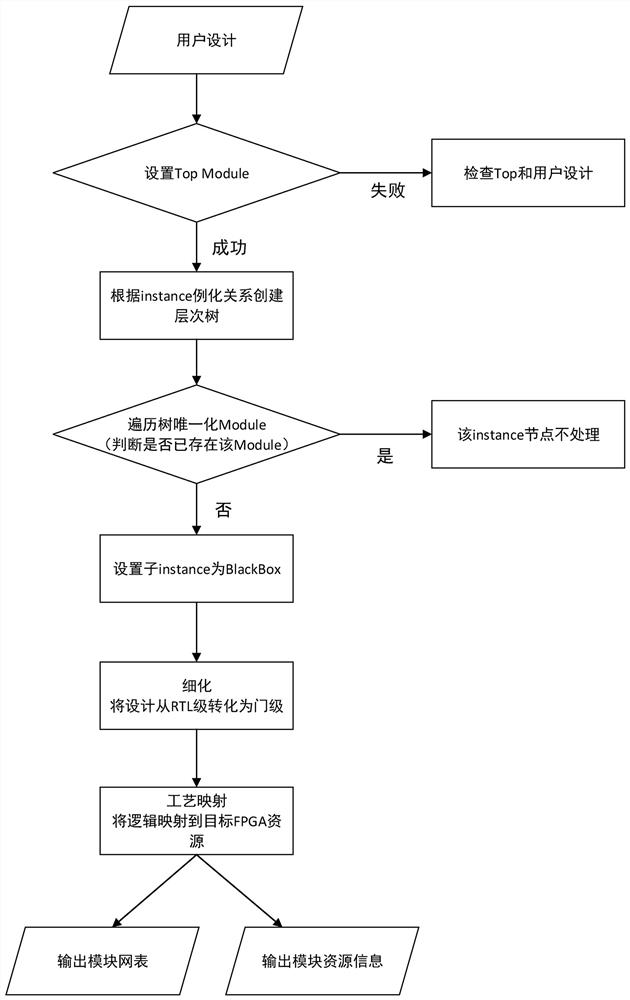

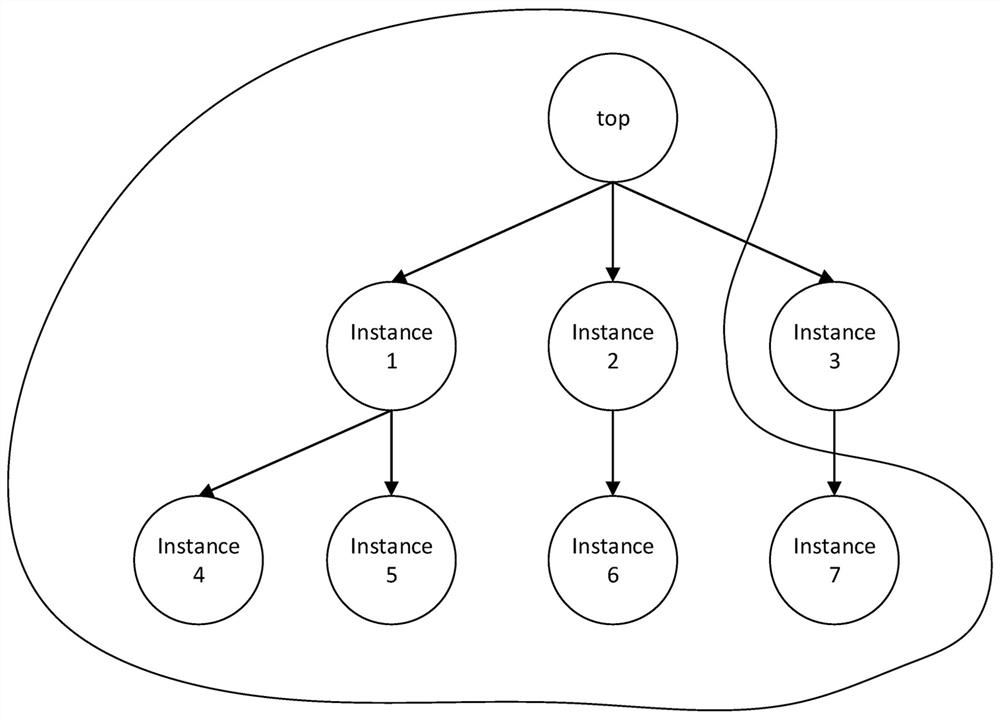

Parallel RTL synthesis method based on multi-FPGA system and storage medium

A comprehensive method and node technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve problems such as low processing efficiency, and achieve the effect of reducing volume, processing time, and recompilation time.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] In order to make the technical problems, technical solutions and beneficial effects to be solved by the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

[0041] Thus, a feature indicated in this specification will be used to describe one of the features of an embodiment of the present invention, rather than implying that every embodiment of the present invention must have the described feature. Furthermore, it should be noted that this specification describes a number of features. Although certain features may be combined to illustrate possible system designs, these features may also be used in other combinations not explicitly described. Thus, the illustrated combinations are not intended to be limiting unless oth...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More