MEMS built-in chip packaging carrier and manufacturing process thereof

A technology for encapsulating carrier boards and manufacturing processes, which is applied in the fields of producing decorative surface effects, decorative arts, and metal material coating processes, etc., and can solve the problems of inability to implement built-in chips, poor packaging and shielding effects, and low signal-to-noise ratio of products problems such as improving sensitivity and signal-to-noise ratio, reducing interference, and increasing volume

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

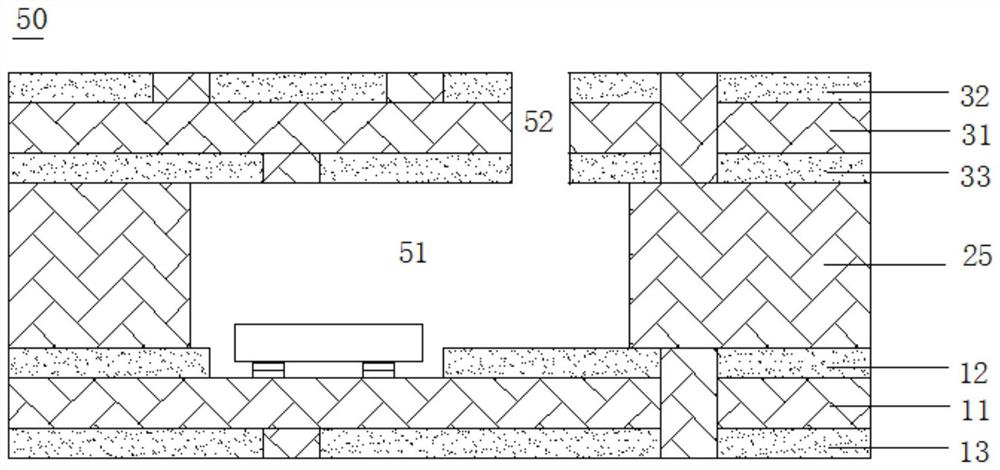

[0060] Example: such as Figure 1-12 As shown, a manufacturing process of a MEMS built-in chip package carrier plate includes the following steps:

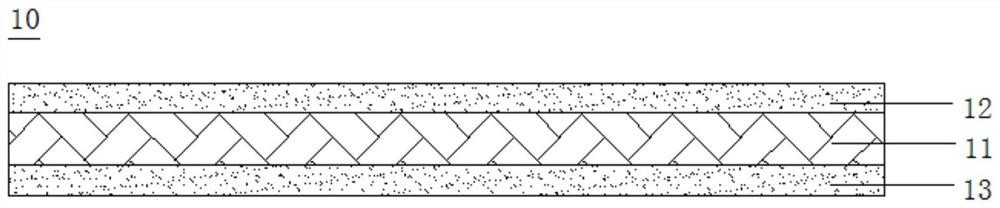

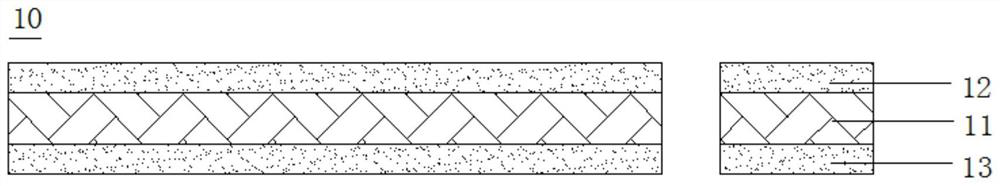

[0061] Step 1: Prepare three core boards, namely the first core board 10, the second core board 20 and the third core board 30, wherein, as figure 2 As shown, the first core board 10 includes a first insulating layer 11 and a first copper foil layer 12 and a second copper foil layer 13 respectively arranged on the front and back sides of the capacitance layer, as shown in Figure 6 As shown, the second core board 20 includes a second insulating layer 21 and a third copper foil layer 22 and a fourth copper foil layer 23 respectively disposed on the front and back sides of the second insulating layer, as shown in Figure 9 As shown, the third core board 30 includes a third insulating layer 31 and a fifth copper foil layer 32 and a sixth copper foil layer 33 respectively disposed on the front and back sides of the third insulating ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More