Manufacturing method of SONOS (Silicon Oxide Nitride Oxide Semiconductor) device

A manufacturing method and device technology, applied in the fields of semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of poor electronic capture capability of flash memory devices, poor device performance, unstable process, etc., and increase retention time. , the effect of increasing the proportion and improving the reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

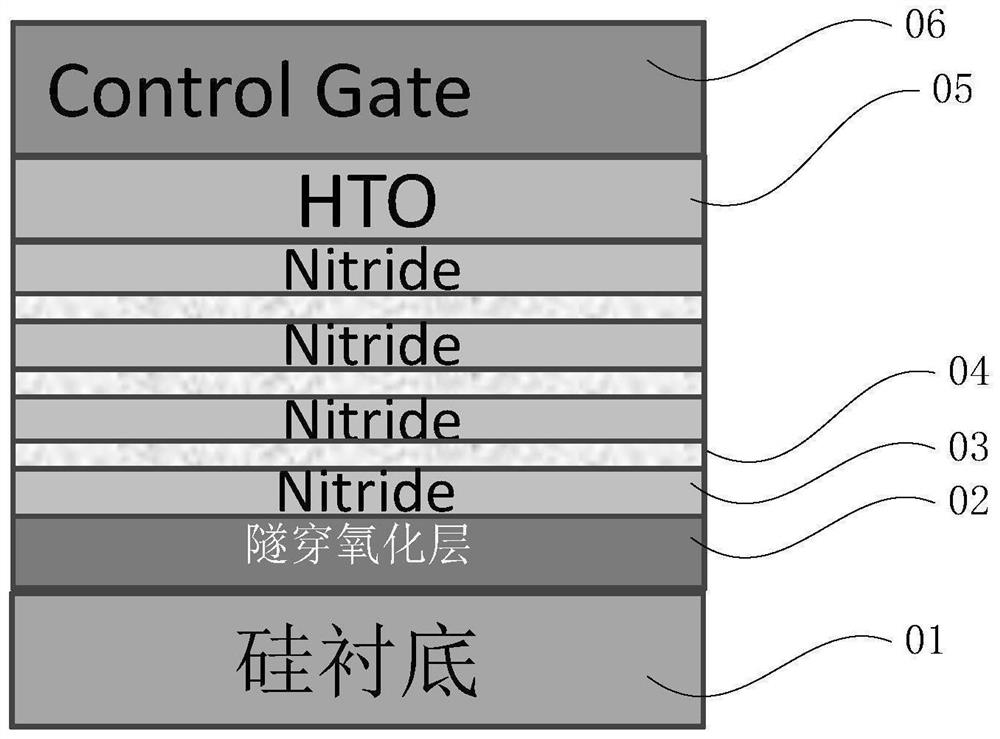

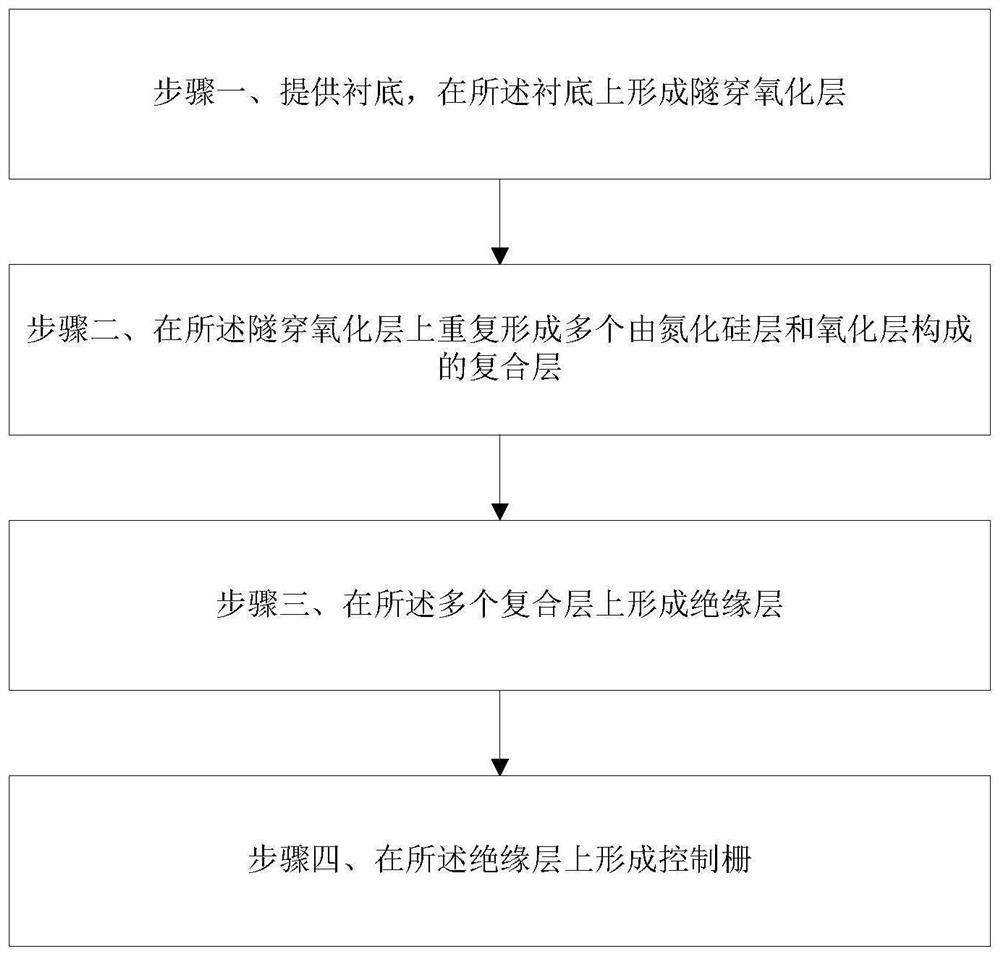

[0024] The invention provides a manufacturing method of a SONOS device, such as figure 2 shown, figure 2 Shown is the flow chart of the manufacturing method of the SONOS device of the present invention, and the method at least comprises the following steps:

[0025] Step 1, providing a substrate, and forming a tunnel oxide layer on the substrate; such as figure 1 shown, figure 1 Shown is a schematic structural diagram of forming a tunnel oxide layer, a composite layer, an insulating layer and a control gate on a substrate in the present invention. In step 1, a tunnel oxide layer 02 is formed on the substrate 01 .

[0026] Further, in the present invention, the substrate 01 in step 1 of this embodiment is a silicon substrate, an active region is provided on the silicon substrate, and the tunnel oxide layer 02 is formed on the silicon substrate of the active region.

[0027] Step 2: Repeatedly forming a plurality of composite layers consisting of a silicon nitride layer a...

Embodiment 2

[0037] The invention provides a manufacturing method of a SONOS device, such as figure 2 shown, figure 2 Shown is the flow chart of the manufacturing method of the SONOS device of the present invention, and the method at least comprises the following steps:

[0038] Step 1, providing a substrate, and forming a tunnel oxide layer on the substrate; such as figure 1 shown, figure 1 Shown is a schematic structural diagram of forming a tunnel oxide layer, a composite layer, an insulating layer and a control gate on a substrate in the present invention. In step 1, a tunnel oxide layer 02 is formed on the substrate 01 .

[0039] Further, in the present invention, the substrate 01 in step 1 of this embodiment is a silicon substrate, an active region is provided on the silicon substrate, and the tunnel oxide layer 02 is formed on the silicon substrate of the active region.

[0040] Step 2: Repeatedly forming a plurality of composite layers consisting of a silicon nitride layer a...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap