I3C bus verification method and verification system

A bus verification and verification test technology, applied in the field of digital verification, can solve the problems of cumbersome code replacement, error-prone, difficult to cover the I3C bus, etc., and achieve the effect of ensuring integrity and efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

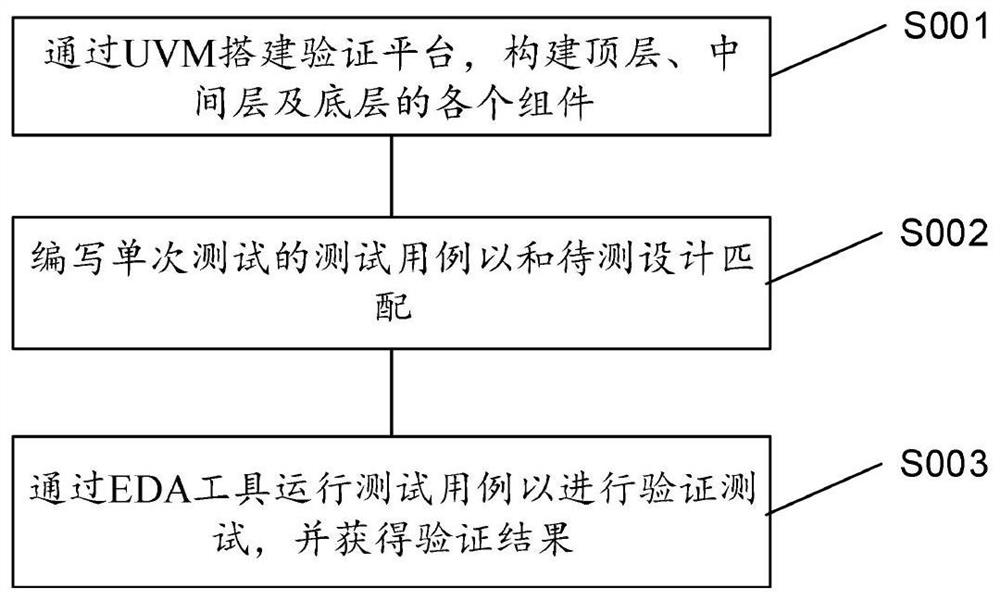

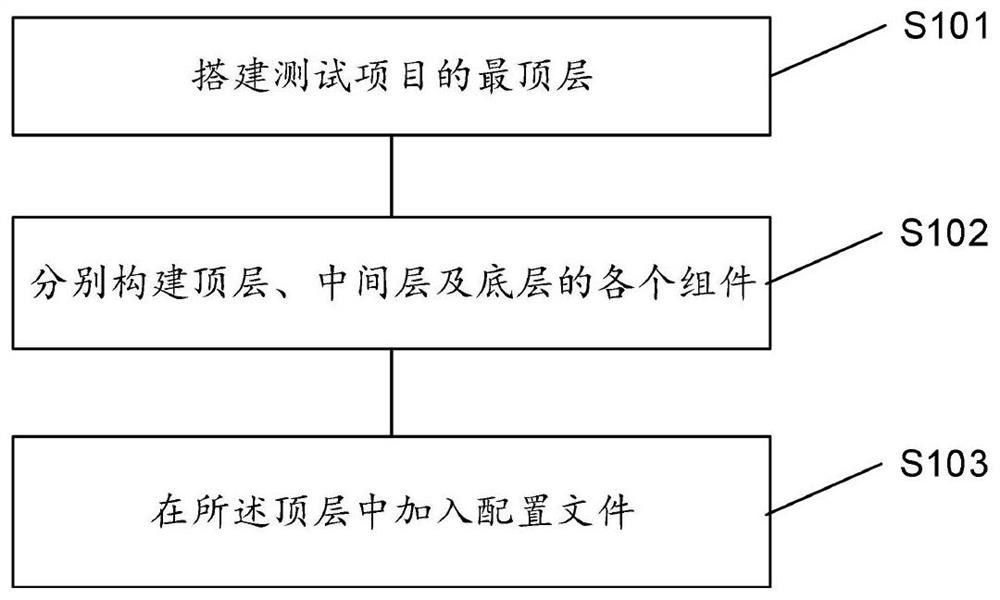

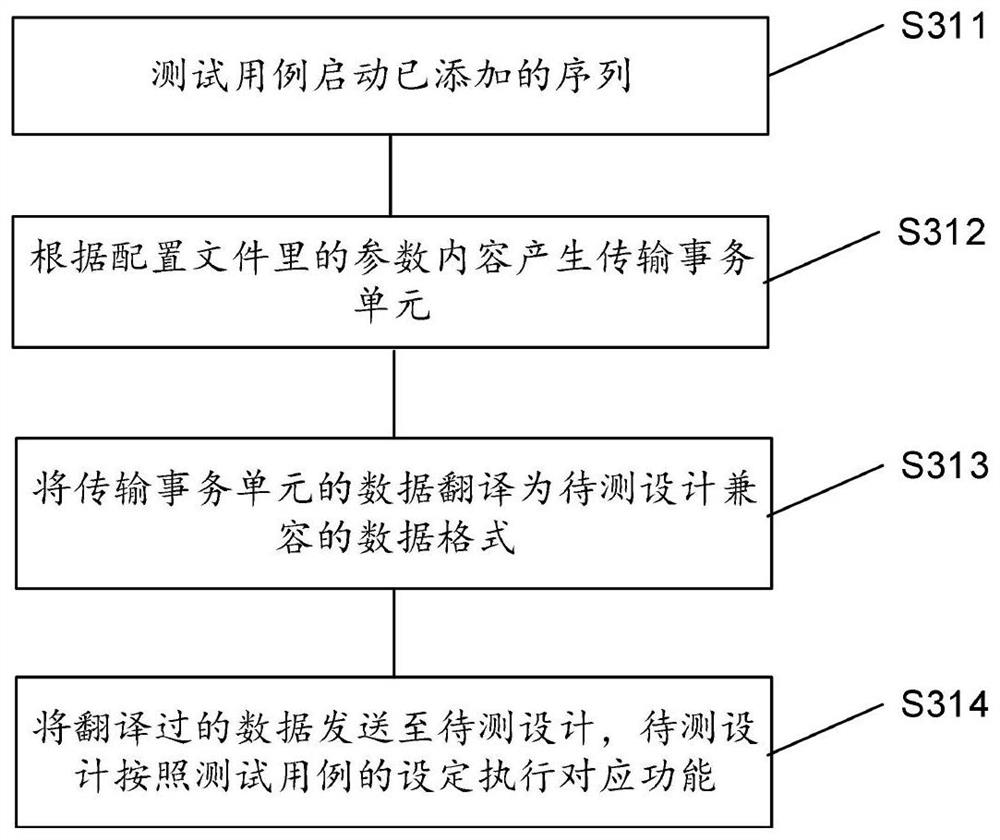

[0037] Embodiments of the present invention will now be described with reference to the accompanying drawings, in which like reference numerals represent like elements. As mentioned above, the present invention provides an I3C bus verification method and verification system. The UVM general verification methodology used in the solution of the present invention is oriented to all digital designs, covering from modules to systems, from ASIC (application-specific integrated circuits) to FPGA, as well as all scenarios from control logic, data path to processor verification object, verification engineers can flexibly change the properties of the verification platform according to specific design specifications to ensure the integrity and efficiency of verification.

[0038] The I3C bus verification method and verification system of the present invention are all realized based on the UVM platform, and UVM (Universal Verification Methodology, Universal Verification Methodology) is a l...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More