Process for preparing MOS transistor

A manufacturing process, semiconductor technology, applied in the direction of semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of component stability, reduce product qualification rate, change the electrical characteristics of components, etc., to increase the qualification rate and improve stability performance, and the effect of reducing the amount of loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

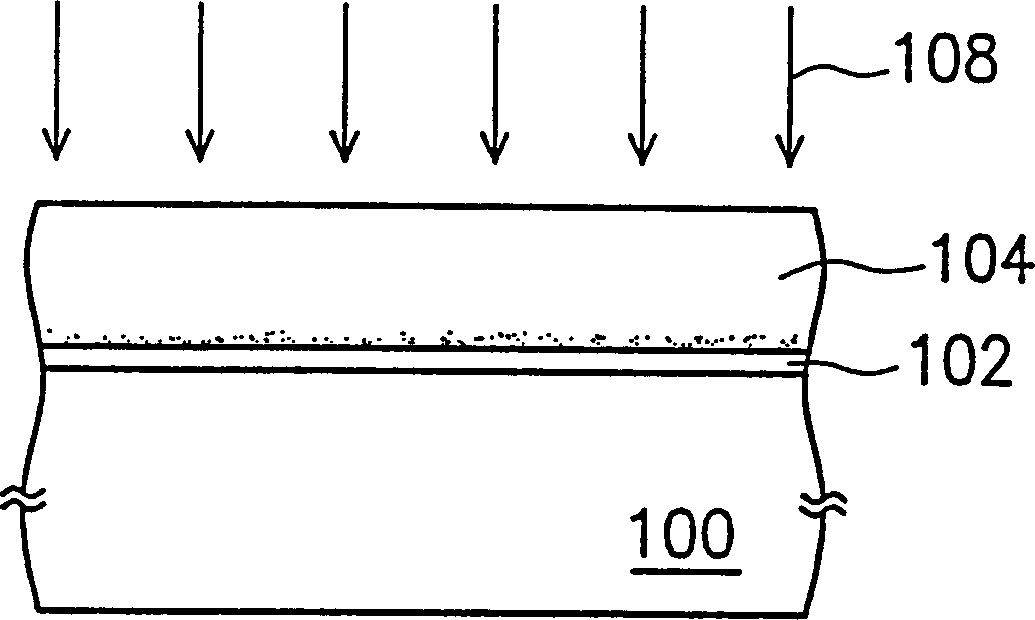

[0023] Figure 1 to Figure 2 Shown is a schematic diagram of a metal oxide semiconductor transistor process in a preferred embodiment of the present invention. Please refer to figure 1 First, a substrate 100 is provided, and then a gate dielectric layer 102 and a polysilicon layer 104 are sequentially formed on the substrate 100 , wherein the material of the gate dielectric layer 102 includes silicon dioxide.

[0024] Next, please refer to figure 2 , implanting nitrogen ions 108 into the connection between the polysilicon layer 104 and the gate dielectric layer 102 , wherein the implantation dose and energy used need to be adjusted according to the actual situation.

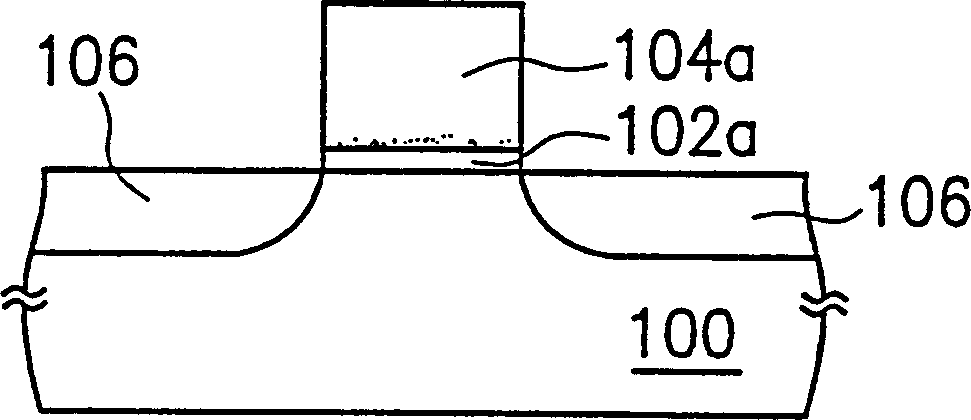

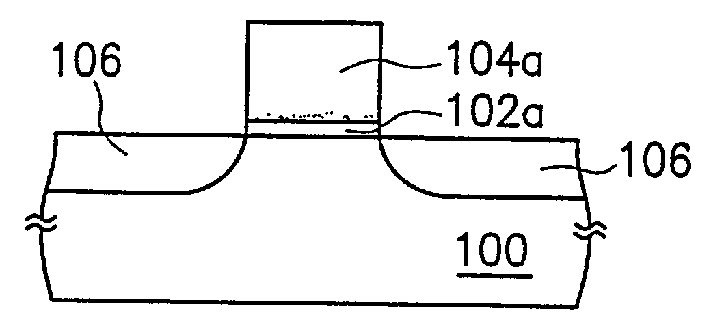

[0025] A tempering step is then performed to enlarge the grains in the polysilicon layer 104 . Next, a photolithographic etching process is performed to pattern the polysilicon layer 104 to form the gate 104a. Next, an ion implantation step is performed to form source / drain regions 106 in the substrates on b...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com