Dielectric layer reetching method

A dielectric layer and etch-back technology, which is applied in the manufacture of circuits, electrical components, semiconductors/solid-state devices, etc., can solve the problem of uneven thickness of the dielectric layer and achieve the effect of improving the problem of uneven thickness of the dielectric layer

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

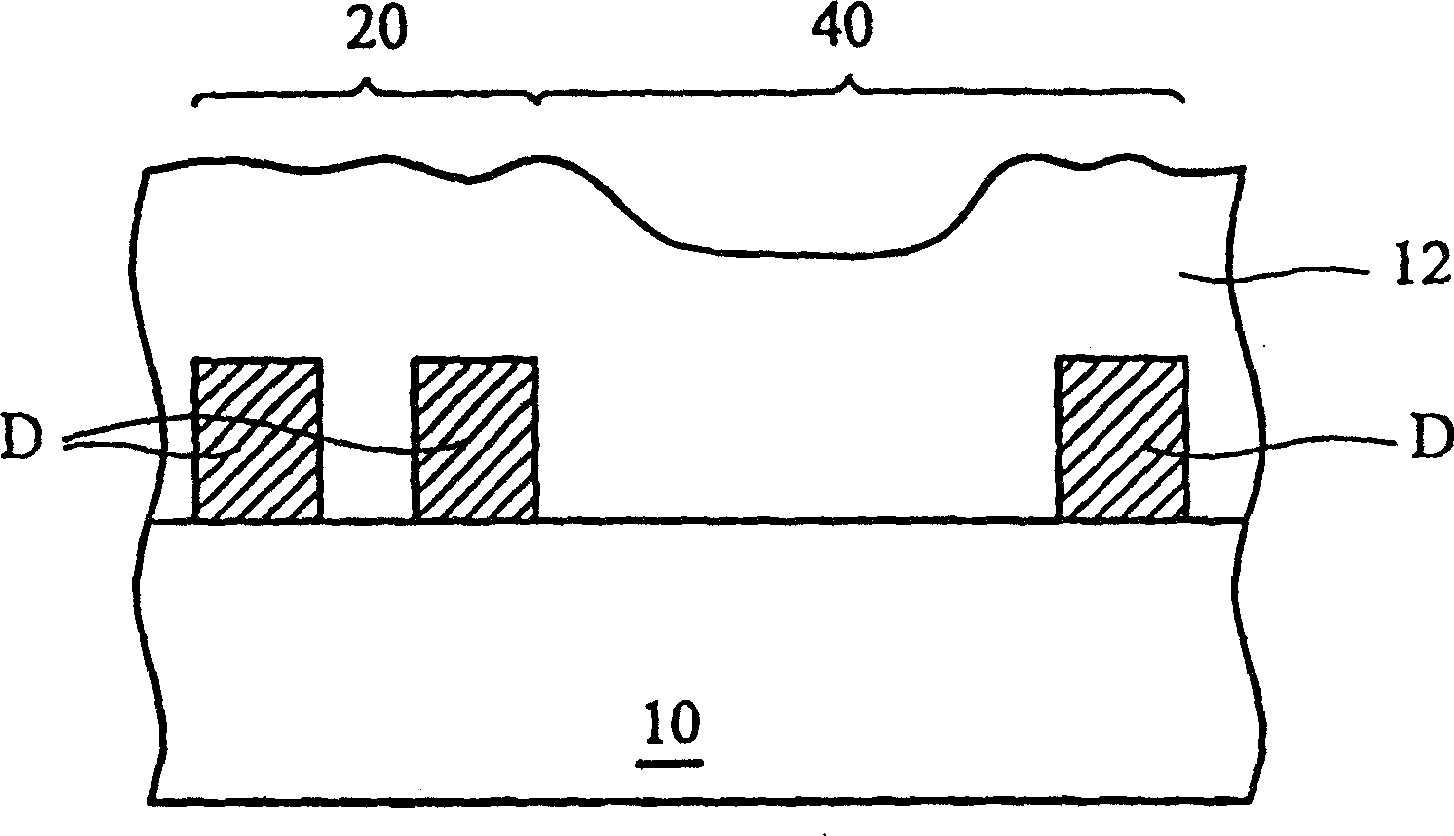

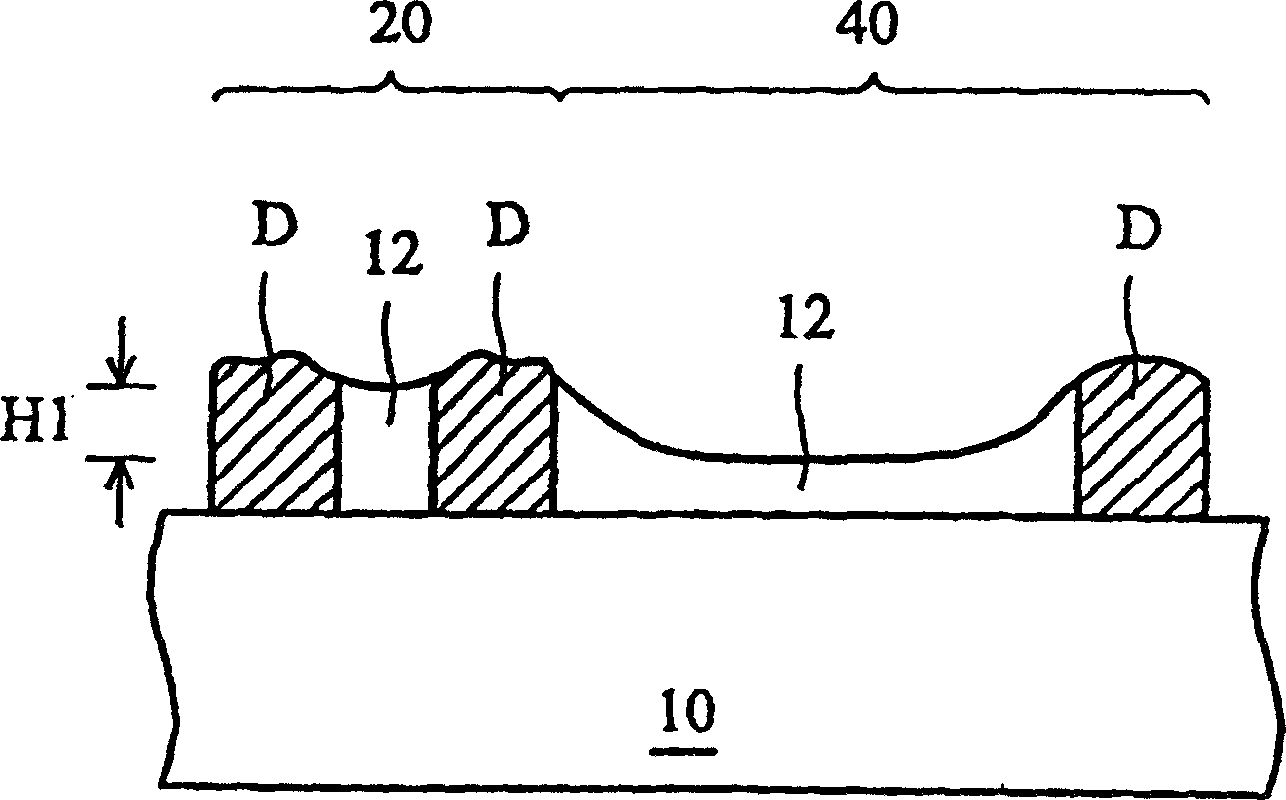

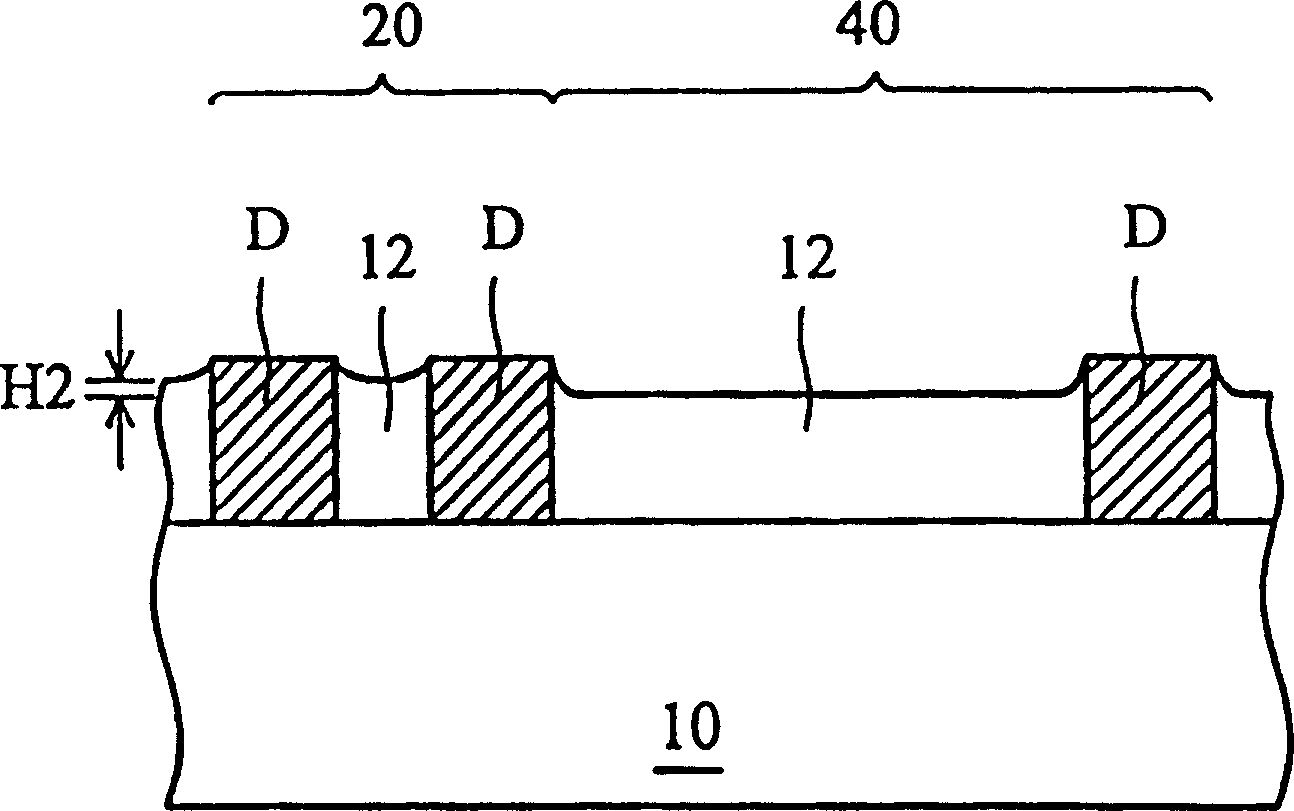

[0017] In this embodiment, the ILD layer is planarized according to the method of the present invention to provide a better planarized structure. Such as figure 1 As shown, a semiconductor substrate 10 is provided, with a plurality of elements D distributed in a sparse area 40 with a small number of elements and a dense area 20 with a large number of elements. The elements D are, for example, MOS transistors, capacitor structures (capacitor ) or other logic components (logic devices), while the surface of component D is made of silicon nitride (Si 3 N 4 ), polysilicon (poly-silicon), amorphous silicon (amorphoussilicon), metal or metal nitride and other non-oxygen (Oxygen free) materials. Next, a dielectric layer material is formed to cover the element D in the element sparse region 40 and the element dense region 20, wherein the dielectric layer material is formed of an oxygen-containing (oxygen contained) material, For example, silicon dioxide, doped silicon dioxide (BSG,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More