Bottom buffering metal lug structure

A metal structure and buffer metal layer technology, which is applied to electrical components, electrical solid-state devices, circuits, etc., can solve the problems of weakening the bonding strength of the solder bump 18 and the bottom metal layer 100 of the bump, reducing the electrical performance of the chip 10, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

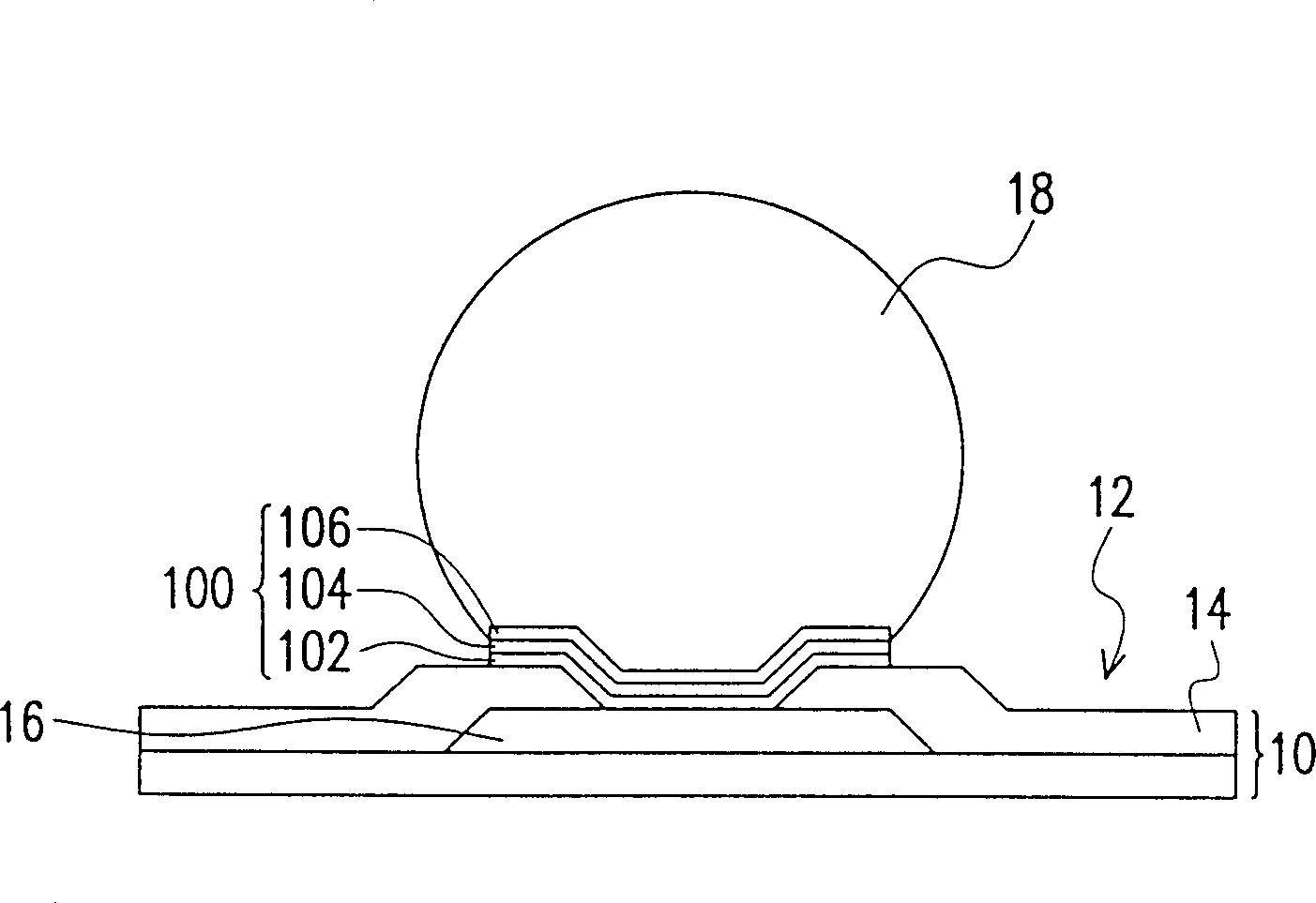

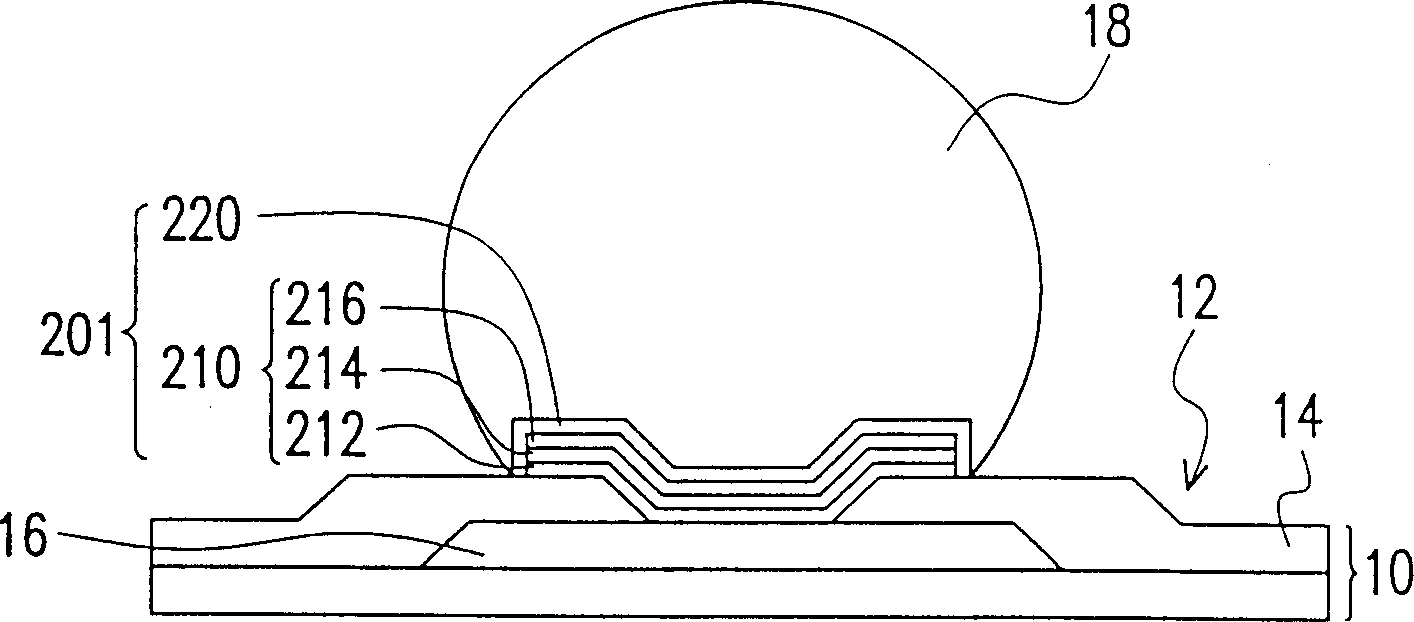

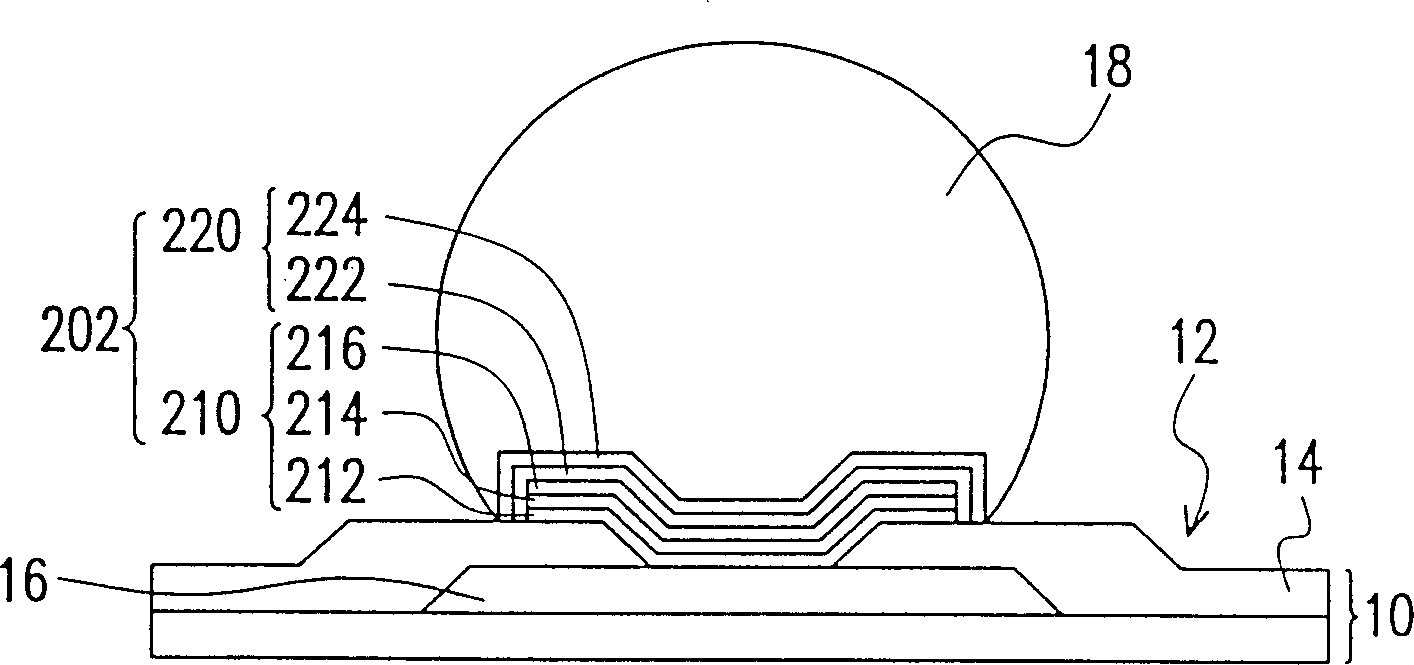

[0043] Please refer to Figure 2A , which is a schematic cross-sectional view of the first under-bump buffer metal structure according to a preferred embodiment of the present invention, which is disposed between a pad and a solder bump of a chip. The chip 10 has an active surface 12, a protection layer 14 and a plurality of pads 16 (only one of them is shown), and the protection layer 14 and the pads 16 are all configured on the active surface 12 of the chip 10, and the protection layer 14 is exposed The bonding pad 16 is above the active surface 12 of the chip 10 . It should be noted that the active surface 12 of the chip 10 generally refers to the side of the chip 10 with active components. In order to provide an interface for bonding between the solder pad 16 and the solder bump 18, the present invention proposes a first under-bump buffer metal structure 201 for disposing between the solder pad 16 and the solder bump 18, which mainly includes a metal layer 210 and a buffe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More