Method for making non-volatile memory with shallow junction

A non-volatile, manufacturing method technology, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problem that the source/drain extension region is difficult to maintain, and achieve the effect of eliminating performance reduction and slowing down damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0033] Embodiments of the present invention relate to a method of fabricating a non-volatile memory with shallow source / drain extensions, which can eliminate or reduce various problems in conventional methods.

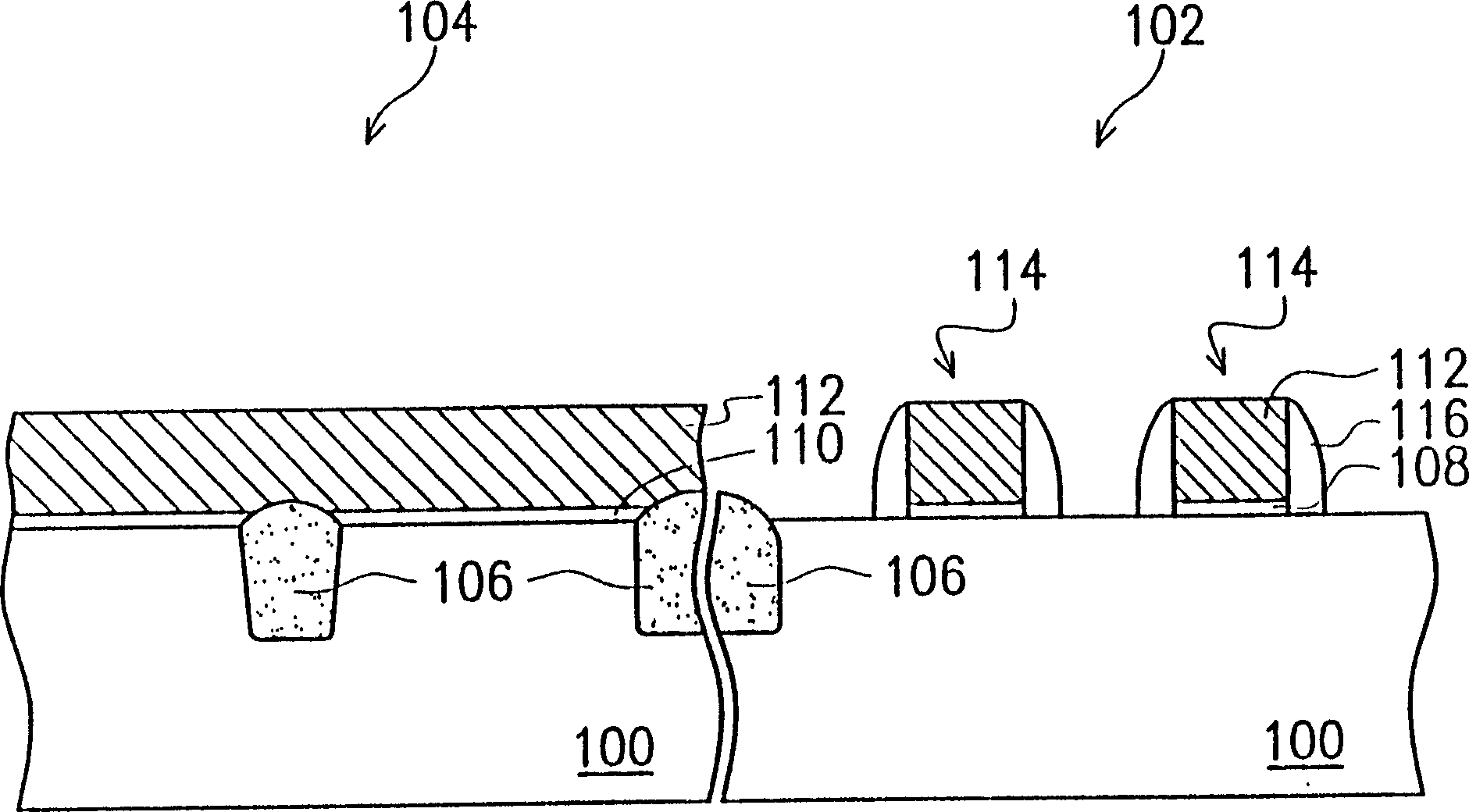

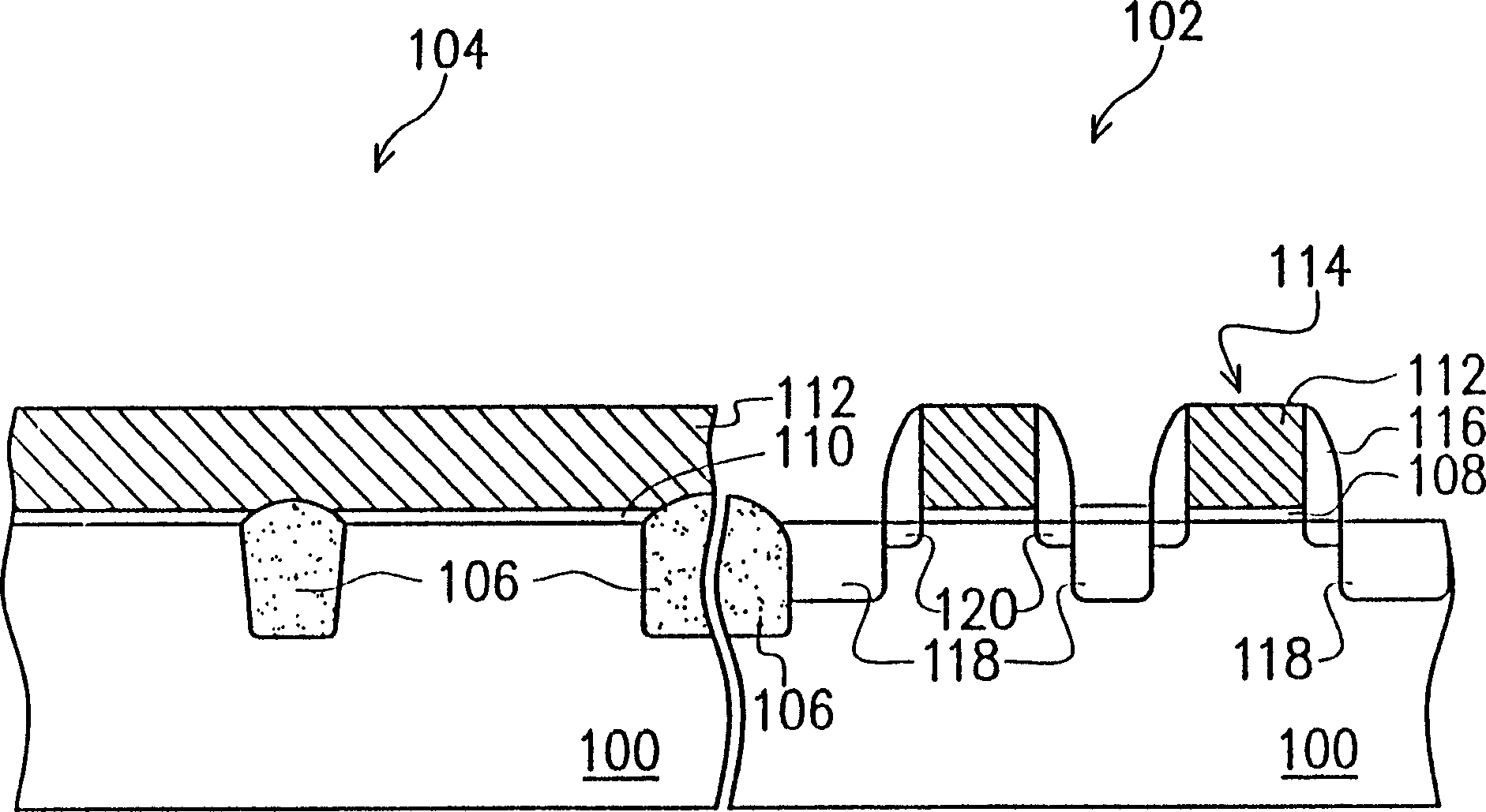

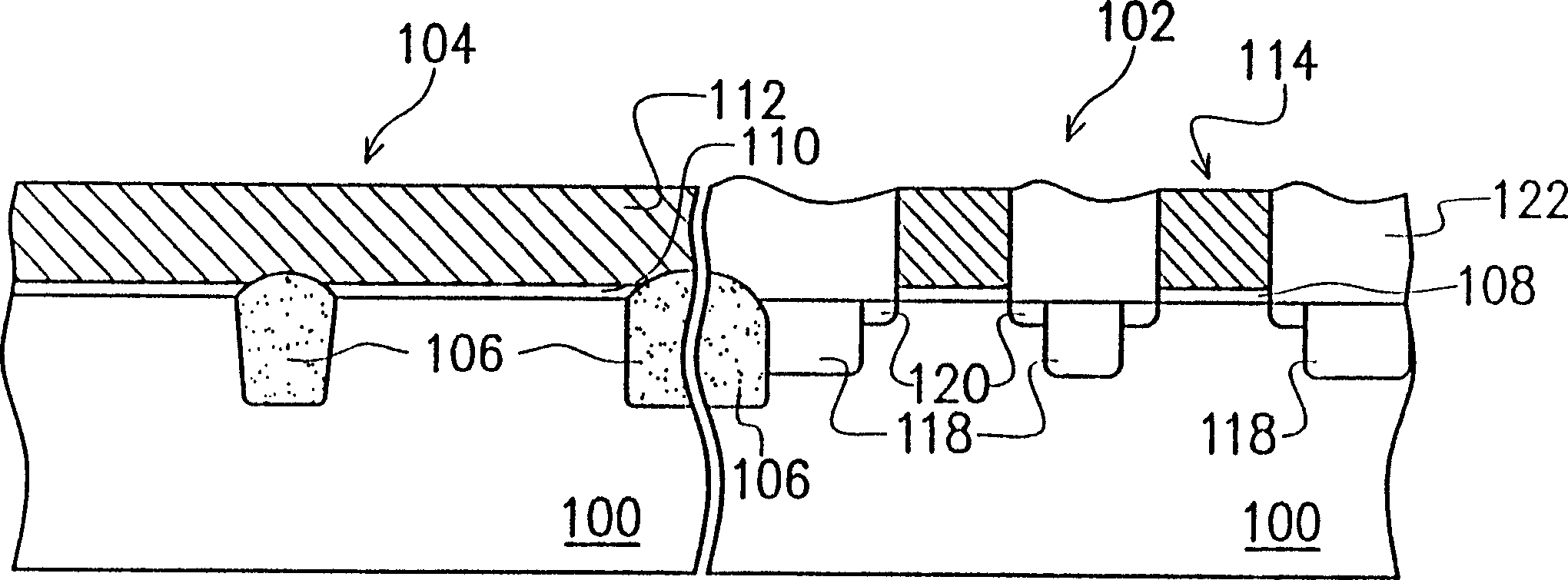

[0034] Figures 1A-1E It is a cross-sectional view of manufacturing an embedded non-volatile memory according to an embodiment of the present invention. Such as Figure 1A As shown, the substrate 100 includes a memory cell region 102 and a peripheral circuit region 104, and isolation structures 106 are used to isolate the memory cell region 102, the peripheral circuit region 104 and other components. . The isolation structure 106 is, for example, a field oxide (FOX) or a shallow trench isolation (STI). A silicon monoxide / silicon nitride / silicon oxide (oxide / nitride / oxide, ONO) layer 108 is formed in the memory cell region 102 . The method for forming the silicon oxide / silicon nitride / silicon oxide layer 108 is, for example, sequentially forming a silicon oxide layer...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More