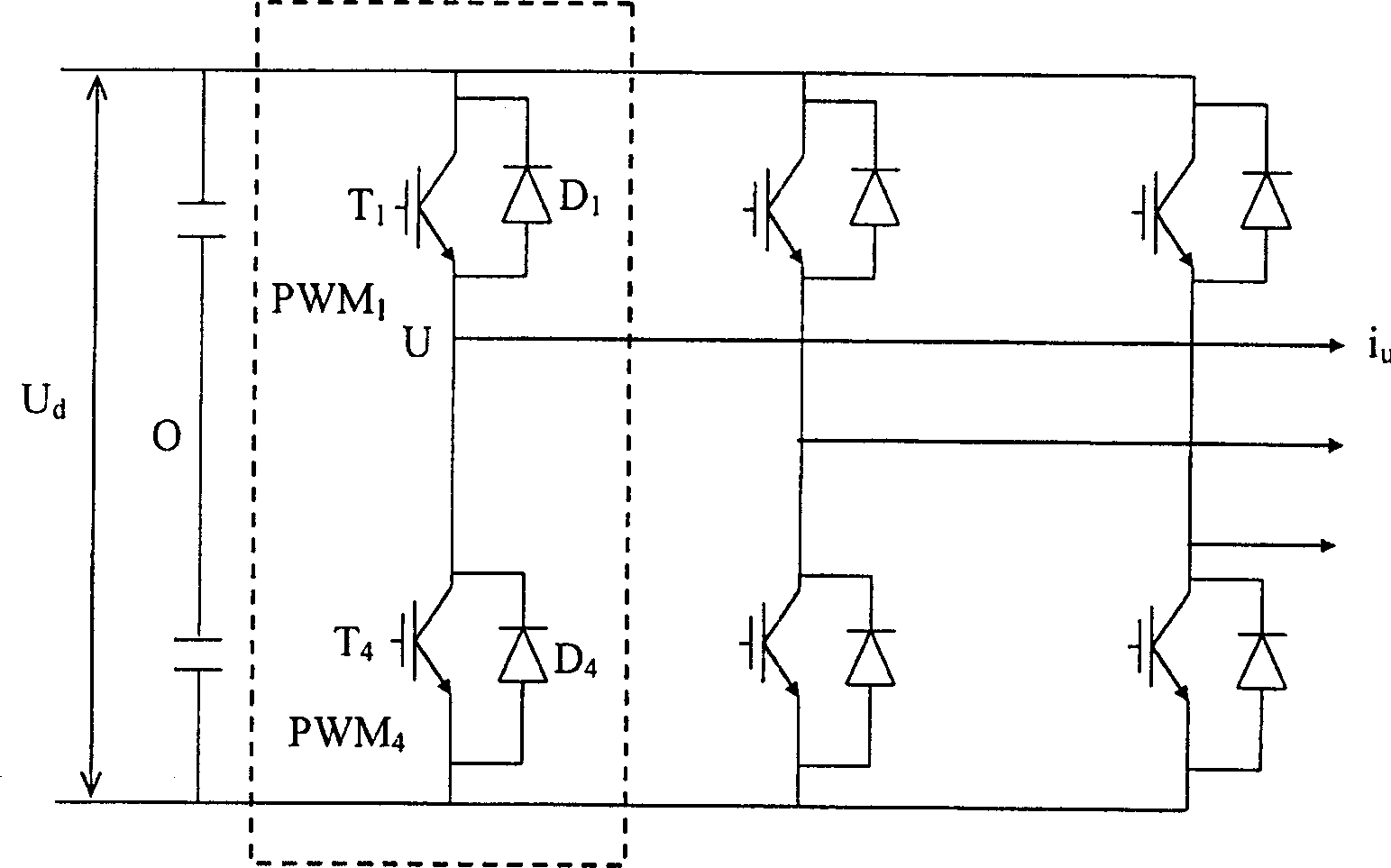

Method and apparatus for adaptive compensation of dead time for inverter and converter

A dead time, inverter technology, applied in the output power conversion device, the conversion of AC power input to DC power output, electrical components and other directions, can solve problems such as difficulty in reducing Uuo

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046] Although the present invention can be implemented in various forms, in order to simplify the description, the details of some preferred embodiments will be further described and illustrated below. However, the content disclosed here is to illustrate the principle of the present invention, but not limited to the following embodiments.

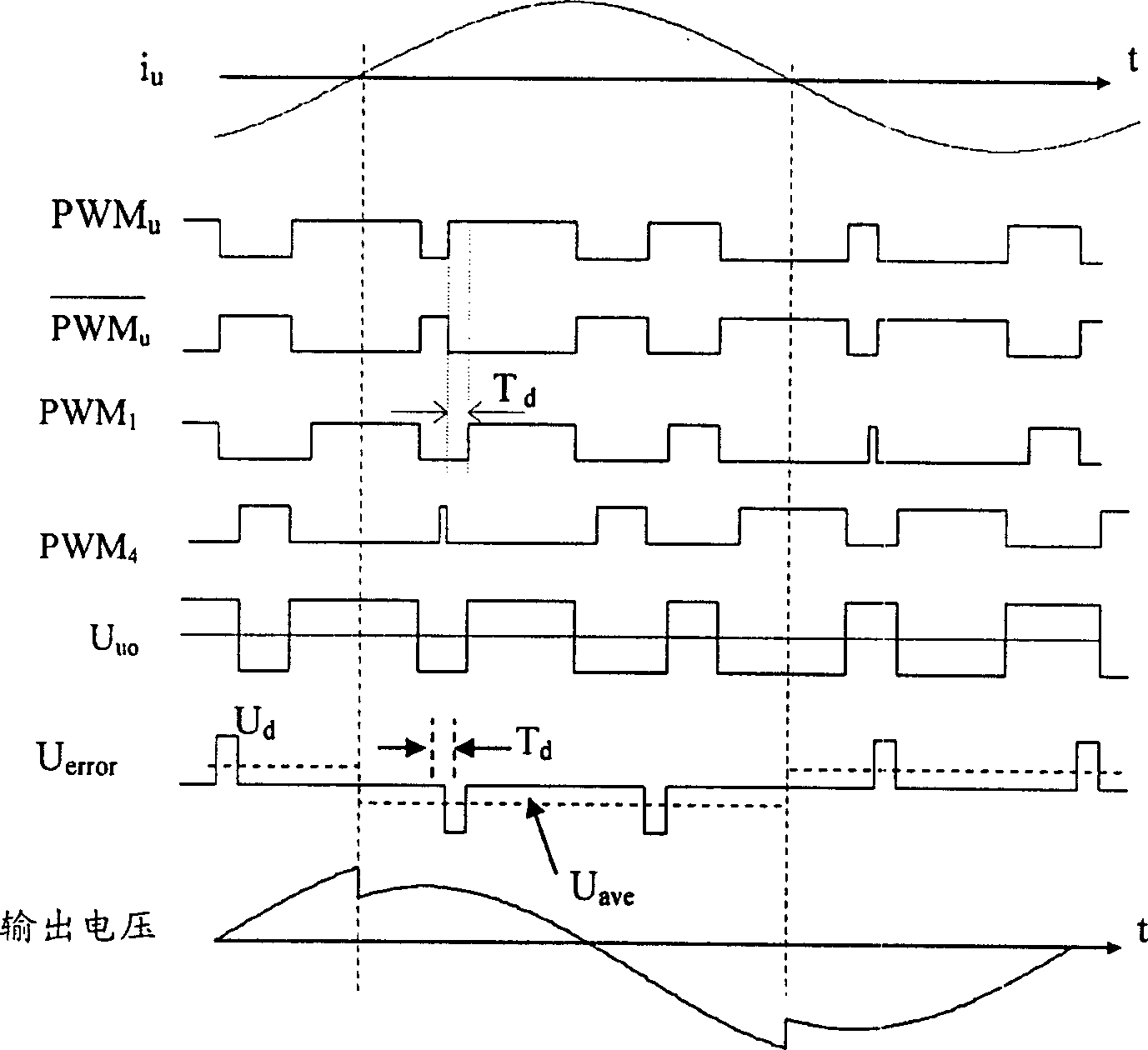

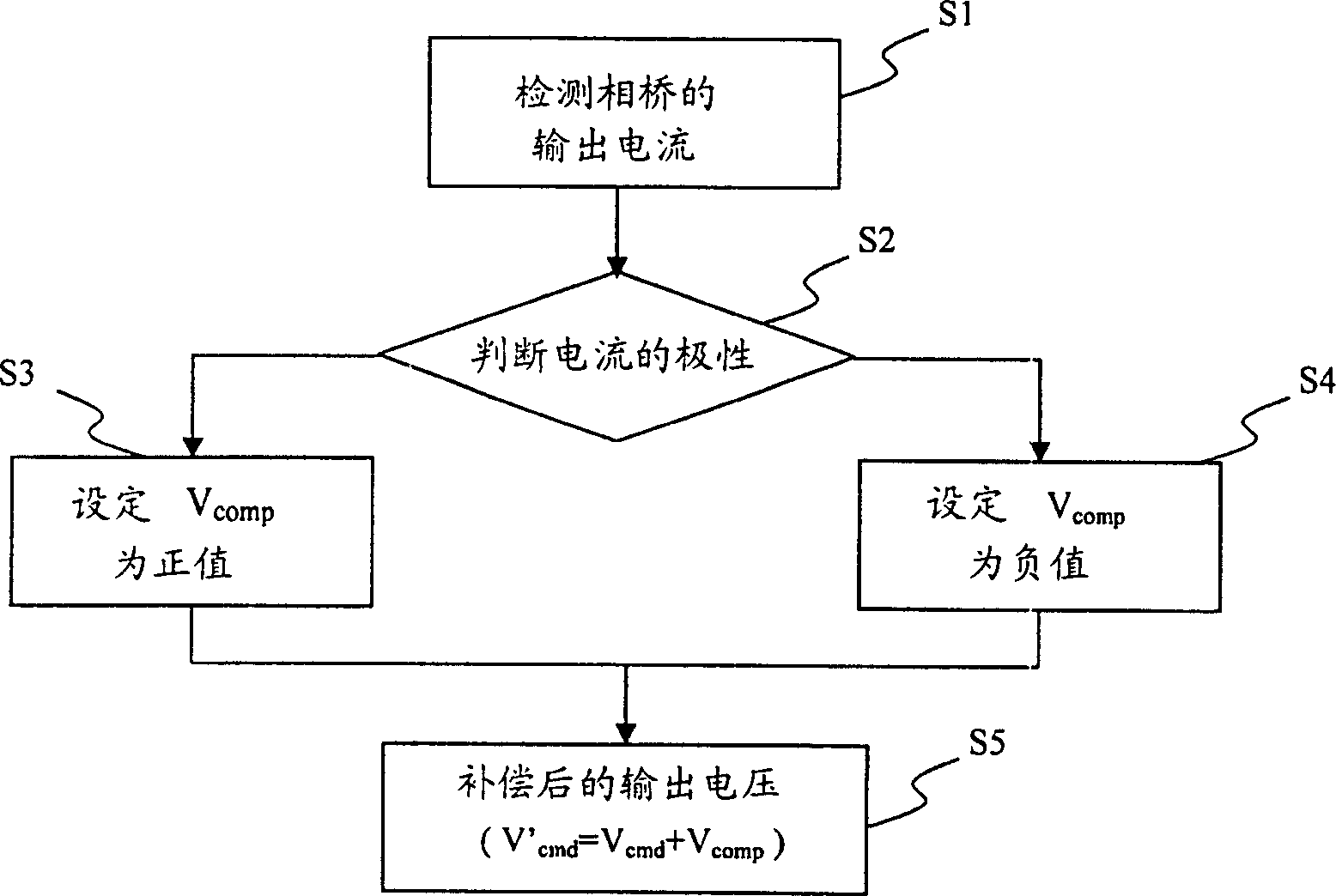

[0047] As mentioned above, the voltage shift caused by the dead time is in the opposite direction to the output current, and its magnitude depends on the direction of the output current. For simplicity, the voltage offset waveform is simplified as Figure 7 The trapezoid shown. see Figure 7 , at t 2 with t 3 During, because the delay time is large enough to automatically compensate the dead time, and at t 1 with t 2 period and t 3 with t 4 During this period, the delay time is gradually increased, and the dead time part is automatically compensated. To compensate for this offset voltage, as Figure 7 The reverse voltage shown i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More