Differential high speed cmos to ecl logic converter

A converter and differential technology, applied in the direction of logic circuit interface device, logic circuit connection/interface layout, pulse generation, etc., can solve the problem of no differential output, etc., and achieve the effect of low operating voltage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] Those skilled in the art will realize that the following description of the invention is illustrative only and not limiting in any way. Other embodiments of the present invention will be readily apparent to those skilled in the art upon reading this specification.

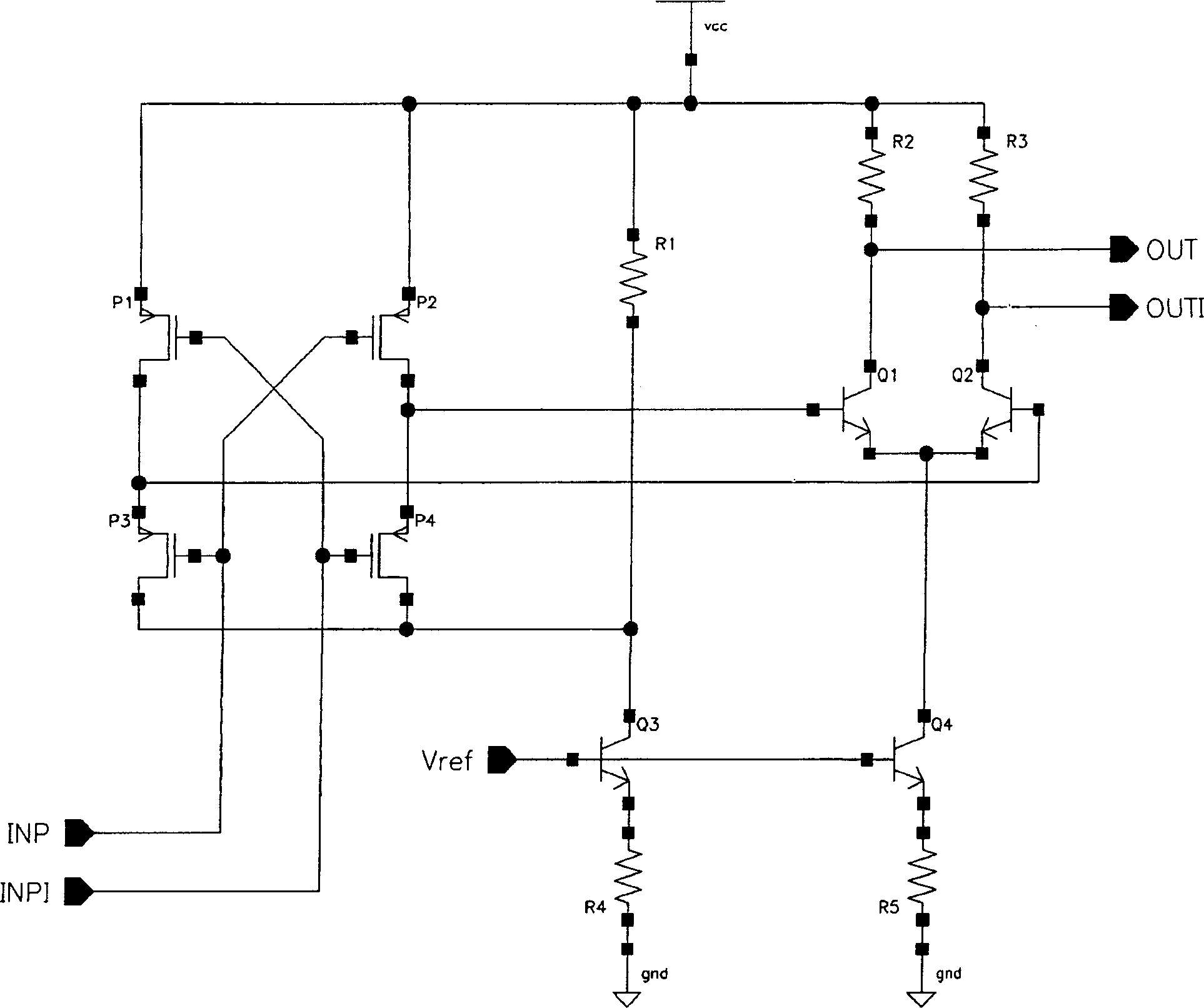

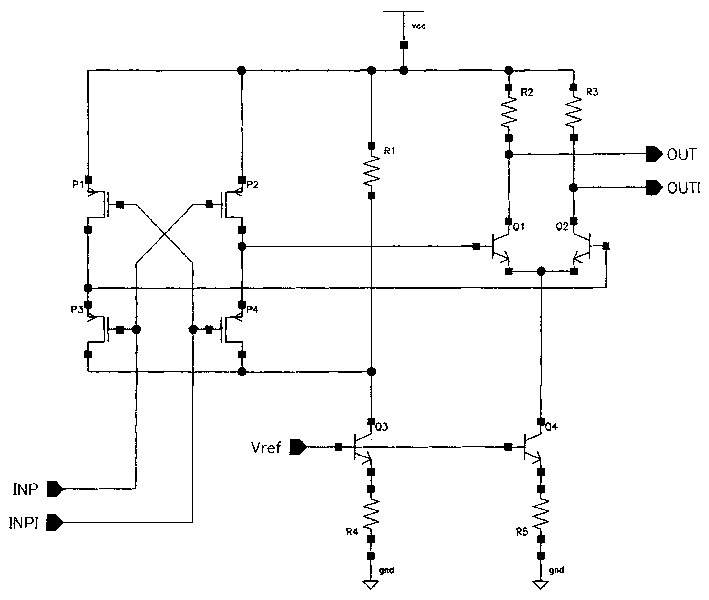

[0040] figure 1 The high speed, low hysteresis logic level translator of the present invention is shown in simplified form. The converter is used to convert a differential complementary pair of input signals at input nodes INP and INPI (input and inverting input) from potentials associated with CMOS logic levels to output nodes OUT and OUTI at potentials associated with ECL logic levels The output signal is a differential complementary pair. It is contemplated that the potentials associated with OUT and OUTI may be generated by converters at levels other than those associated with ECL, including but not limited to firing transceiver logic (GTL).

[0041] The converter of the present invention comprises tw...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More