Processor apparatus, information processor using the same, compiling apparatus and method thereof

A processor, command processing technology, applied in electrical digital data processing, preventing unauthorized use of memory, instruments, etc., can solve problems such as difficulty in maintaining the protection range correctly

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment approach 1

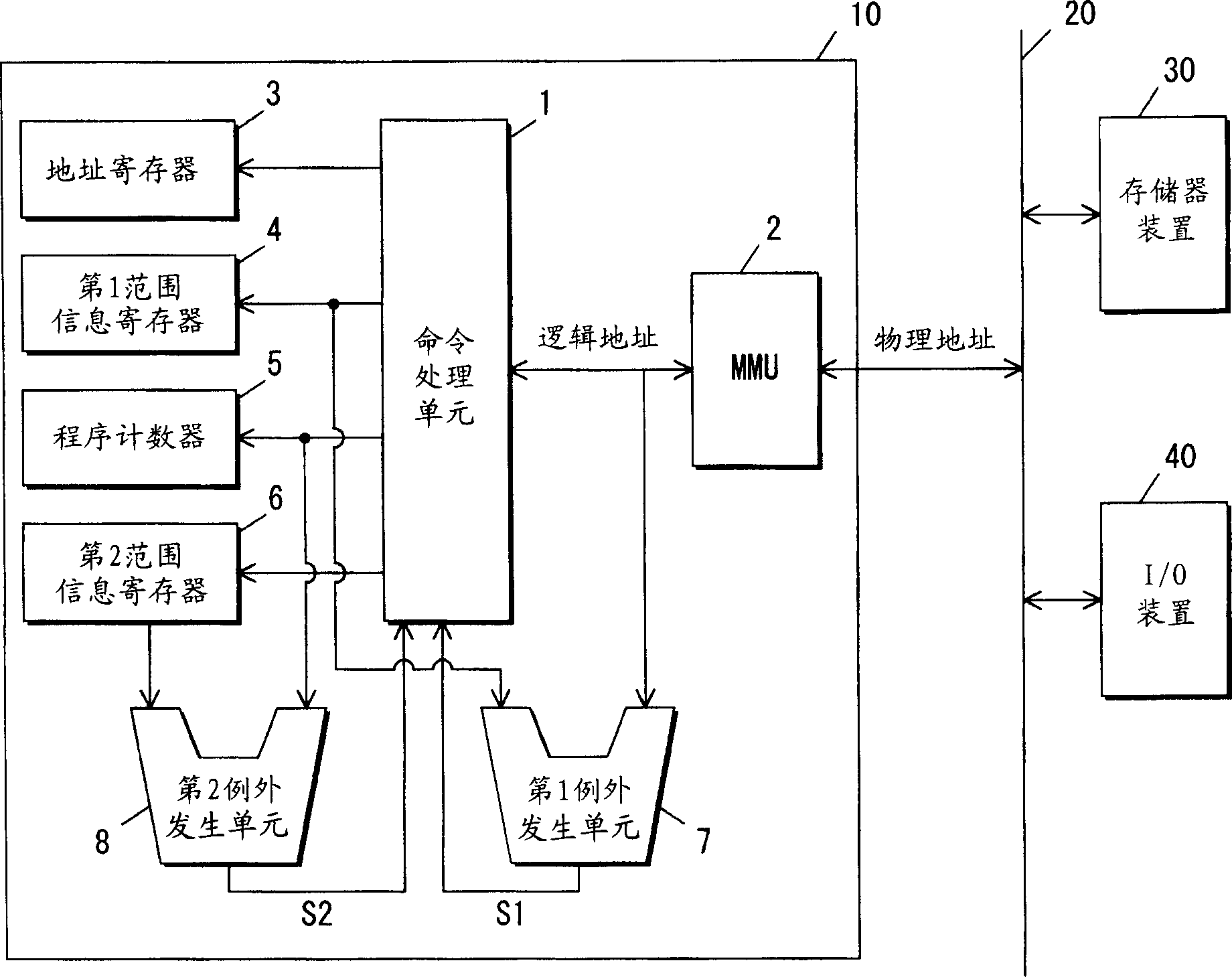

[0099] This aspect relates to a processor device. figure 1 It is a block diagram of the processor device according to Embodiment 1 of the present invention.

[0100] Such as figure 1 As shown, the processor device 10 is connected to a memory device 30 and an I / O device 40 etc. via a bus 20 . Also, the processor device 10 is equipped with the following structural components.

[0101] The command processing unit 1 reads in and sequentially executes the program on the memory device 30 via the bus 20 , and performs input and output with the I / O device 40 .

[0102] Here, in this mode, an MMU (memory management unit) is set between the command processing unit 1 and the bus 20, the command processing unit 1 and the MMU2 use logical addresses for input and output, and the MMU2 performs logical address / physical address conversion, but For example, the MMU may be omitted, and the command processing unit 1 may input and output physical addresses.

[0103] Furthermore, in the process...

Embodiment approach 2

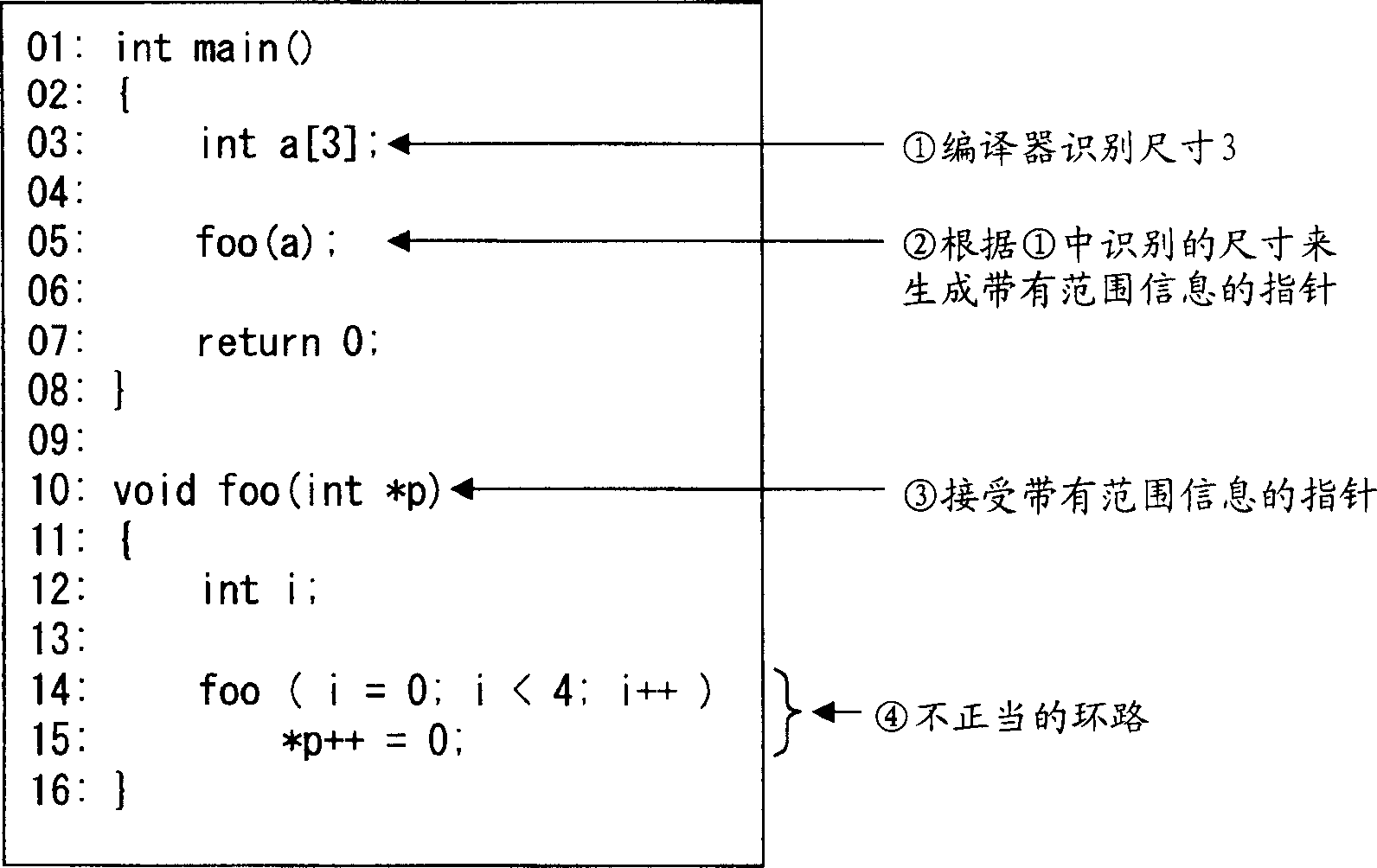

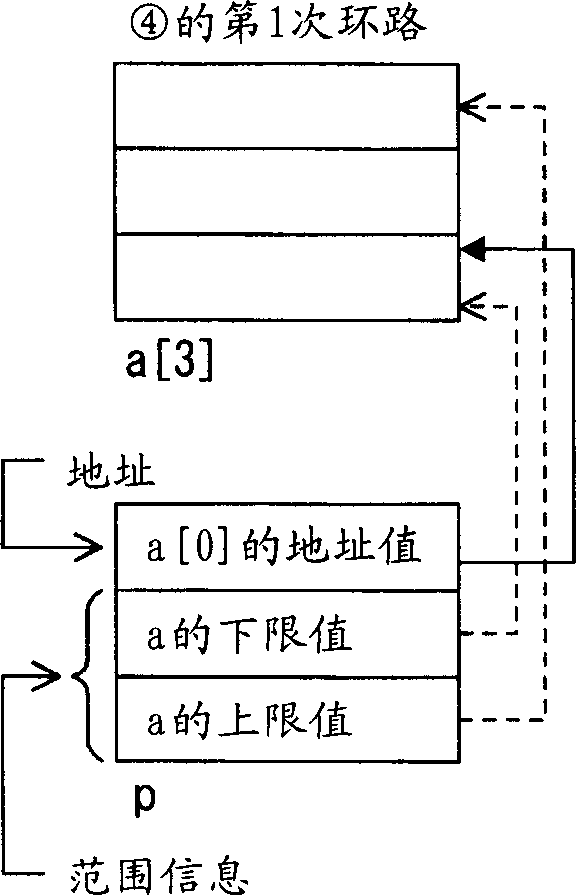

[0156] This method involves figure 1 The shown compiling device based on the address register 3 and the first range information register 4 supports pointers with range information. In addition, in the case of generating executable code from source code, methods such as compiling and linking are usually combined according to stages, but in this specification, a series of methods from source code to generation of executable code are collectively referred to as compile.

[0157] image 3 is a block diagram of a compiling device according to Embodiment 2 of the present invention. Of course, the compiling device 51 shown in FIG. 2 generates the execution code 60 from the source code 52 described in a programming language (for example, c / c++ language, Pascal, etc.) that can directly manipulate pointers.

[0158] In this source code 52, as described in Embodiment 1, pointers with range information are used, so no special description is required.

[0159] In FIG. 2 , the source an...

Embodiment approach 3

[0178] This method involves figure 1 The illustrated compiling device is supported by a pair of a program counter 5 and a second range information register 6 to perform range protection of address values.

[0179] Figure 5 is a block diagram of a compiling device according to Embodiment 3 of the present invention. Such as Figure 5 As shown, the compiling device 71 generates an execution code 81 based on the source code 72 described in the same programming language as in the second embodiment, and includes the main components described below.

[0180] The source analyzing unit 73 determines the forwarding destination of the code according to the discrimination condition. The function code range is stored in the function code range storage memory 79 . In the execution code memory 78, the generated execution code is stored.

[0181] The function code range analysis unit 74 analyzes the function code range in the execution code memory 78 when the source analysis unit 73 det...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More