Method for forming grid electrode of semiconductor

A semiconductor and gate technology, applied in the field of semiconductor device formation, can solve problems that affect reliability, failure, and reduce gate coupling rate, so as to prevent reliability, increase gate coupling rate, and expand error margins. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 2 example

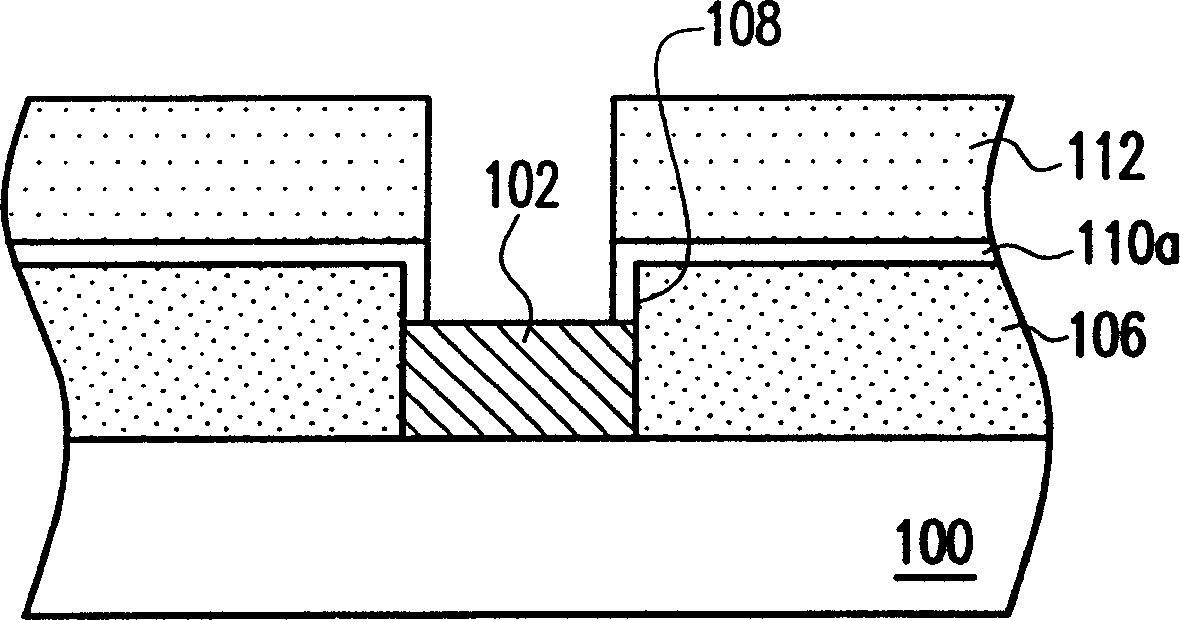

[0030] Figure 2A to Figure 2E It is a sectional view of the manufacturing process of the floating gate of the flash memory according to a second embodiment of the present invention.

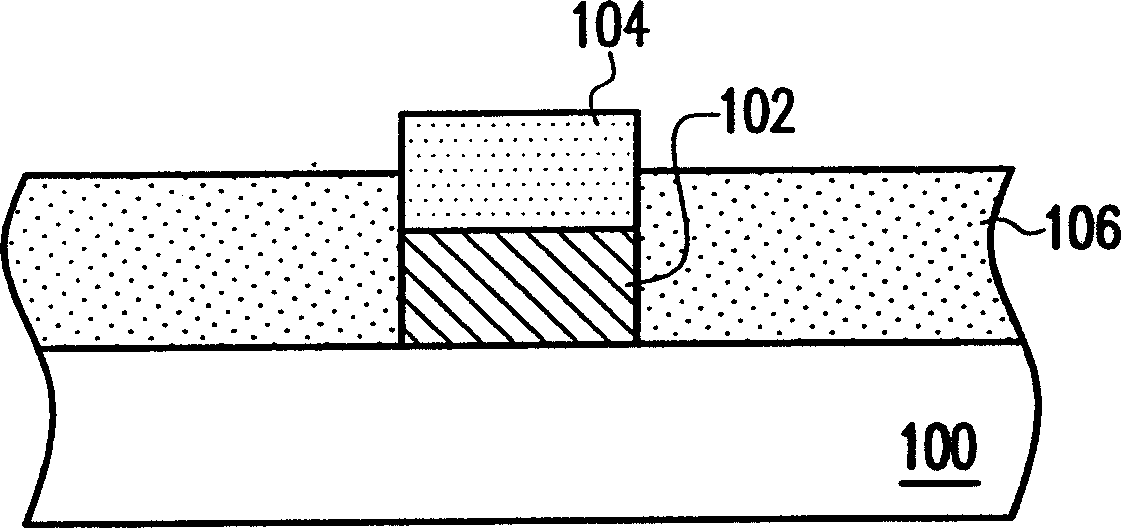

[0031] Please refer to Figure 2A , forming a stack structure comprising a conductor layer 202 and a top cover layer 204 on a substrate 200, wherein the conductor layer 202 is, for example, a polysilicon layer, and the top cover layer 204 is, for example, a silicon nitride layer, and the substrate 200 and the conductor A tunnel oxide layer (not shown) is also included between the layers 202 . Then, a high-density plasma dielectric layer 206 is formed on the substrate 200 and the top cover layer 204 is exposed, wherein the top of the high-density plasma dielectric layer 206 is higher than the top of the conductive layer 202, and its material is, for example, selected from silicon oxide ethnic groups.

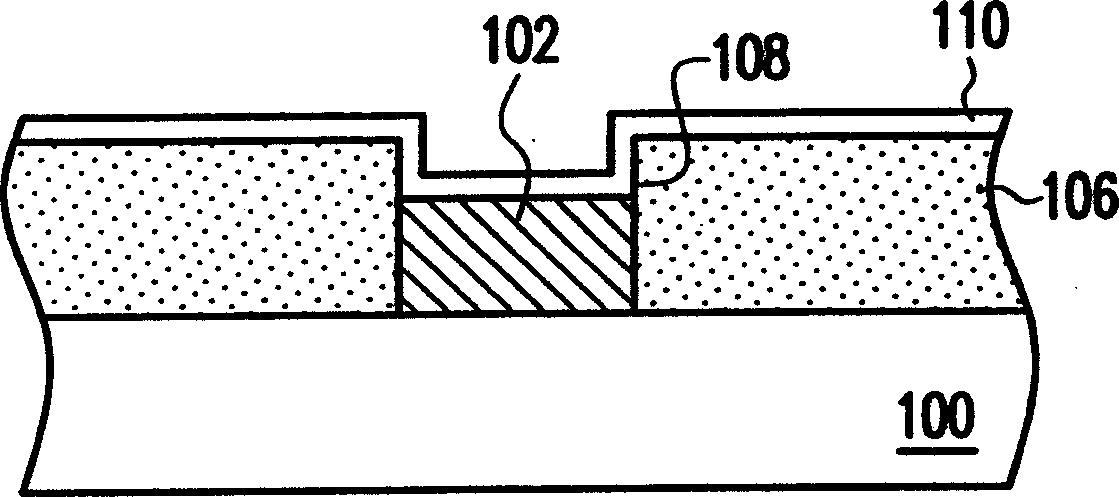

[0032] Then, please refer to Figure 2B , use such as hot phosphoric acid to cover the top ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com