Digital lock phase ring for producing multiple frequency point clock signal using one time delay chain

A technology of digital phase-locked loop and clock signal, which is applied to the automatic control of power and electrical components, etc., which can solve the problems of reducing clock precision and increasing the occupied area, and achieve the effect of improving precision and saving chip area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

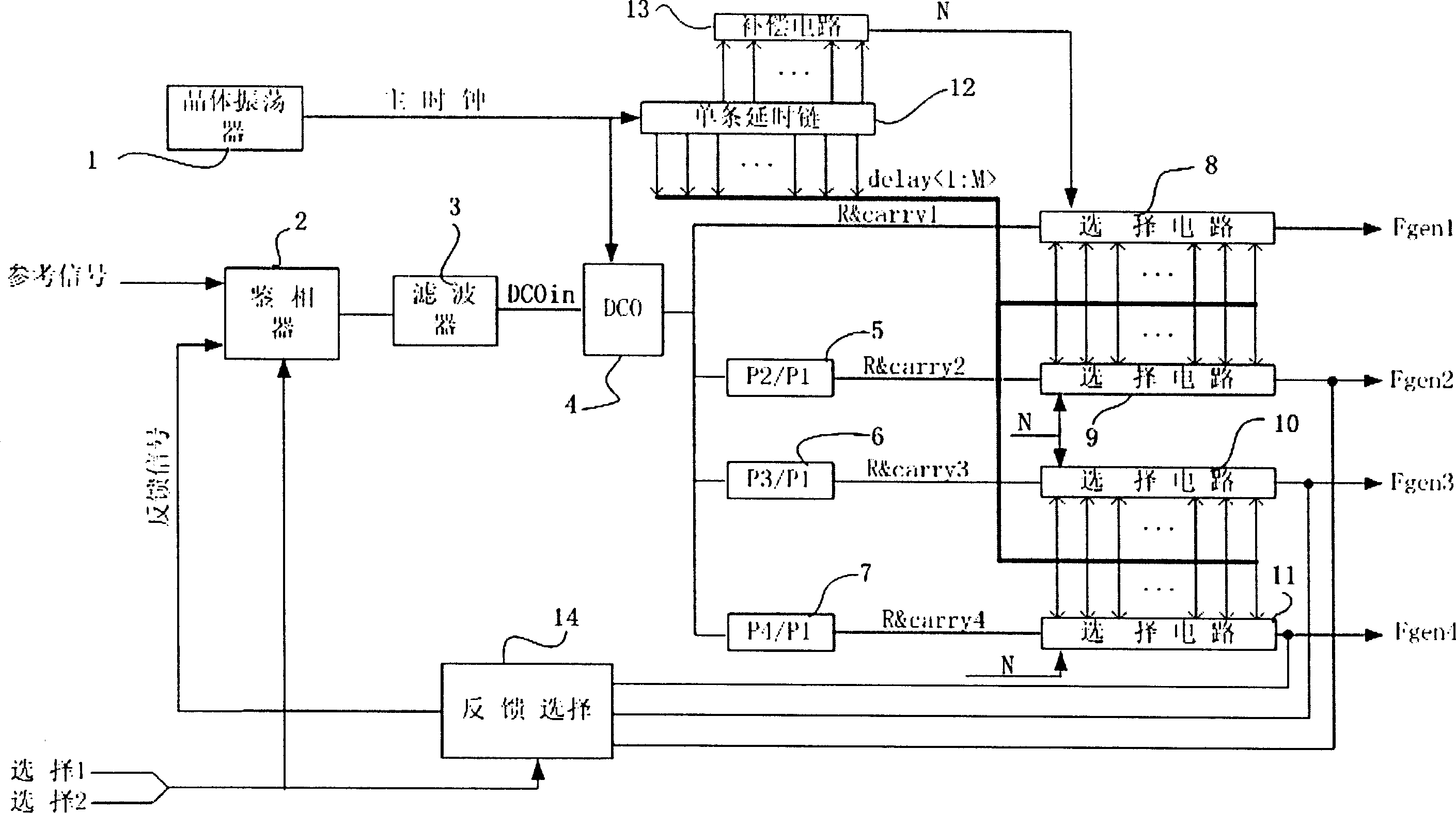

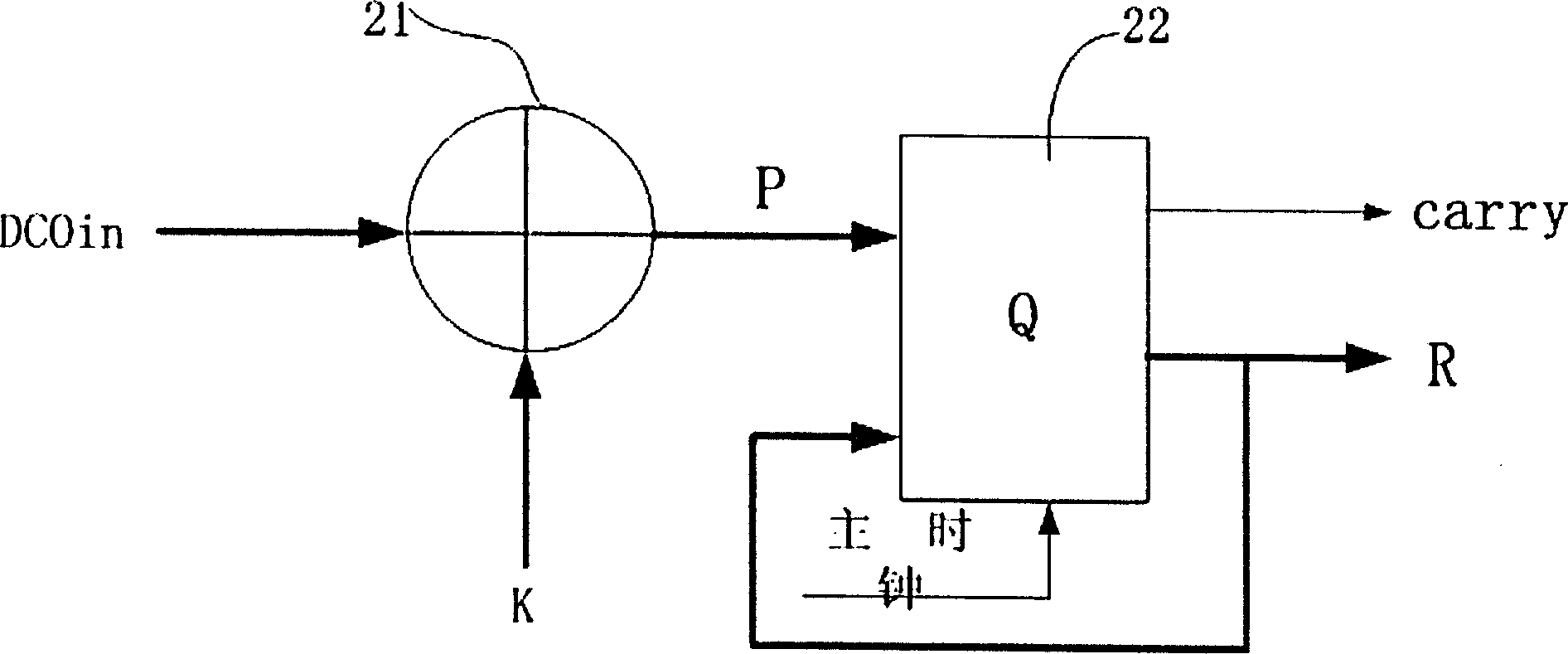

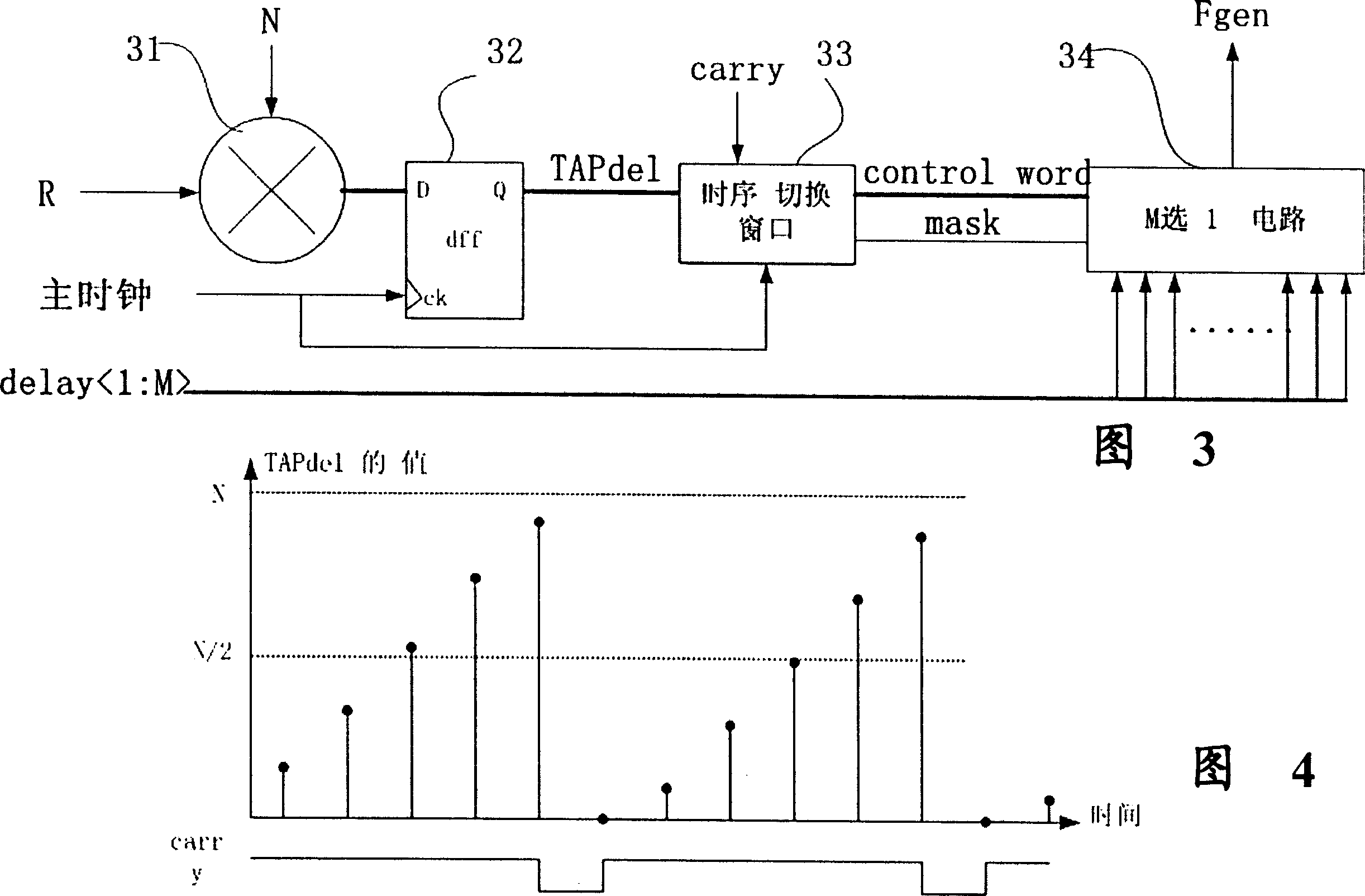

[0024] A digital phase-locked loop that uses a delay chain to generate multiple frequency point clock signals. The digital phase-locked loop can use at least one input signal as a reference to attenuate the jitter of the input signal to generate one or more relatively stable clock signals. , which includes: a) phase detection filter circuit, which compares the difference between the output clock and the reference signal, and filters out high-frequency components; b) digitally controlled oscillator (DCO for short); c) a crystal oscillator that provides the main clock; d) A delay chain with taps is composed of multiple stages of the same delay units in series; e) compensation circuit to eliminate the influence of temperature and process deviation on the characteristics of the delay chain; f) selection circuit, each of the delay chain can be Stage delay selected output.

[0025] The local main clock generated by the crystal oscillator is sent to the delay chain, and the control w...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More