Method of utilizing focused ion beam in exposing required layer in failure analysis of multilayer semiconductor

A focused ion beam, semiconductor technology, applied in the field of failure analysis, can solve the problems of easy damage, low defect detection rate, troublesome and expensive

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] Reference numerals are added to the drawings to describe the embodiments of the present invention in detail. In all drawings, the same or similar elements will be represented by the same reference numerals as much as possible.

[0016] According to the present invention, there is provided a method for exposing a target layer of a multilayer semiconductor device, mainly by stripping at least one upper layer above the target layer by using a focused ion beam.

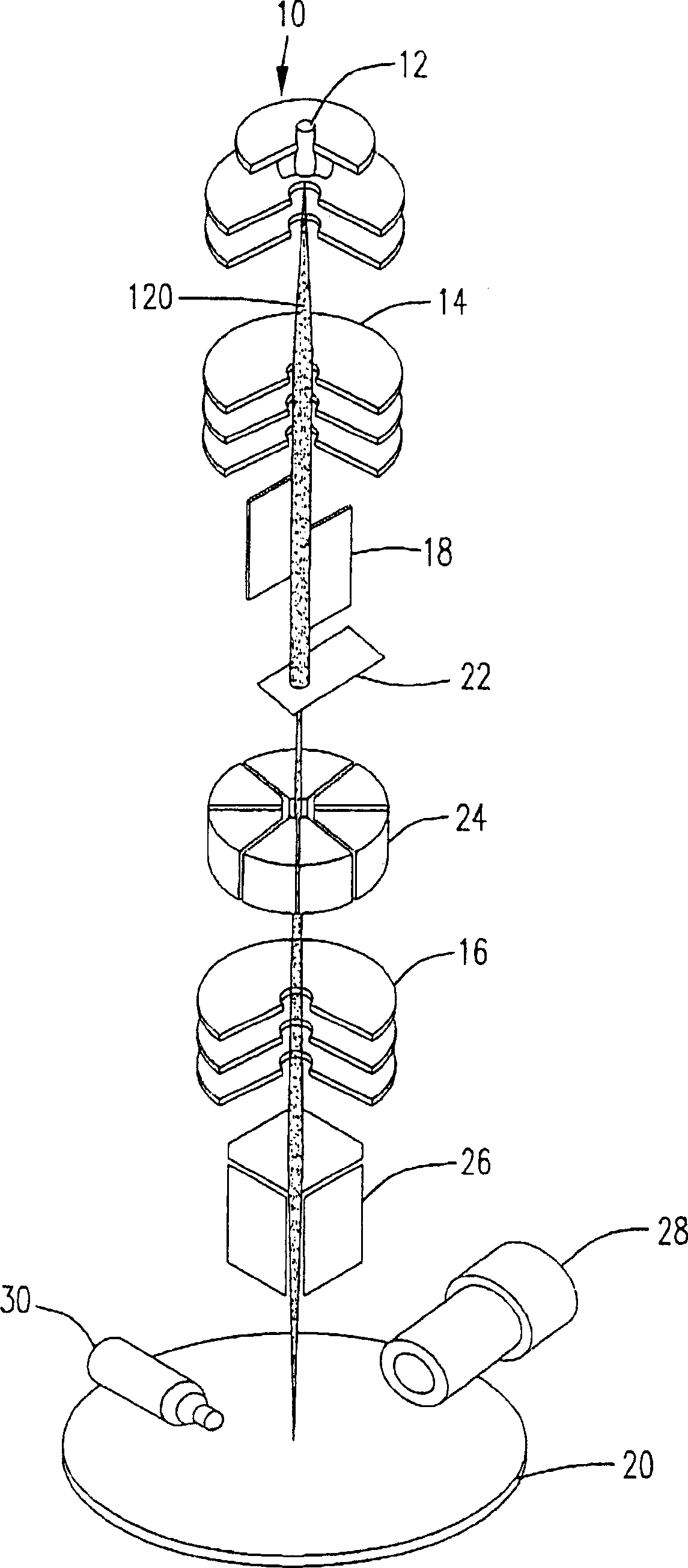

[0017] figure 1 For a description of conventional focused ion beam configurations used in the present invention, see figure 1 The focused ion beam structure 10 generally includes an ion source 12 (such as a Ga+ source), a focusing lens 14 and an objective lens 16, so that the ion beam 120 can be focused on the test piece 20 (ie, the semiconductor device herein, including a semiconductor wafer) via an ion focusing device 18 or packaged product). The focused ion beam structure 10 generally also includes an adjustab...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More