Patents

Literature

57 results about "Electrical analysis" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

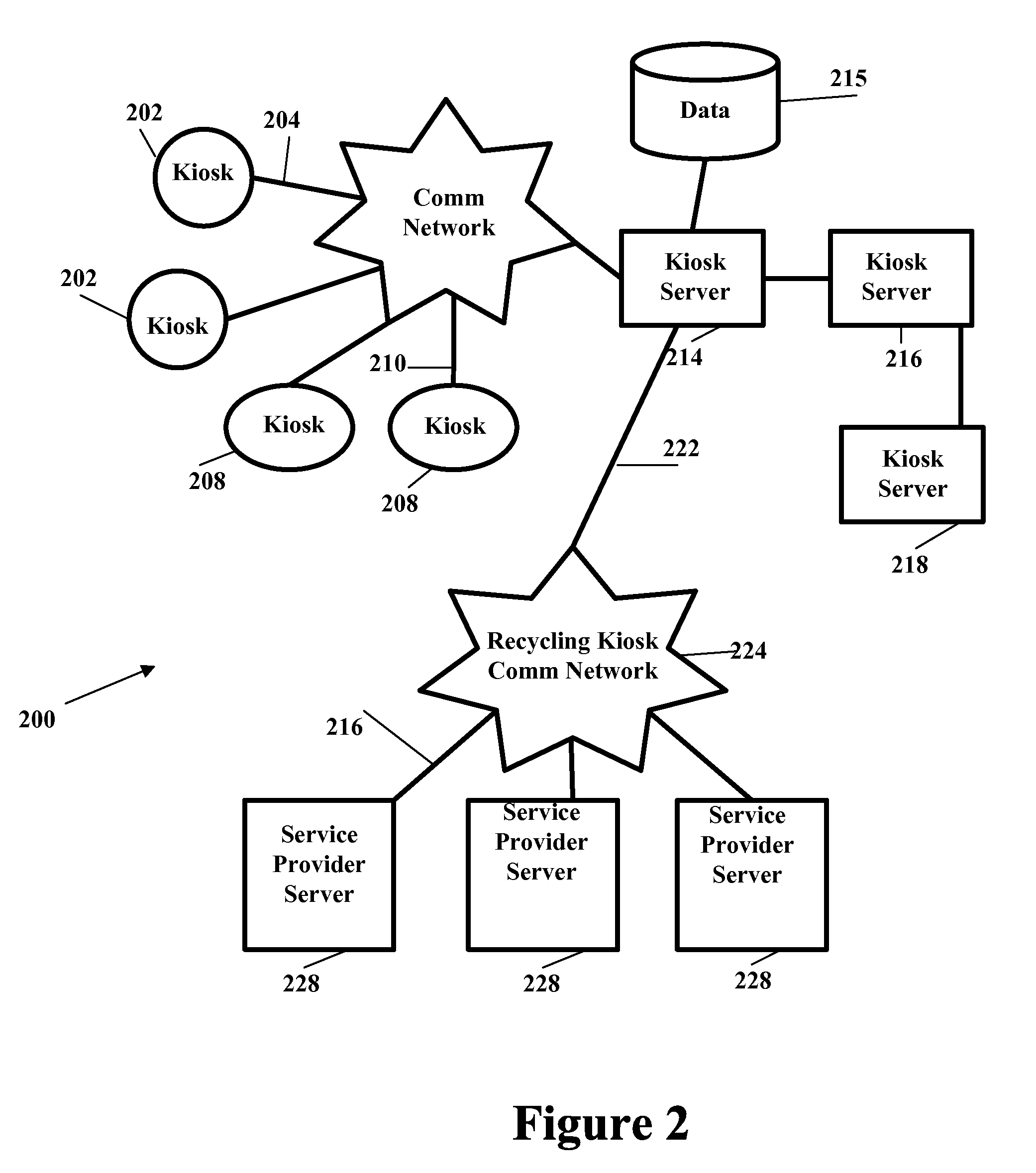

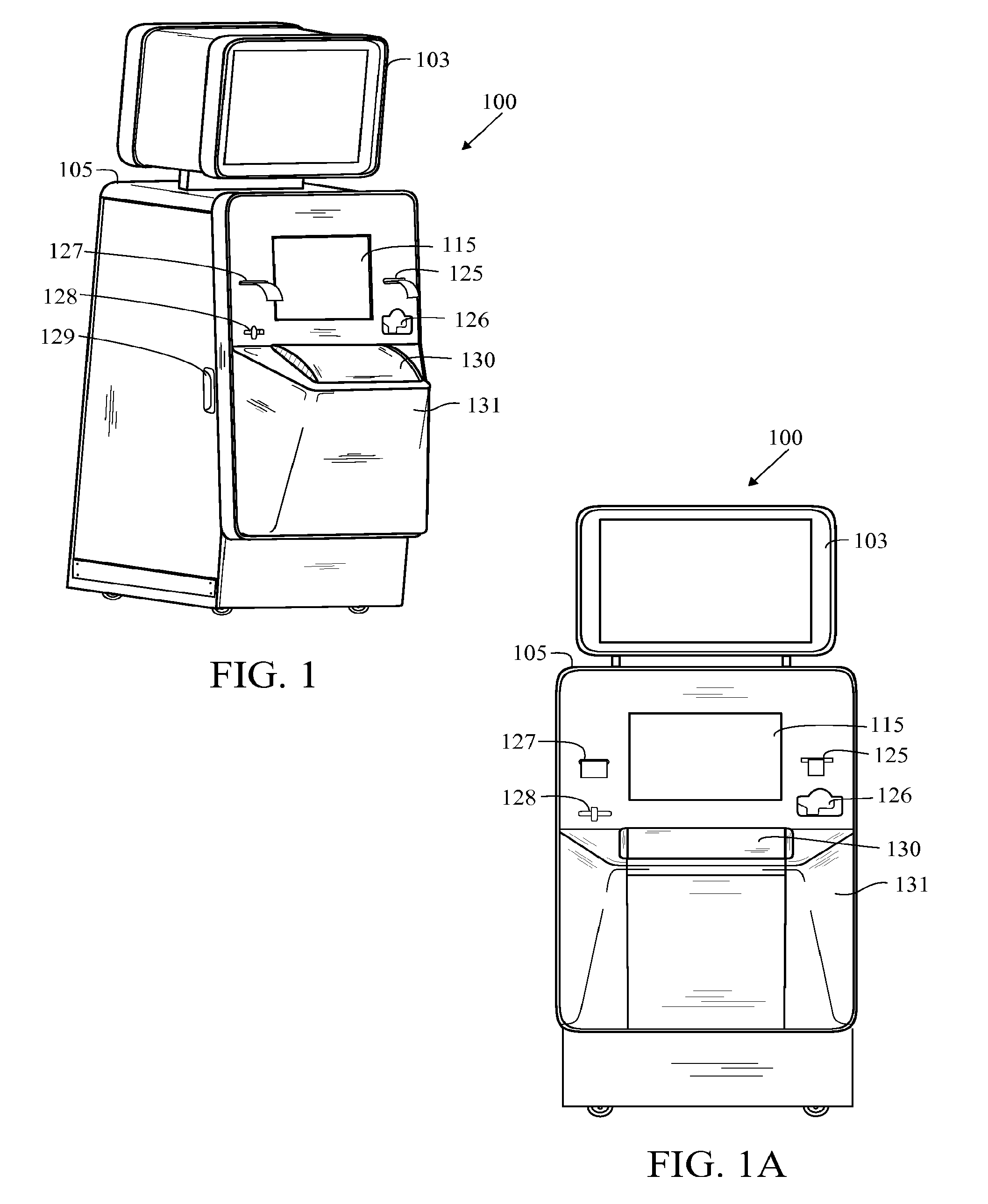

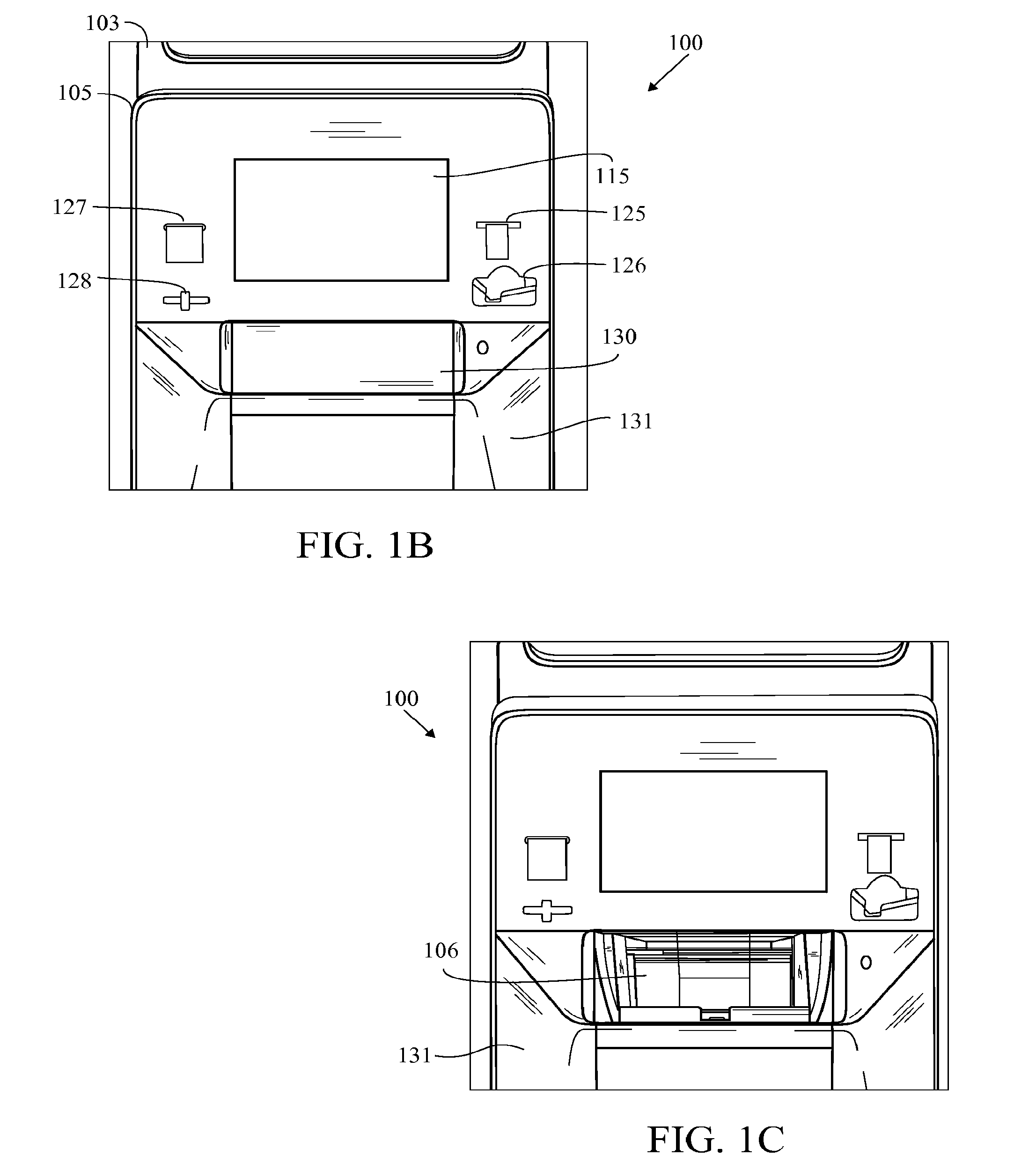

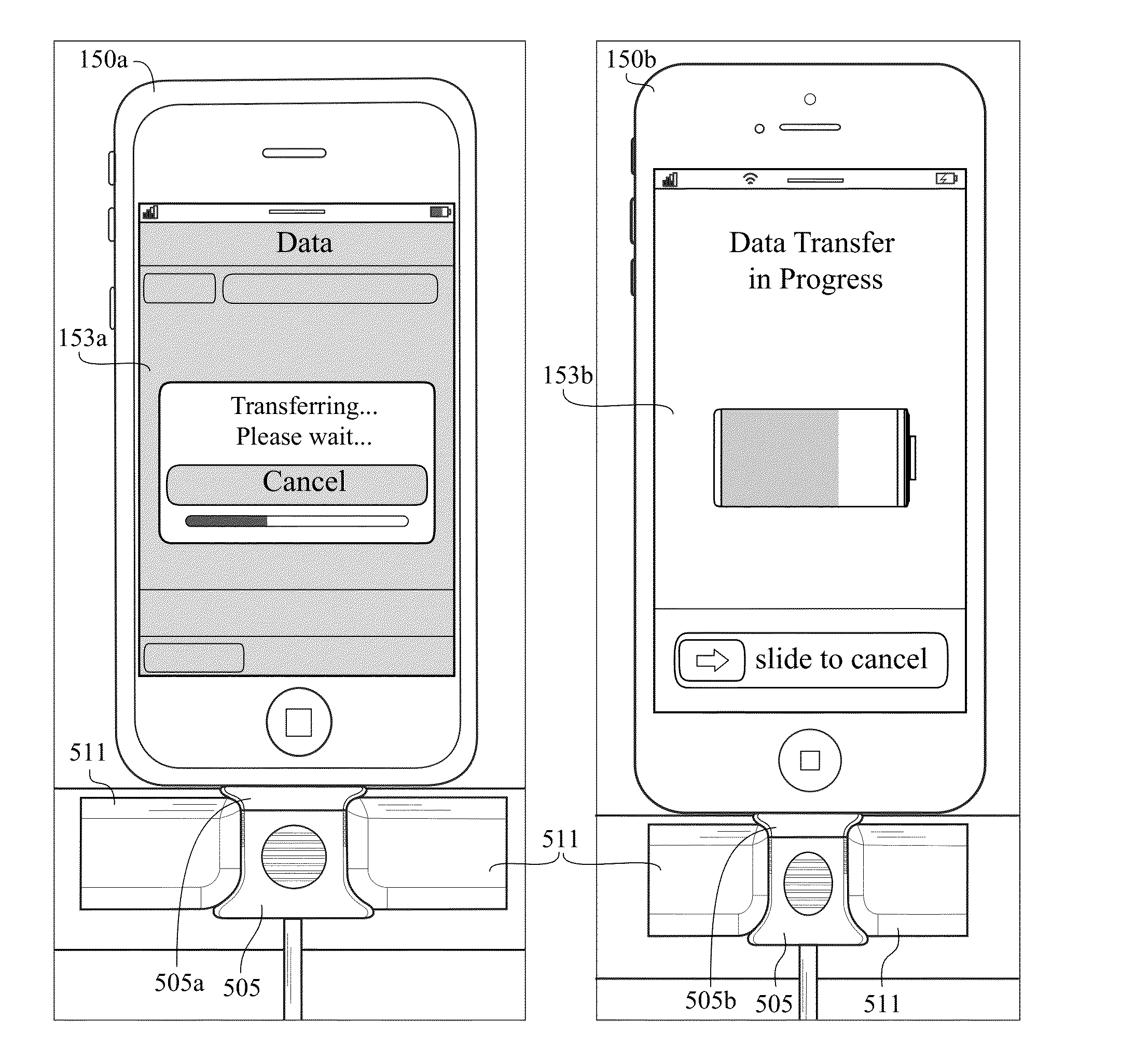

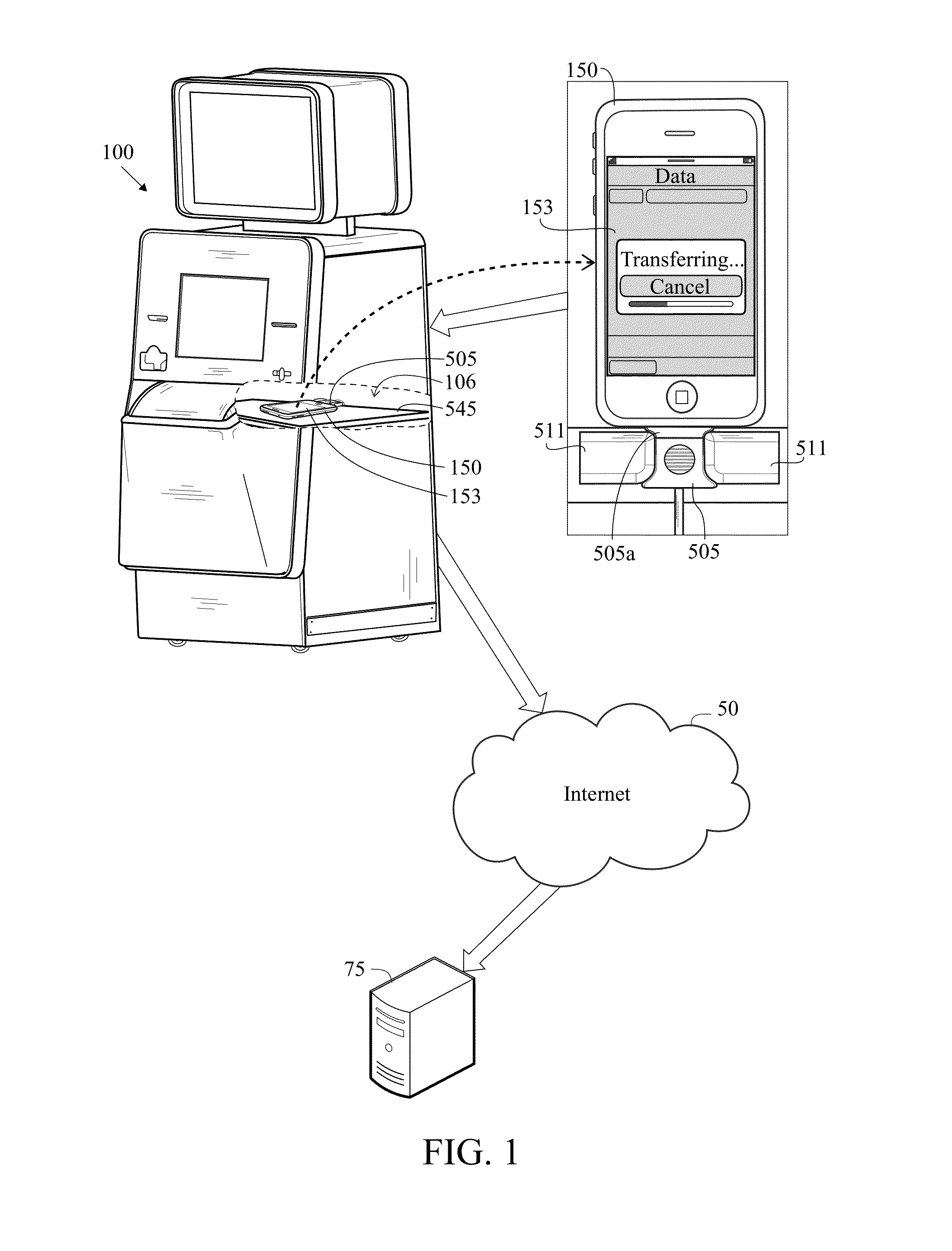

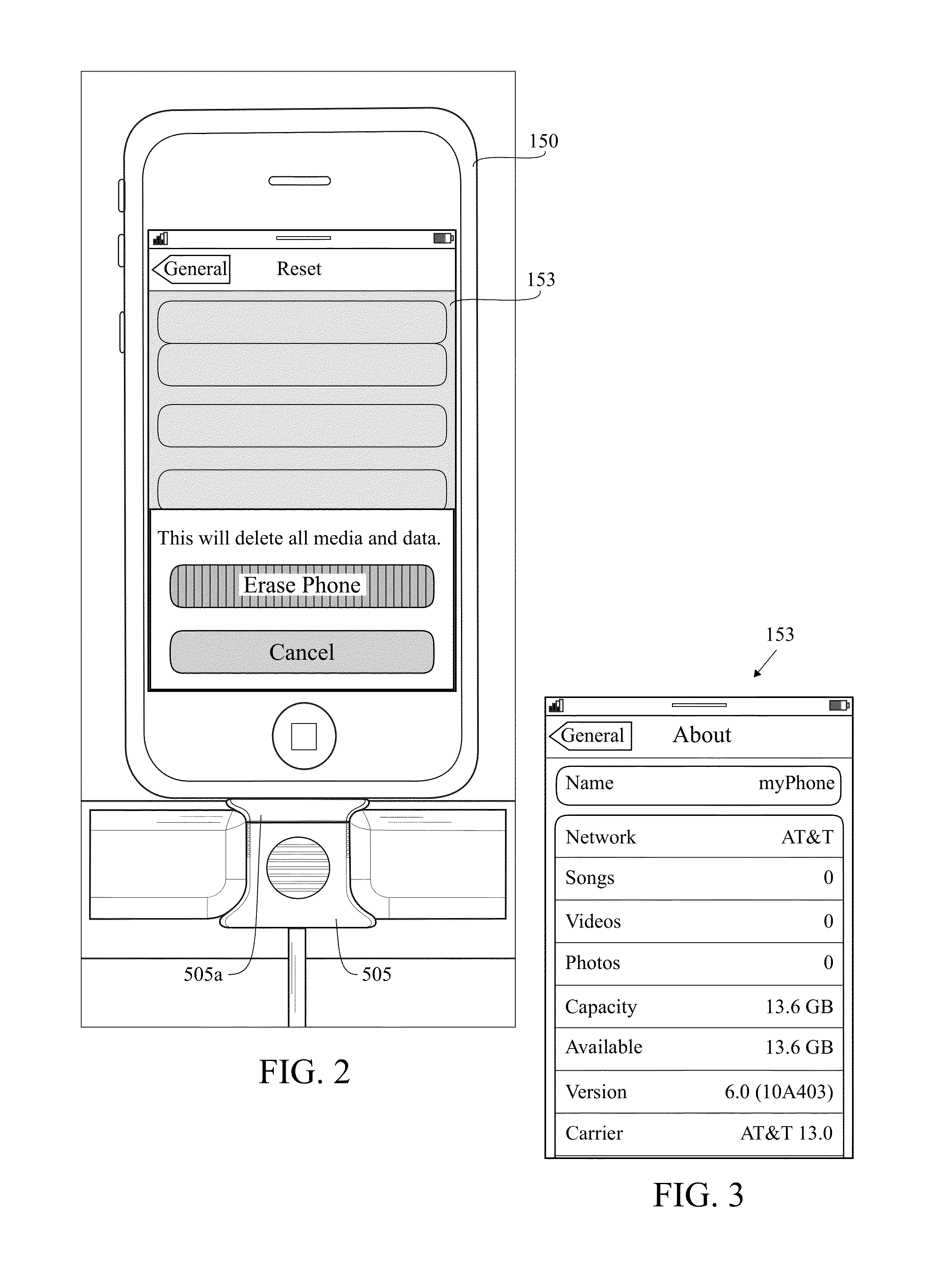

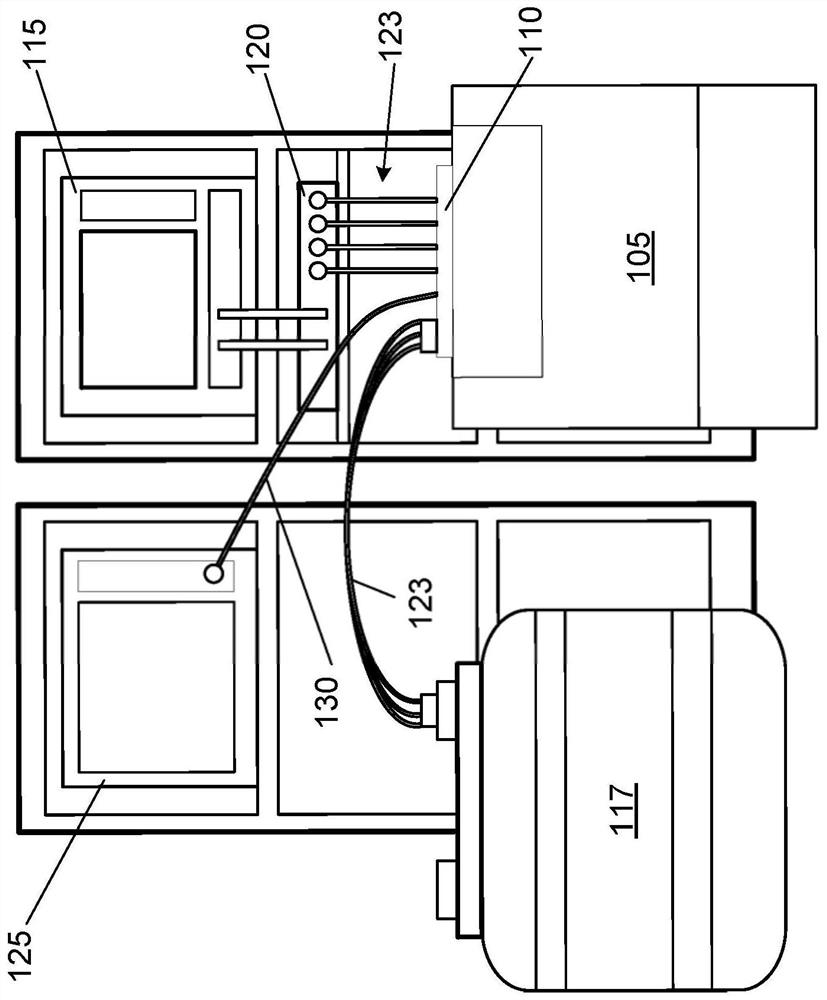

Secondary market and vending system for devices

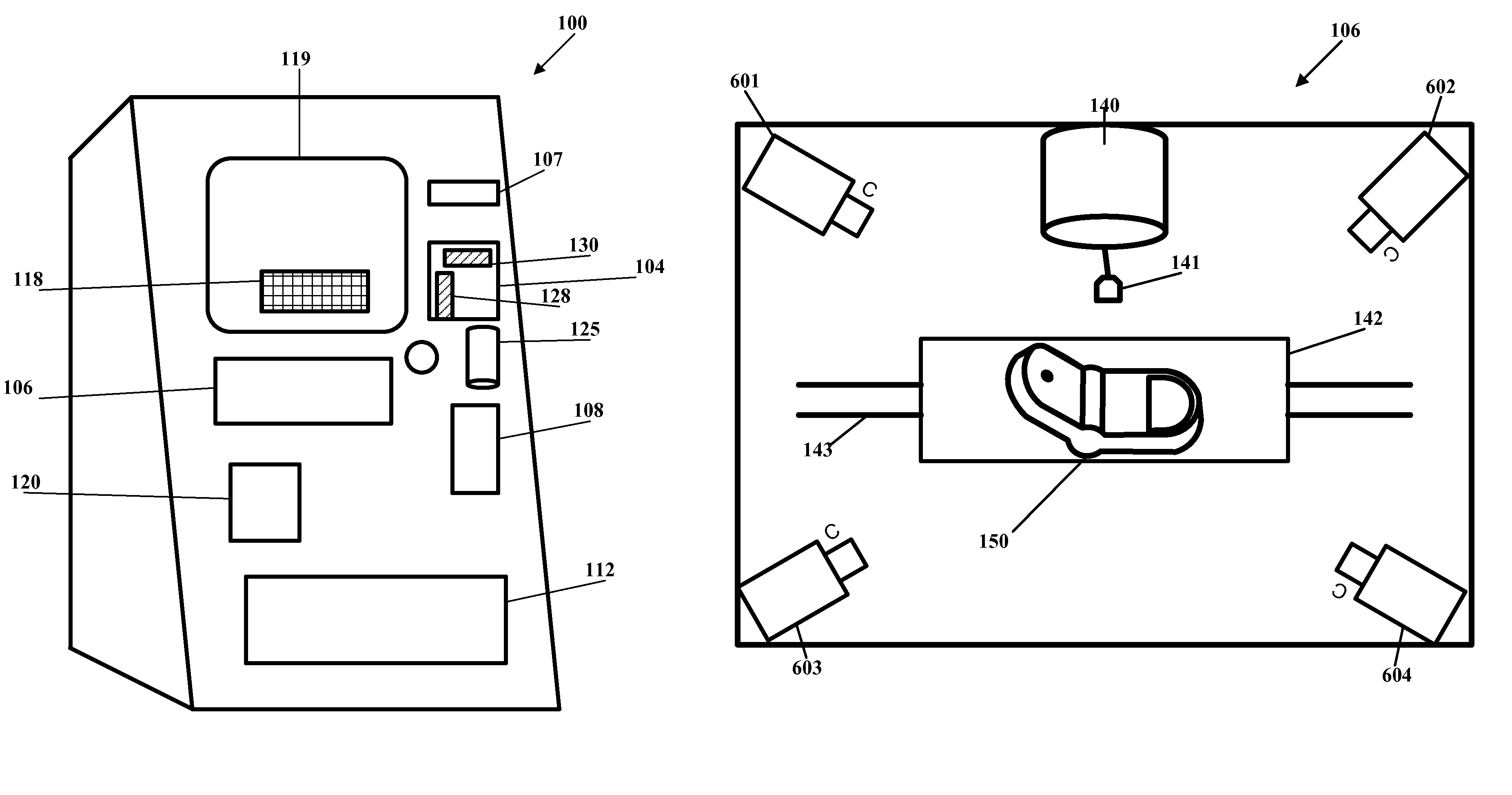

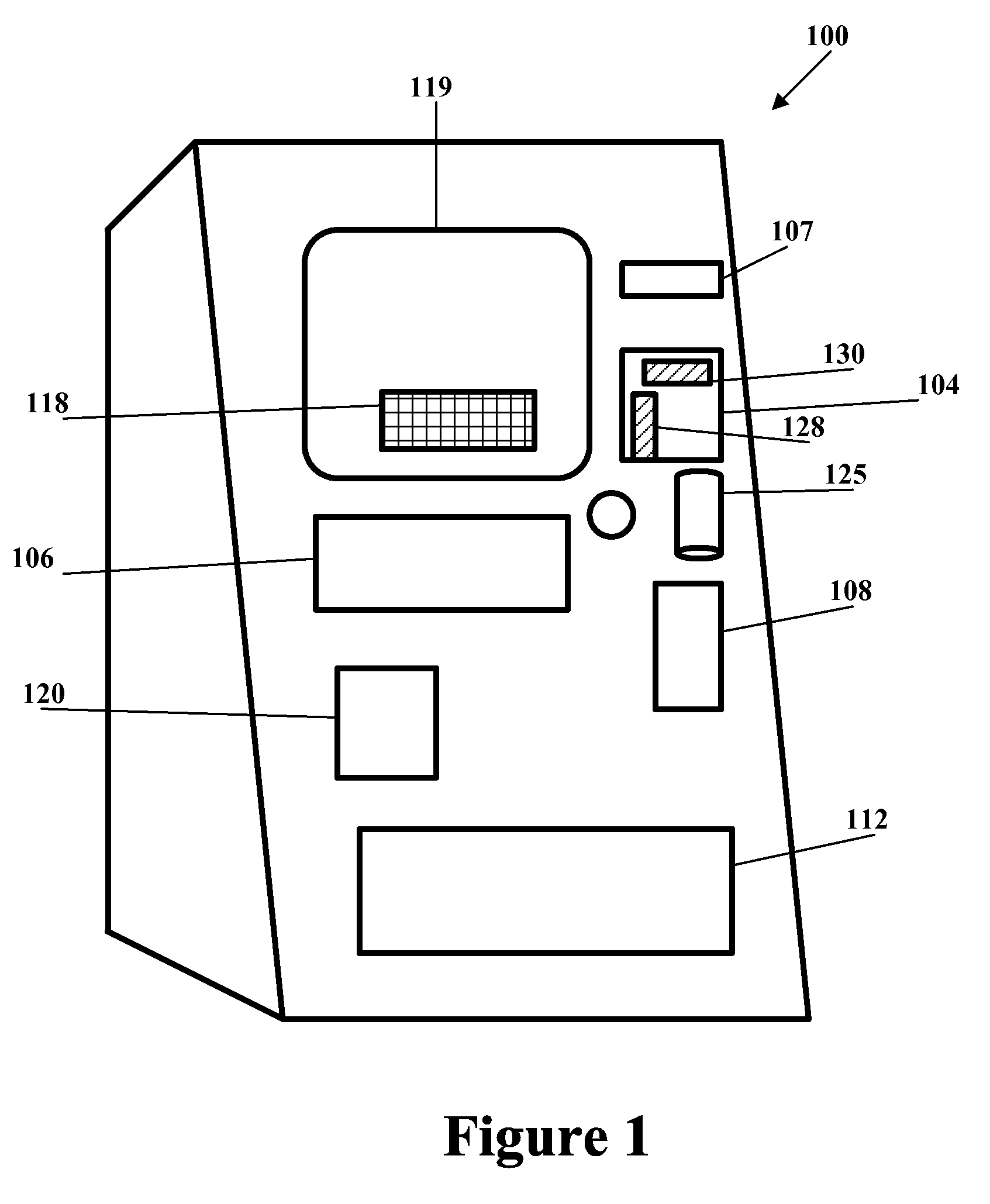

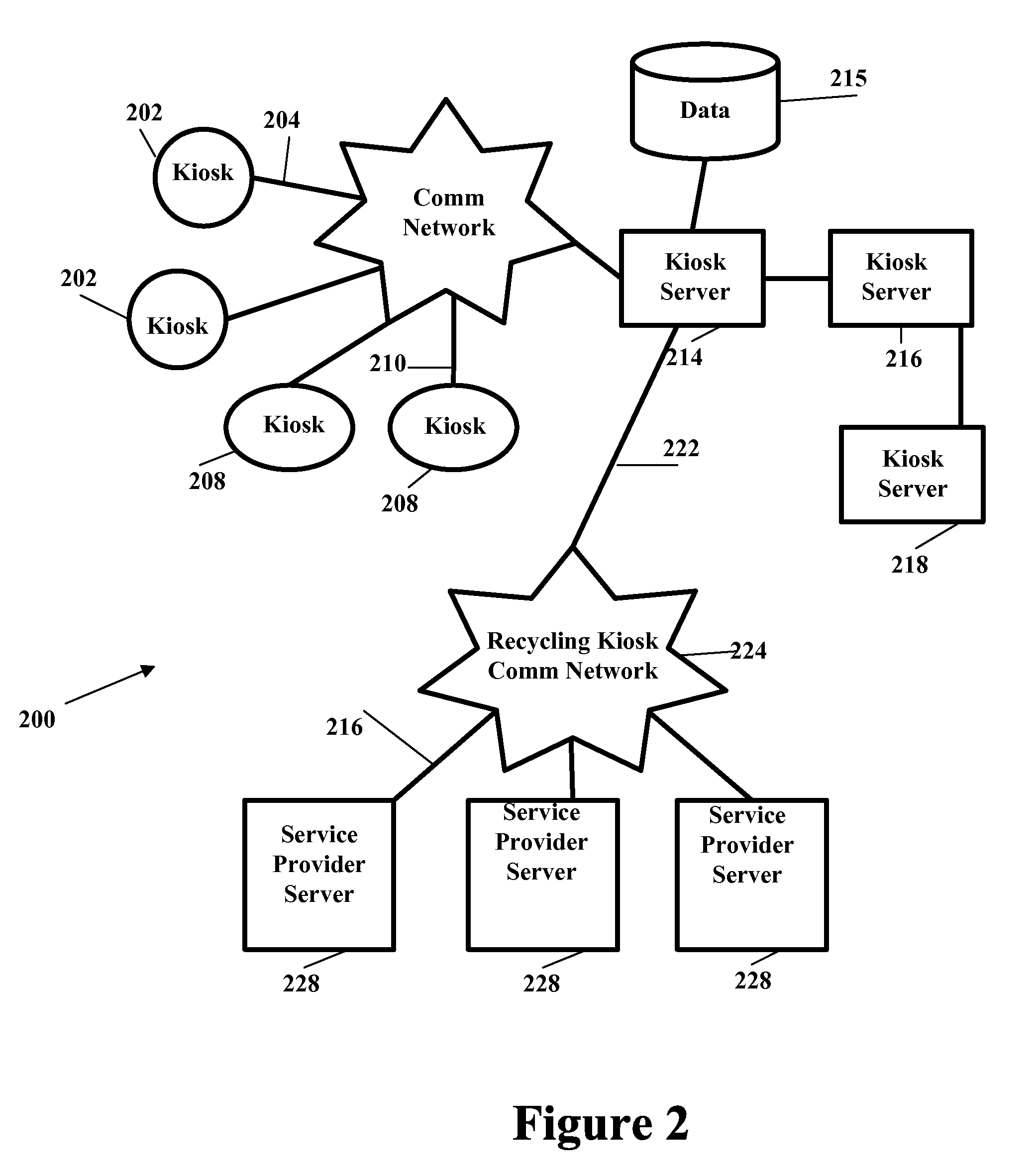

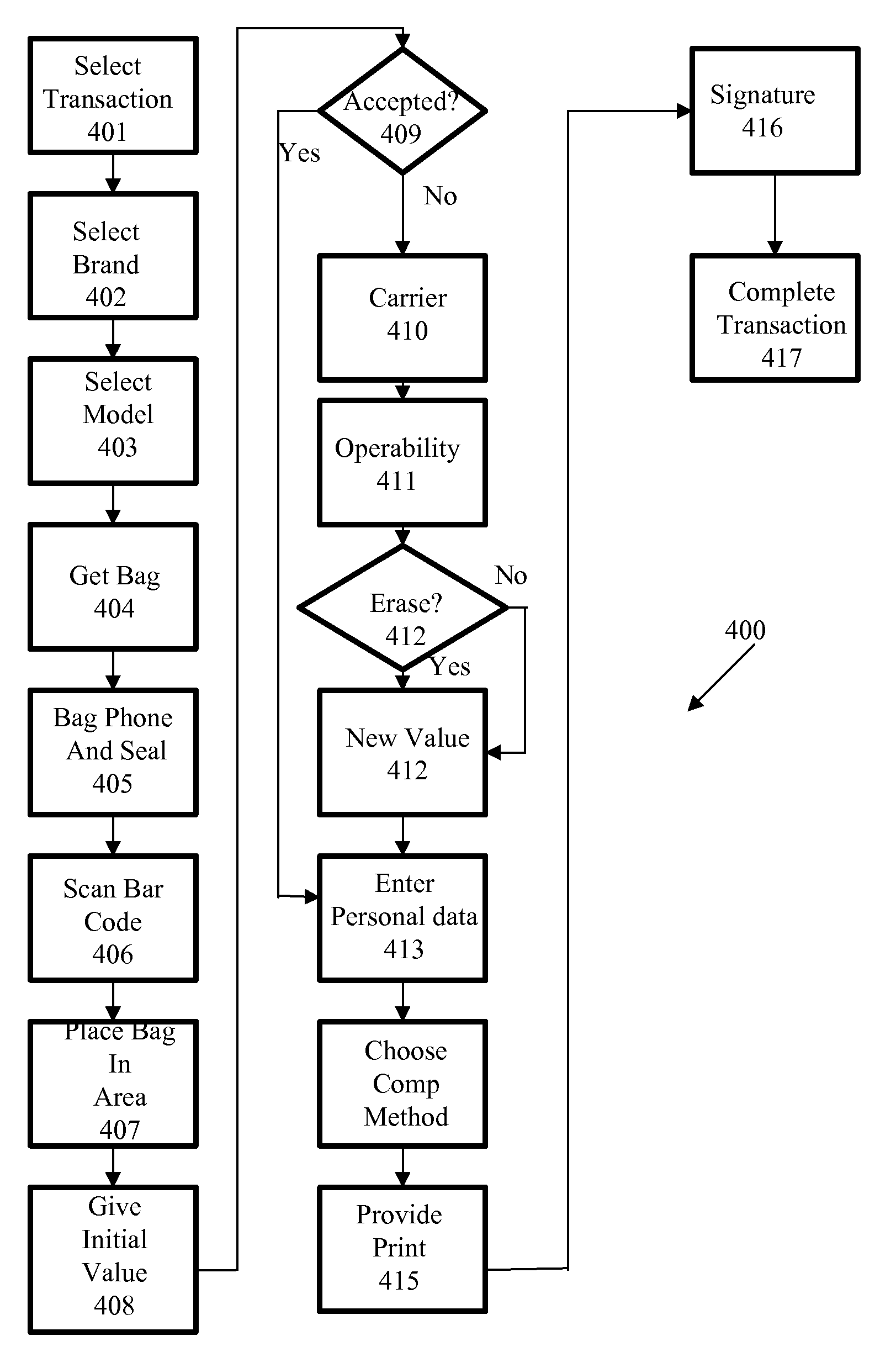

A recycling kiosk for recycling and financial remuneration for submission of a mobile telephone is disclosed herein. The recycling kiosk includes an inspection area with at least one camera and a plurality of electrical connectors in order to perform a visual analysis and an electrical analysis of the mobile telephone for determination of a value of the mobile telephone. The recycling kiosk also includes a processor, a display and a user interface.

Owner:ECOATM LLC

Secondary Market And Vending System For Devices

A recycling kiosk for recycling and financial remuneration for submission of a mobile telephone is disclosed herein. The recycling kiosk includes an inspection area with at least one camera and a plurality of electrical connectors in order to perform a visual analysis and an electrical analysis of the mobile telephone for determination of a value of the mobile telephone. The recycling kiosk also includes a processor, a display and a user interface.

Owner:ECOATM LLC

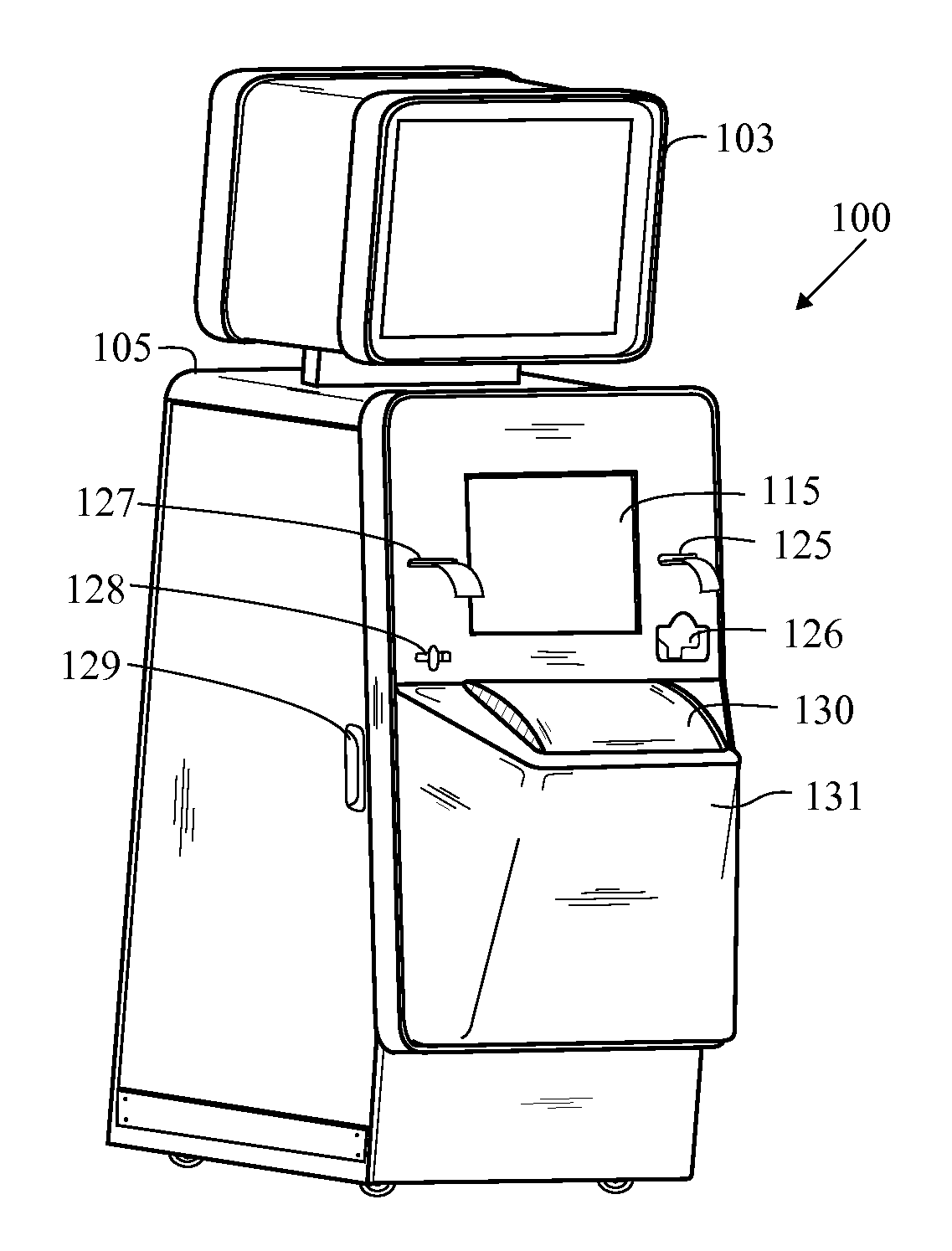

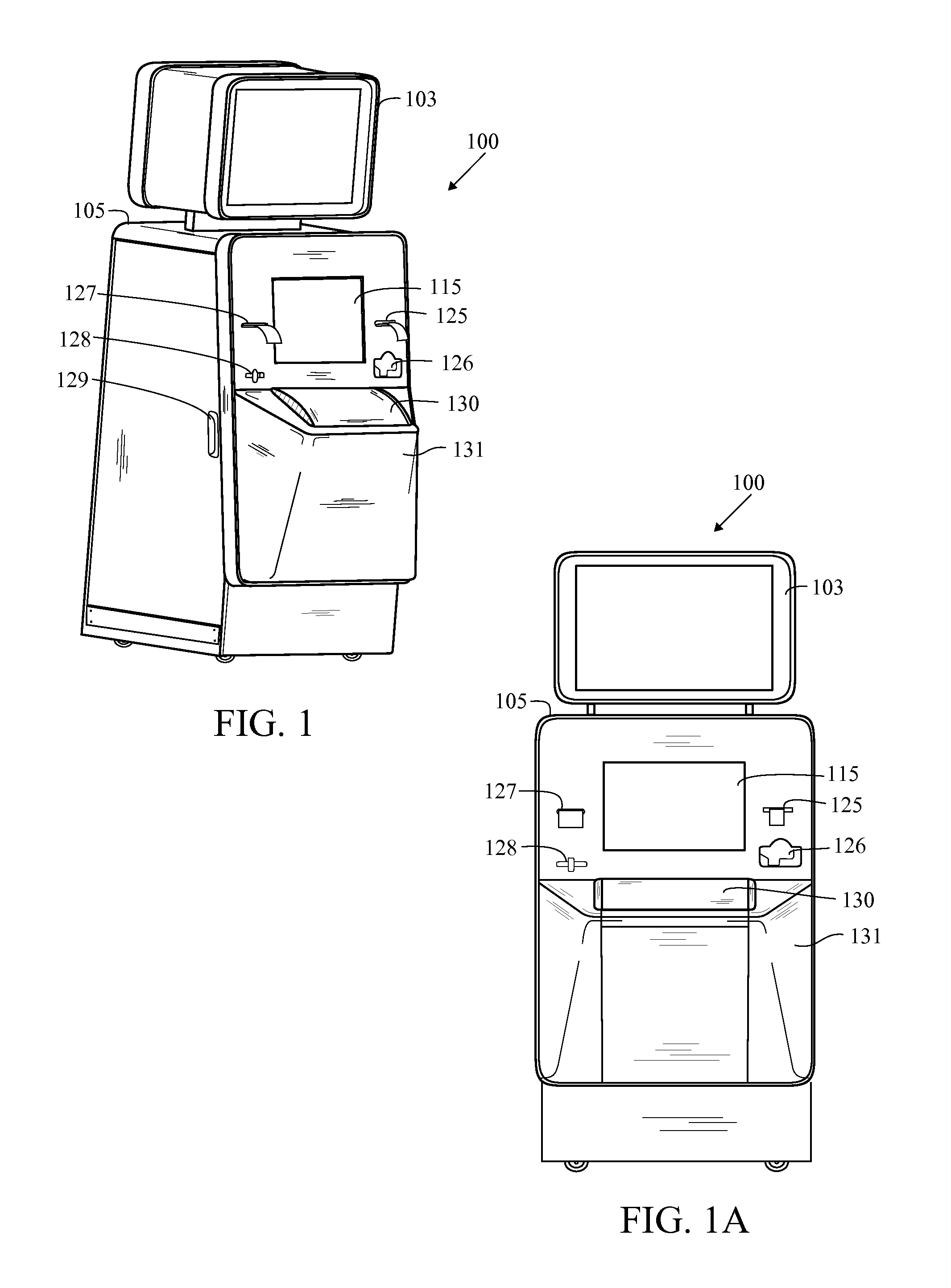

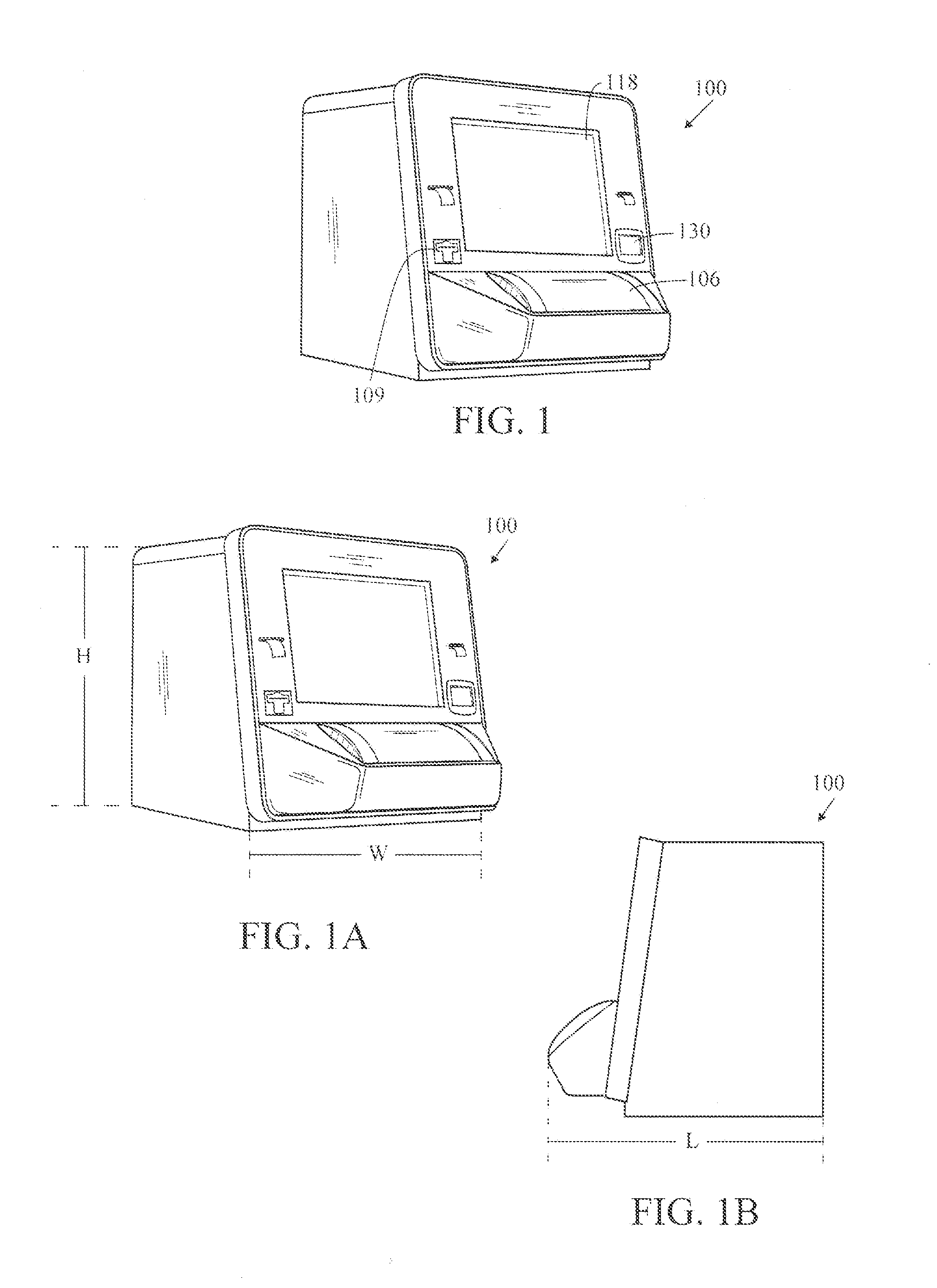

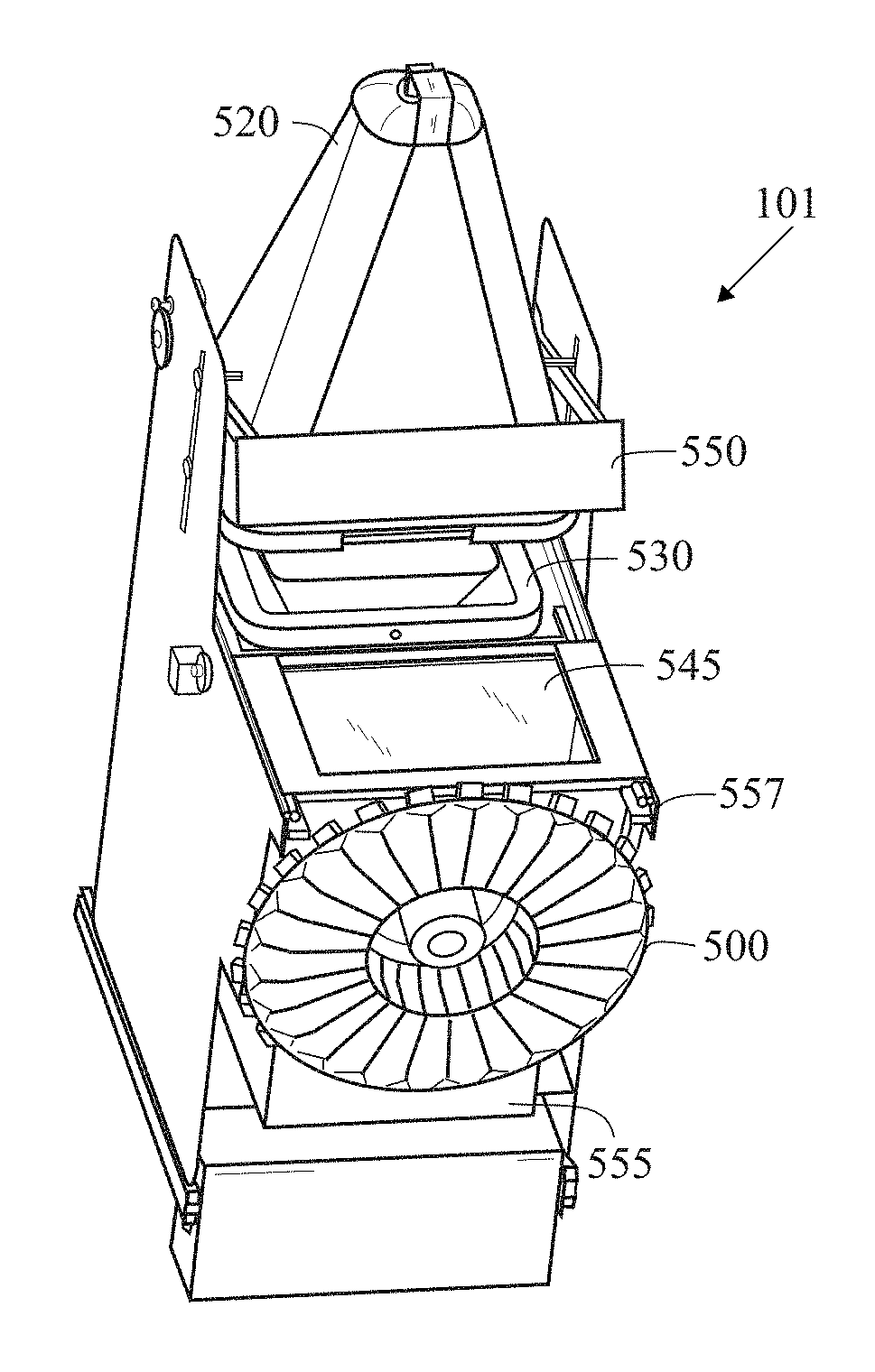

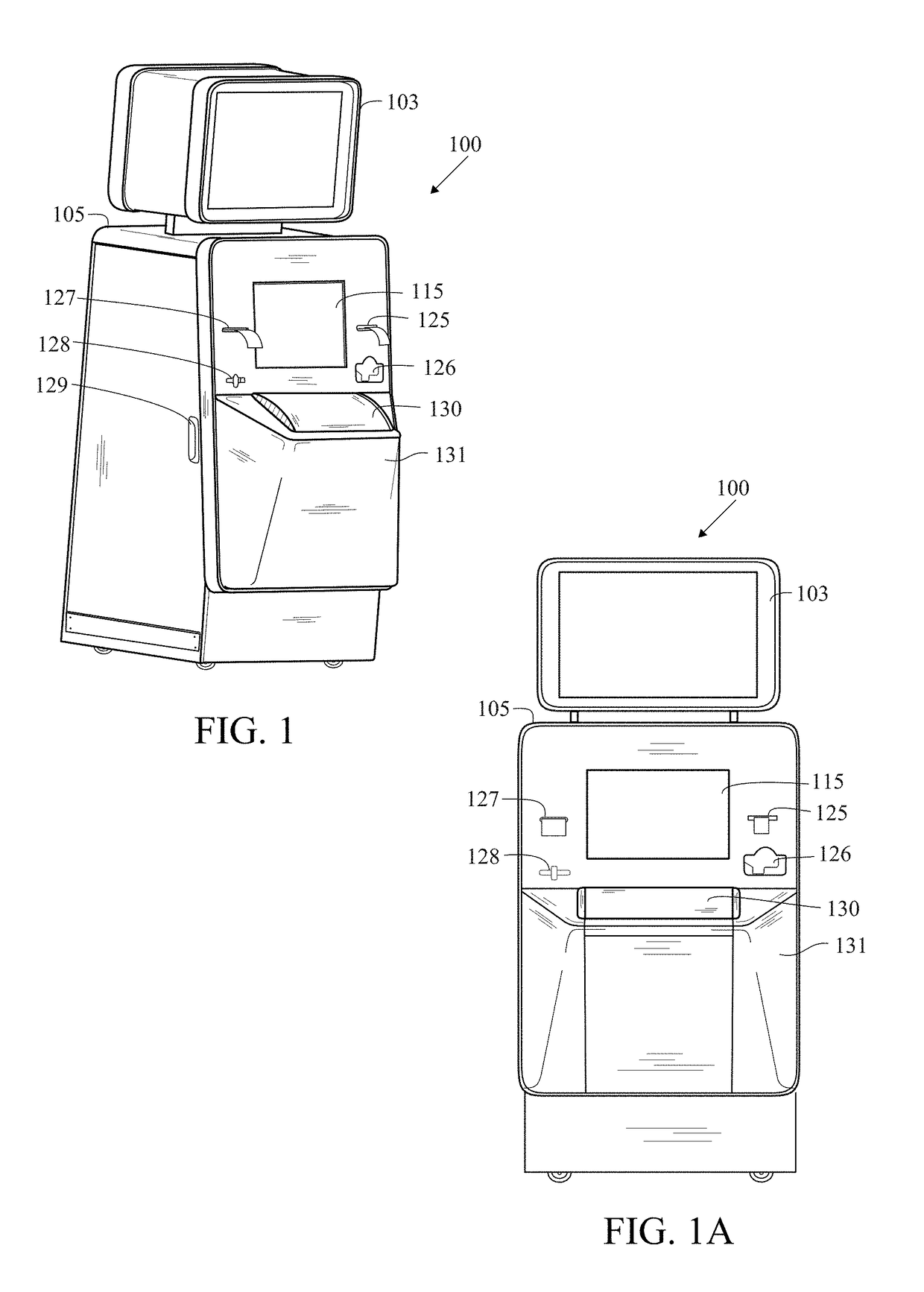

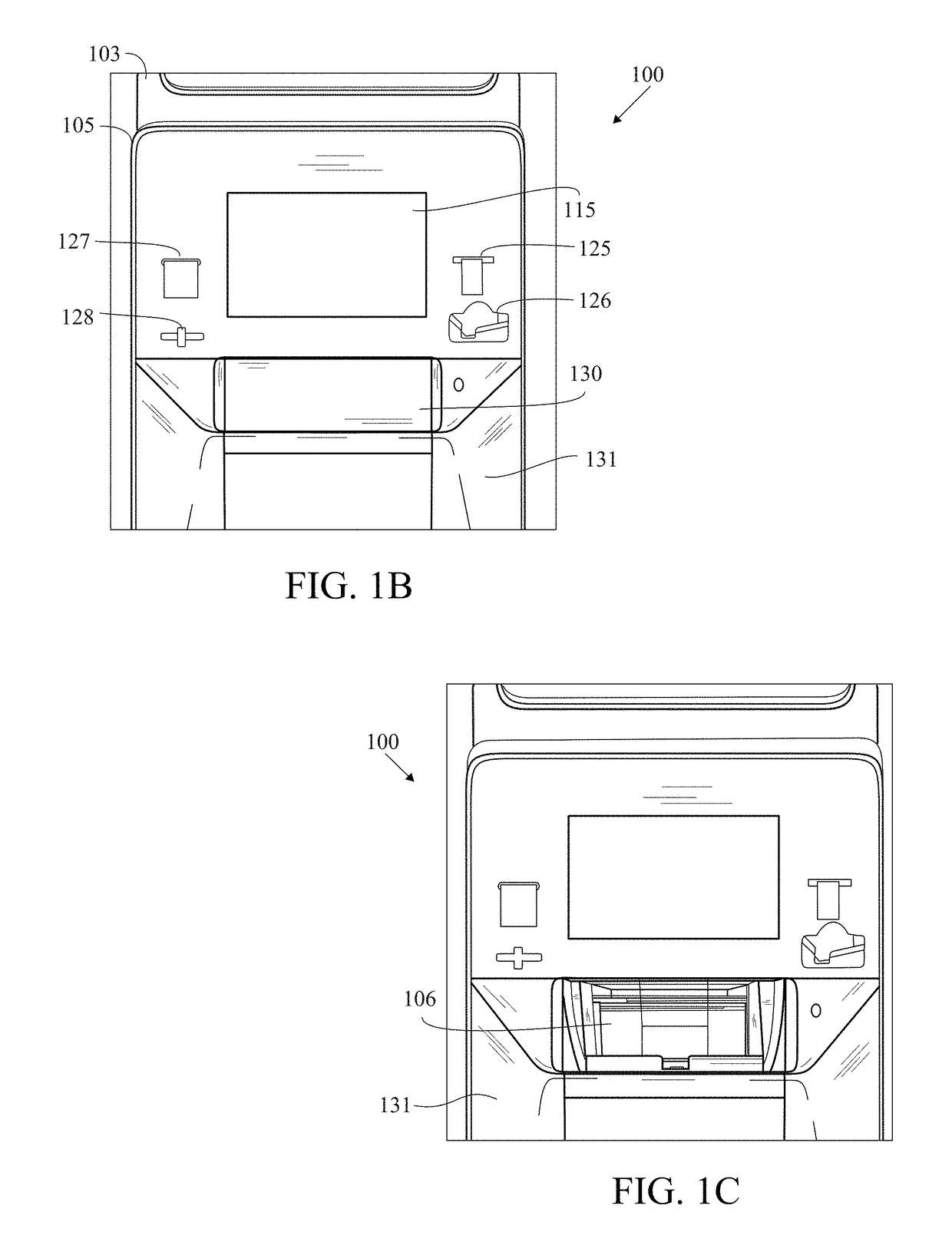

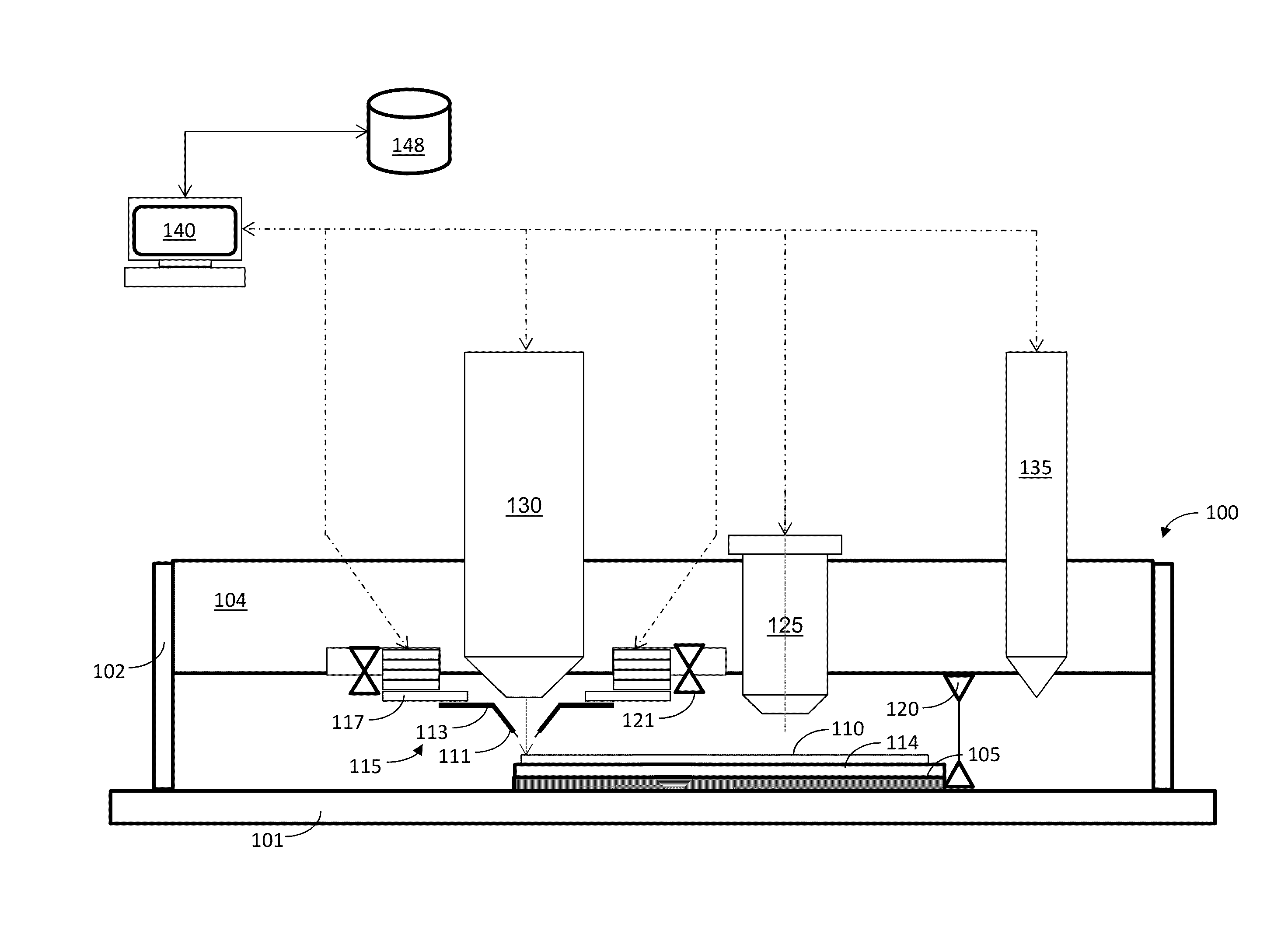

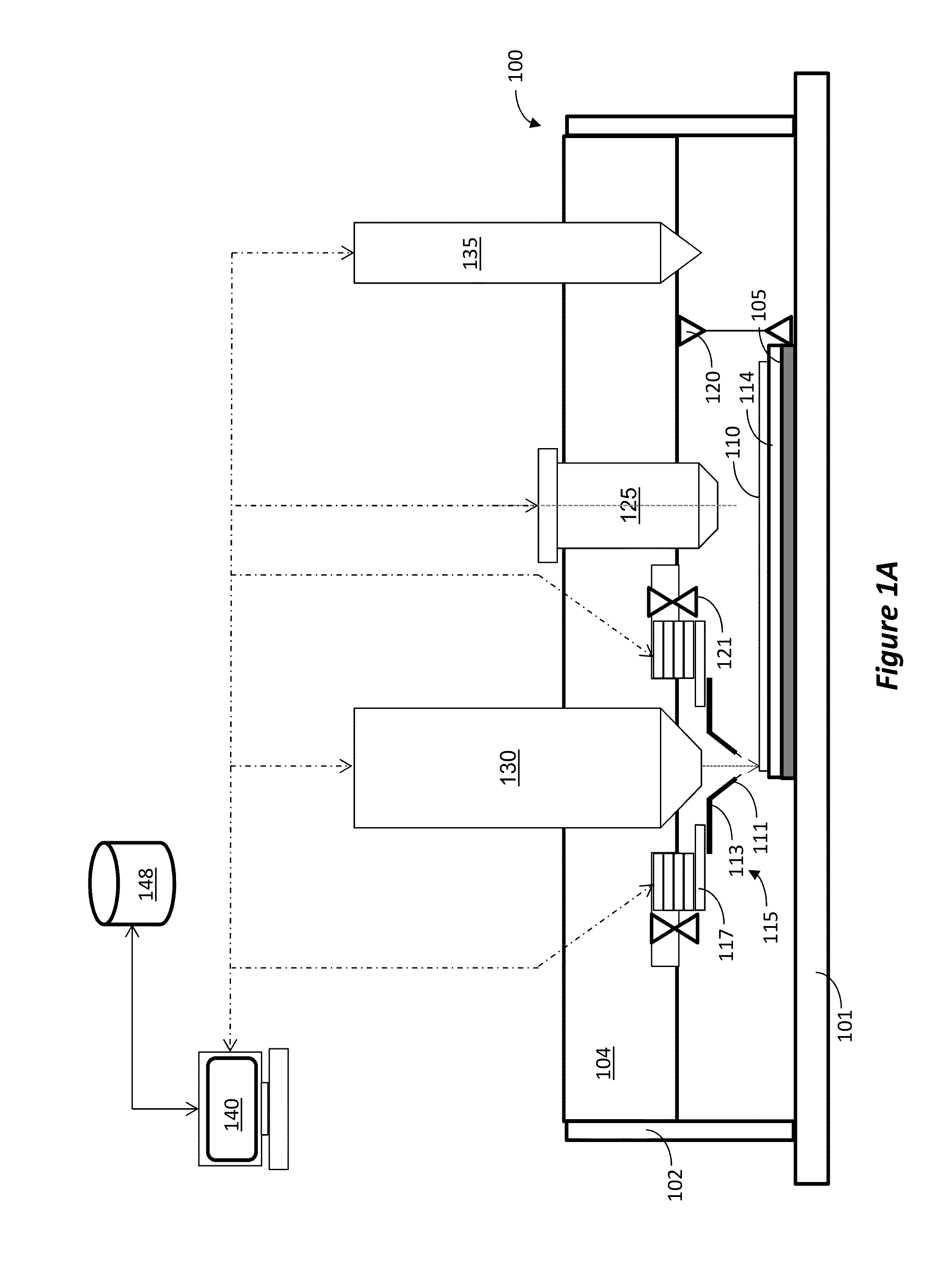

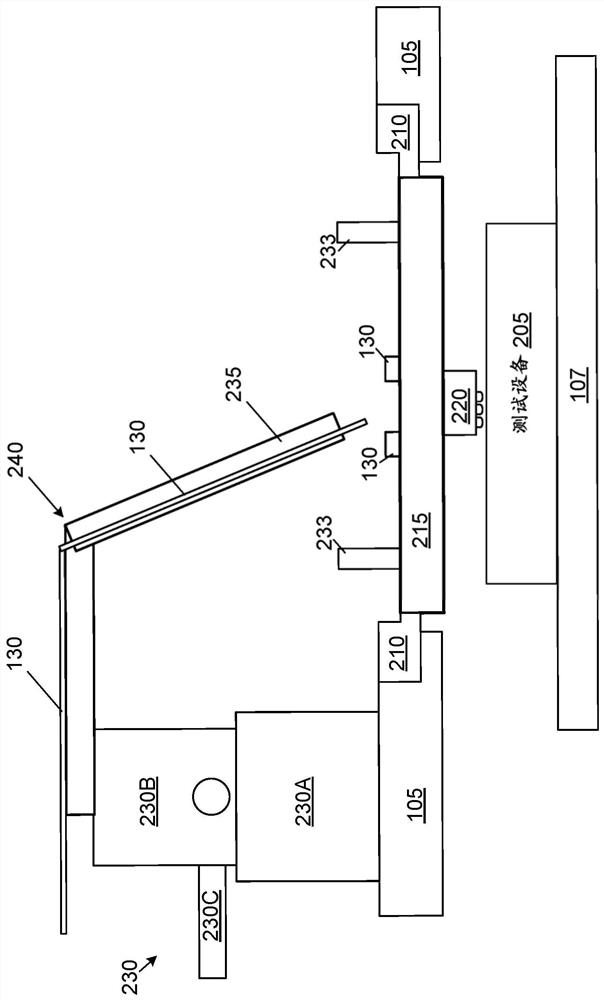

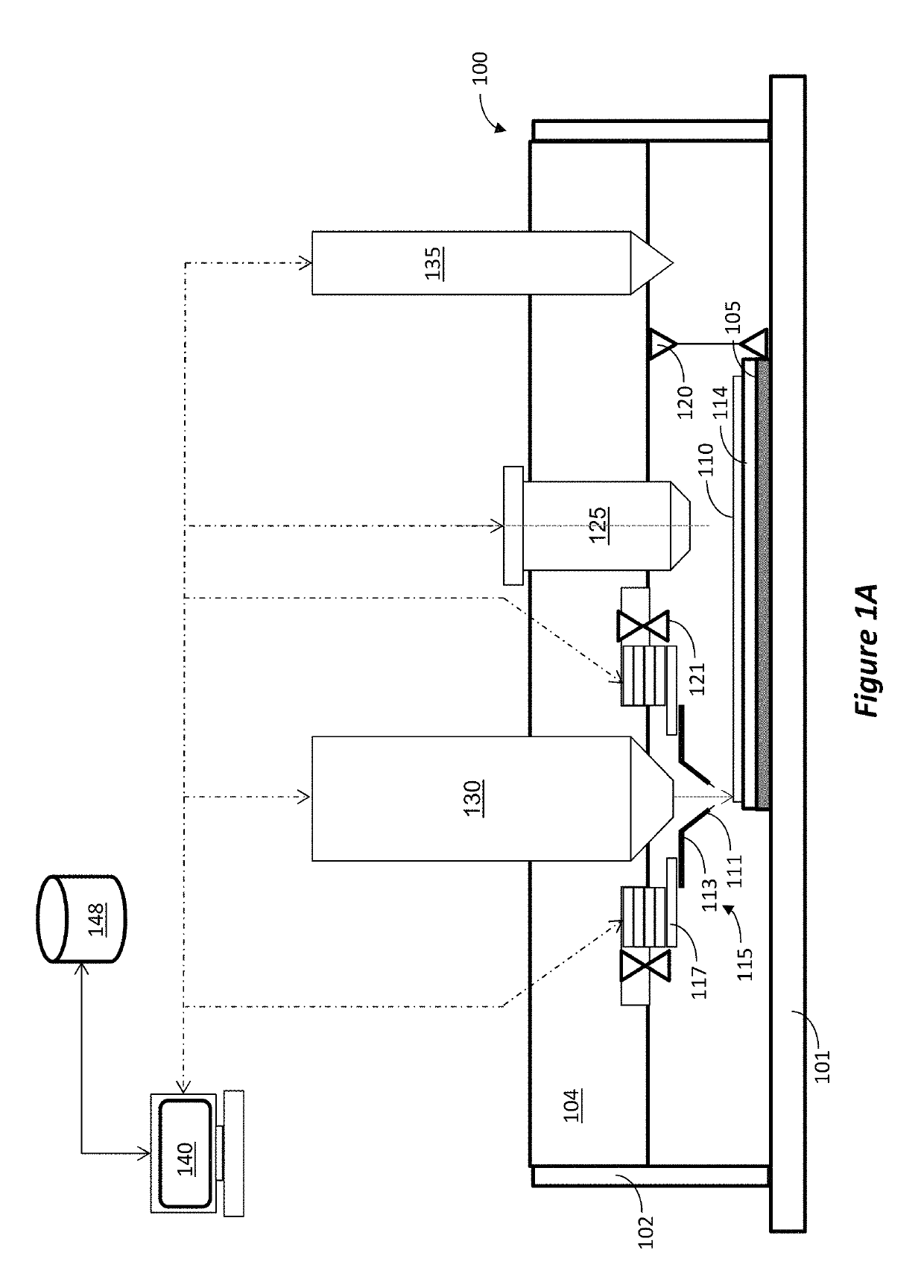

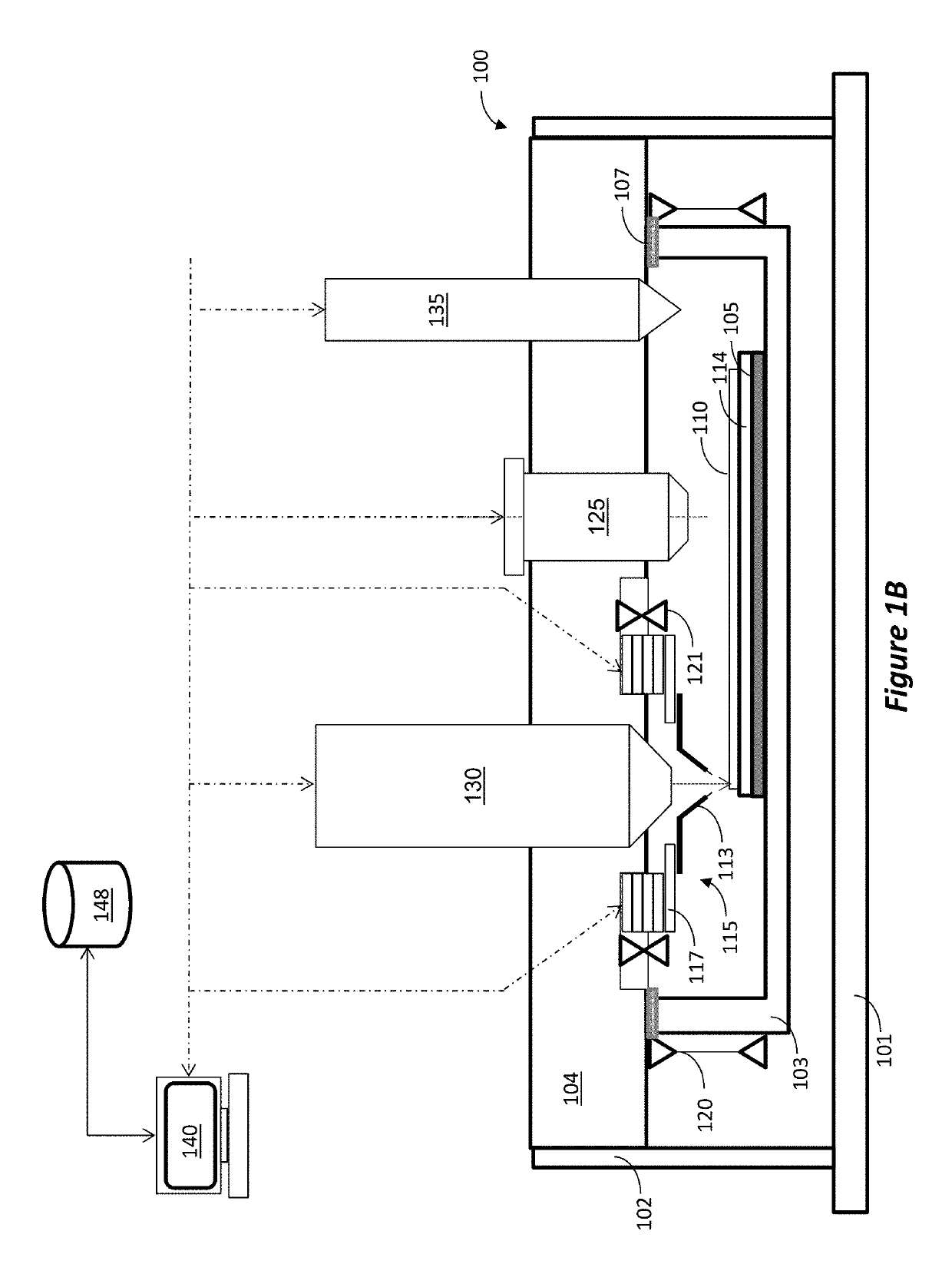

Kiosk For Recycling Electronic Devices

A recycling kiosk for recycling and financial remuneration for submission of an electronic device such as a mobile phone is disclosed herein. The recycling kiosk includes electrical connectors and an inspection area with an upper chamber, a lower chamber, a transparent plate and at least one camera in order to perform a visual analysis and an electrical analysis of the electronic device for determination of a value of the electronic device. The recycling kiosk also includes a processor and a display for user interaction.

Owner:ECOATM LLC

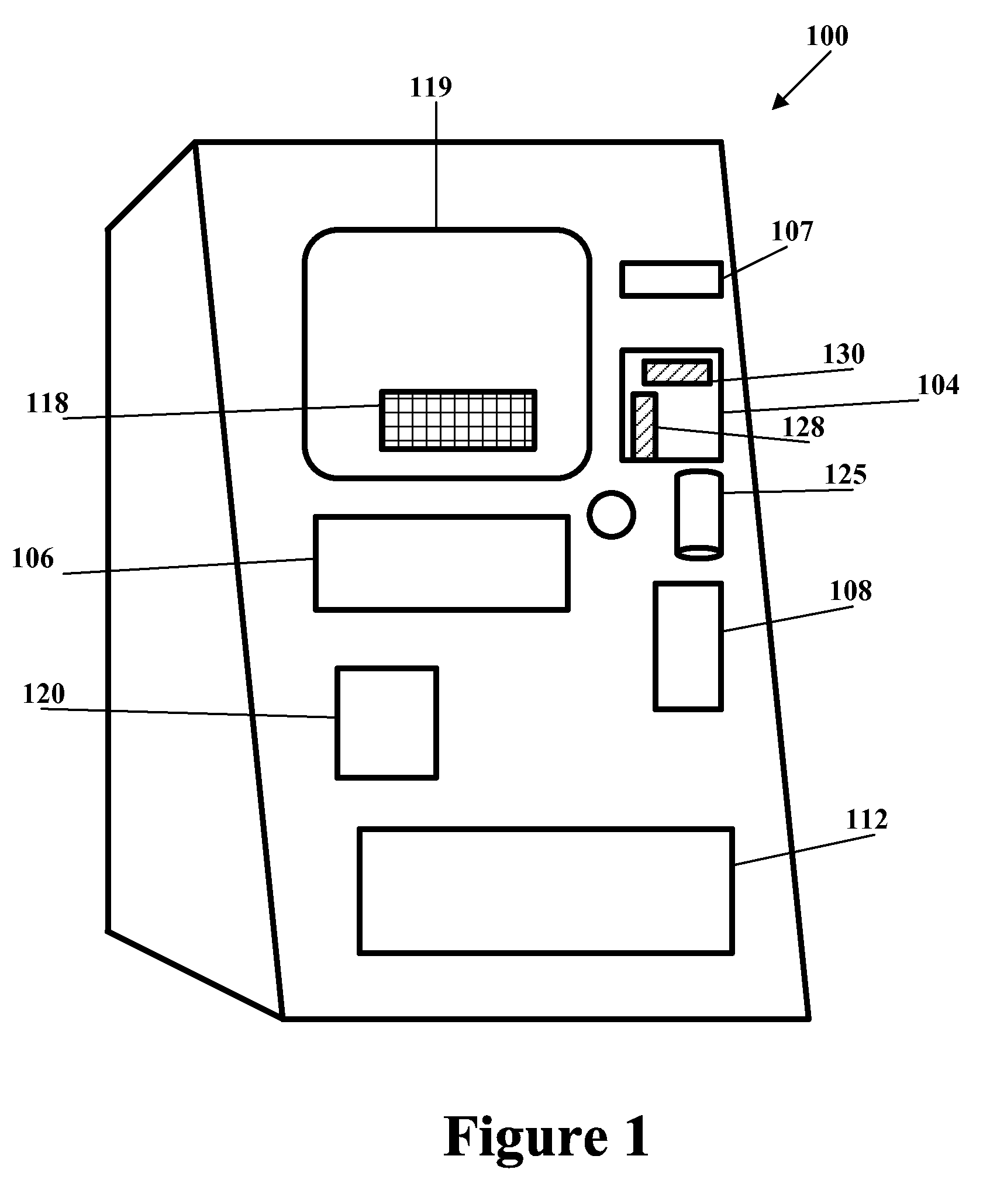

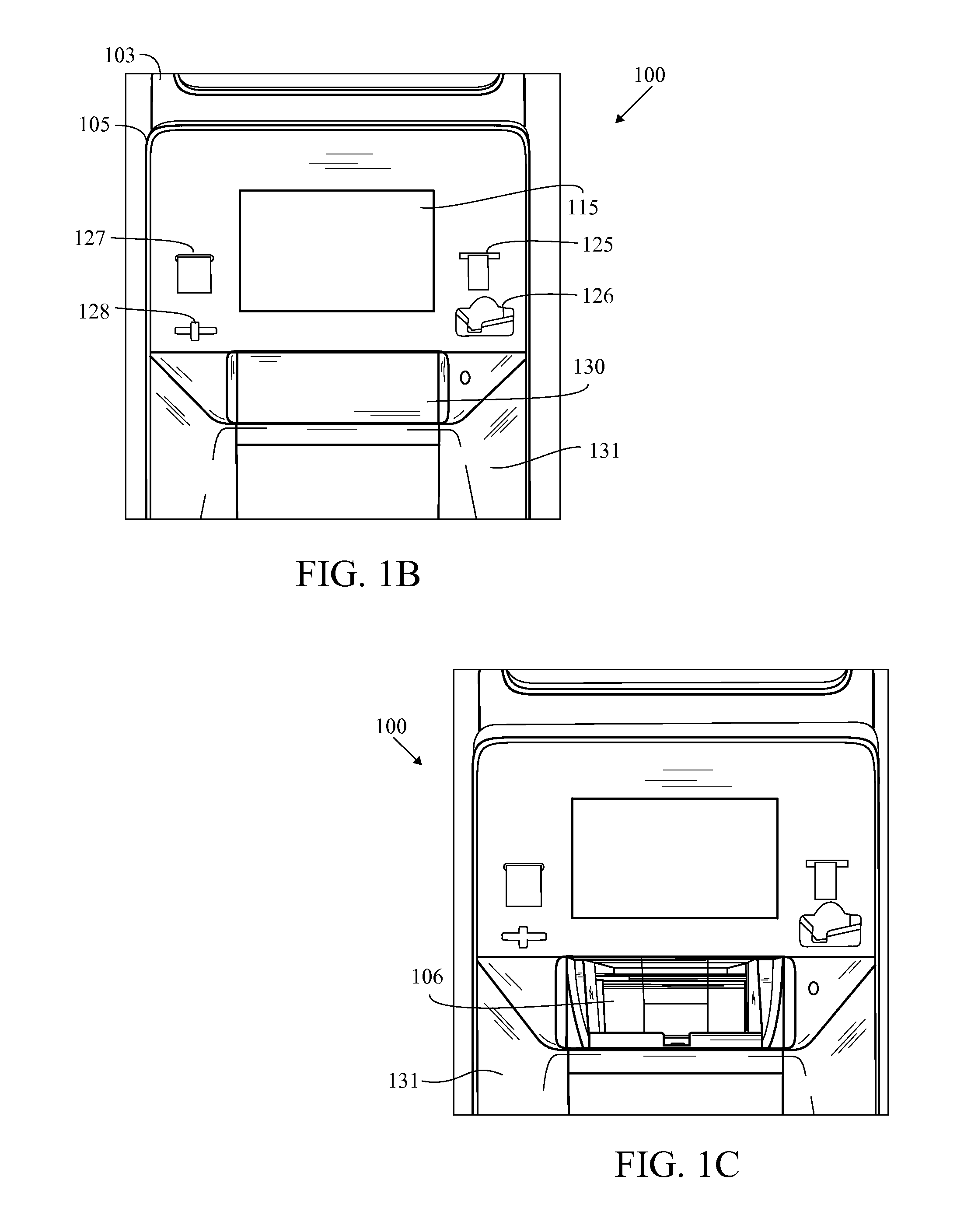

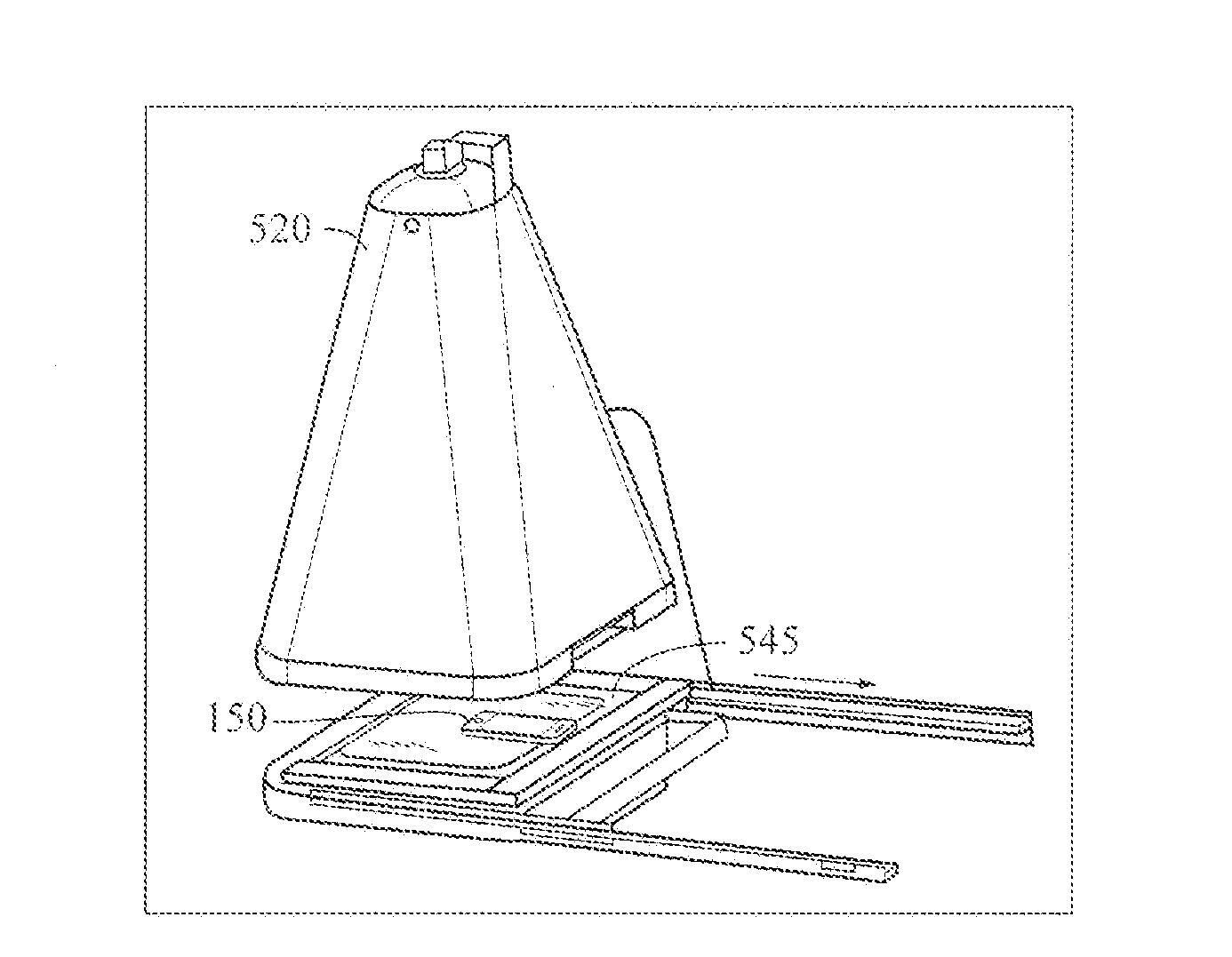

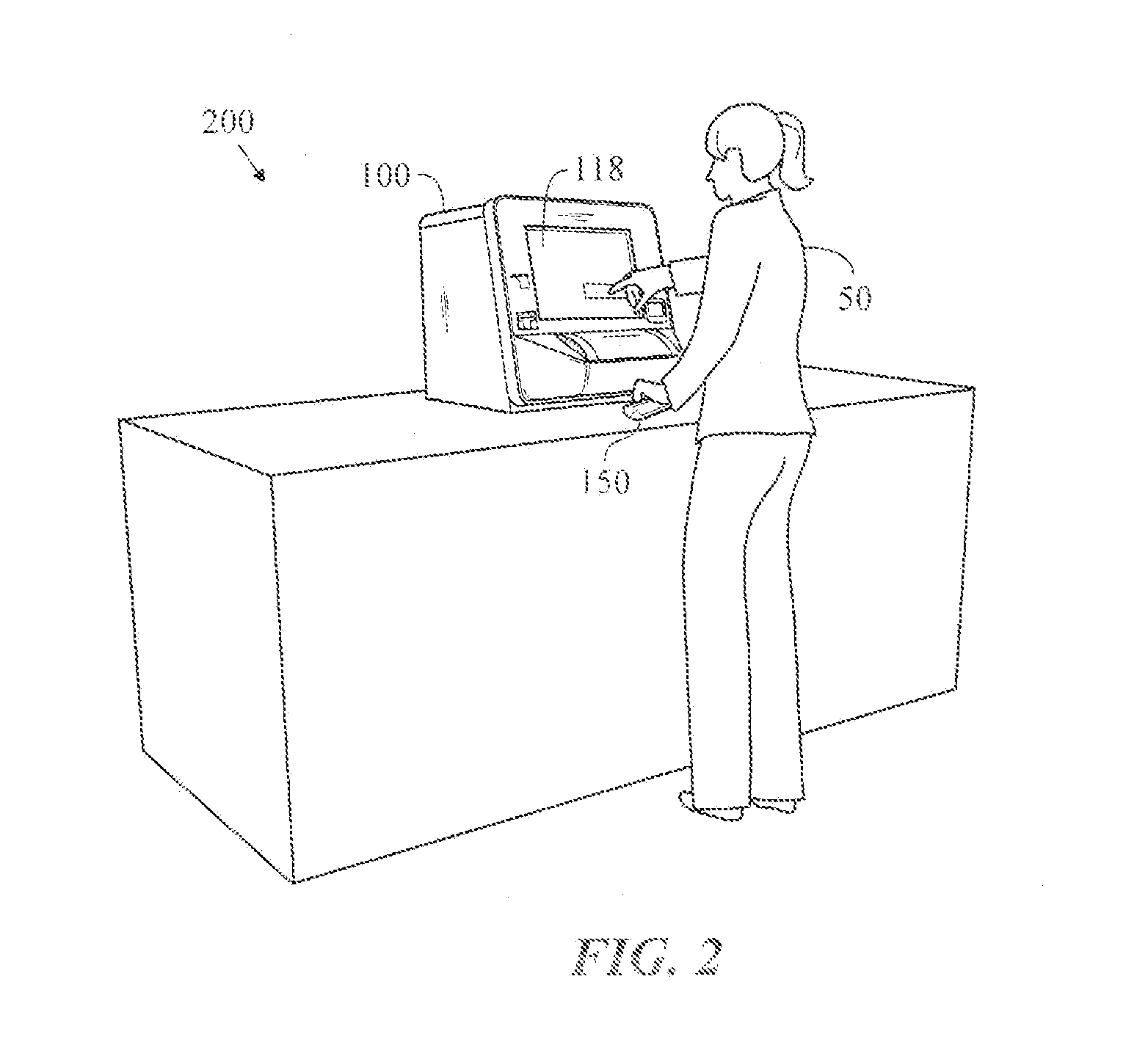

Mini-Kiosk For Recycling Electronic Devices

A mini-kiosk for recycling and financial remuneration for submission of an electronic device such as a mobile phone is disclosed herein. The mini-kiosk is designed to be placed on a counter-top. The mini-kiosk includes electrical connectors and an inspection area with at least one camera in order to perform a visual analysis and an electrical analysis of the electronic device for determination of a value of the electronic device. The mini-kiosk also includes a processor and a display for user interaction.

Owner:ECOATM LLC

Kiosk for recycling electronic devices

A recycling kiosk for recycling and financial remuneration for submission of an electronic device such as a mobile phone is disclosed herein. The recycling kiosk includes electrical connectors and an inspection area with an upper chamber, a lower chamber, a transparent plate and at least one camera in order to perform a visual analysis and an electrical analysis of the electronic device for determination of a value of the electronic device. The recycling kiosk also includes a processor and a display for user interaction.

Owner:ECOATM LLC

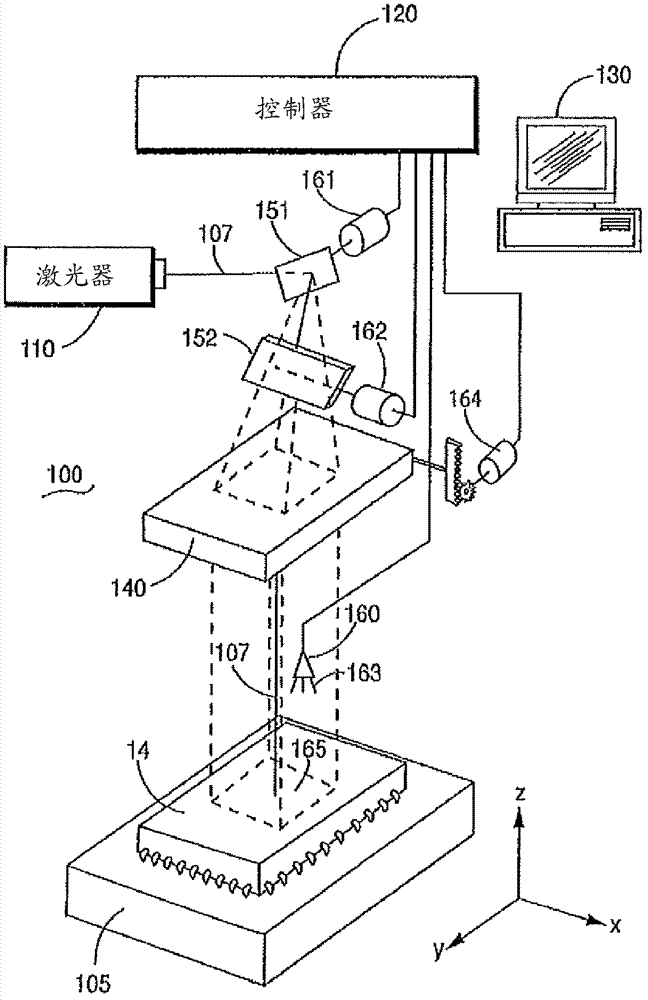

Through process flow intra-chip and inter-chip electrical analysis and process control using in-line nanoprobing

ActiveUS20150377921A1Quality improvementReduce riskSemiconductor/solid-state device testing/measurementElectronic circuit testingContact forceEngineering

System for performing in-line nanoprobing on semiconductor wafer. A wafer support or vertical wafer positioner is attached to a wafer stage. An SEM column, an optical microscope and a plurality of nanoprobe positioners are all attached to the ceiling. The nanoprobe positioners have one nanoprobe configured for physically contacting selected points on the wafer. A force (or touch) sensor measures contact force applied by the probe to the wafer (or the moment) when the probe physically contacts the wafer. A plurality of drift sensors are provided for calculating probe vs. wafer alignment drift in real-time during measurements.

Owner:DCG SYST

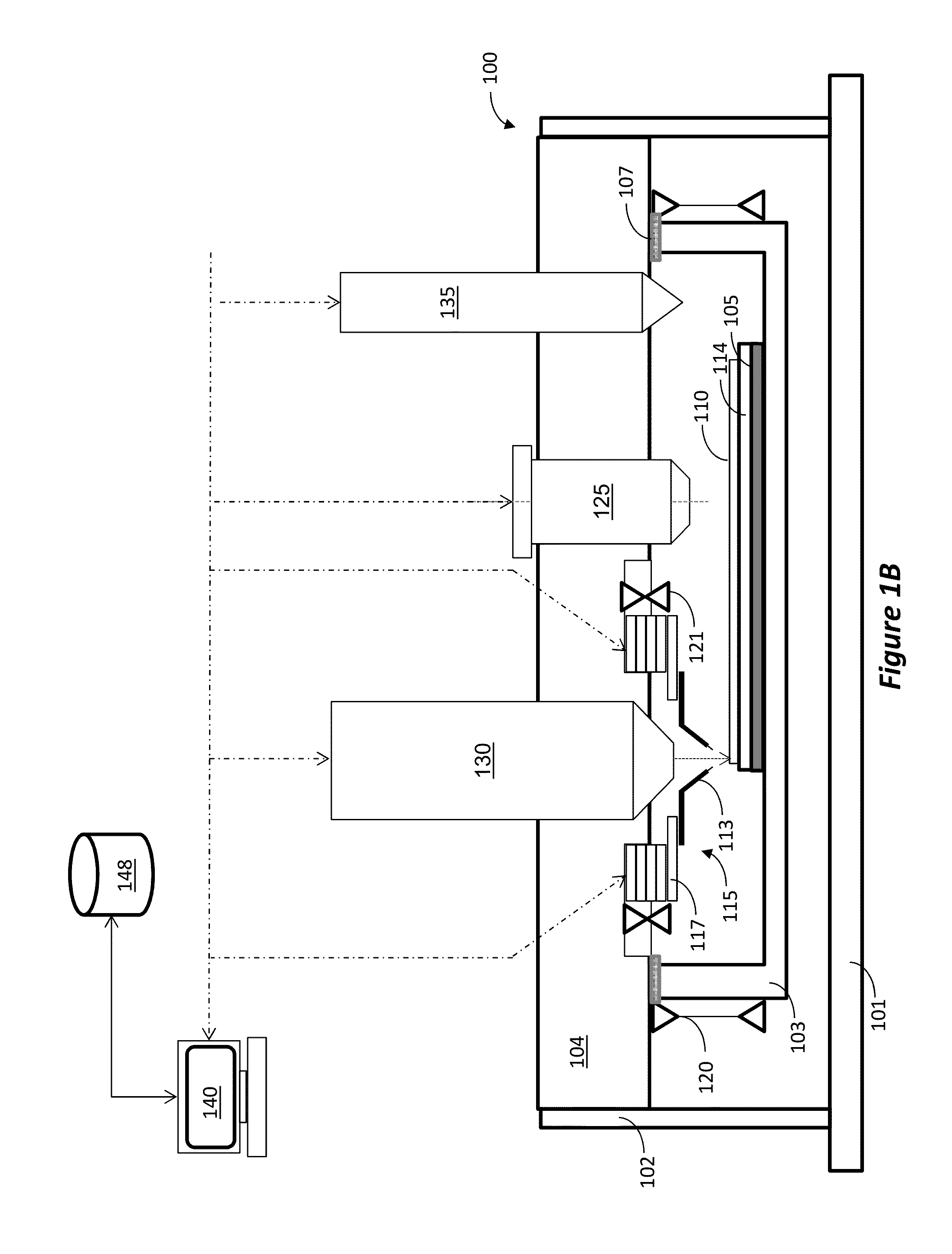

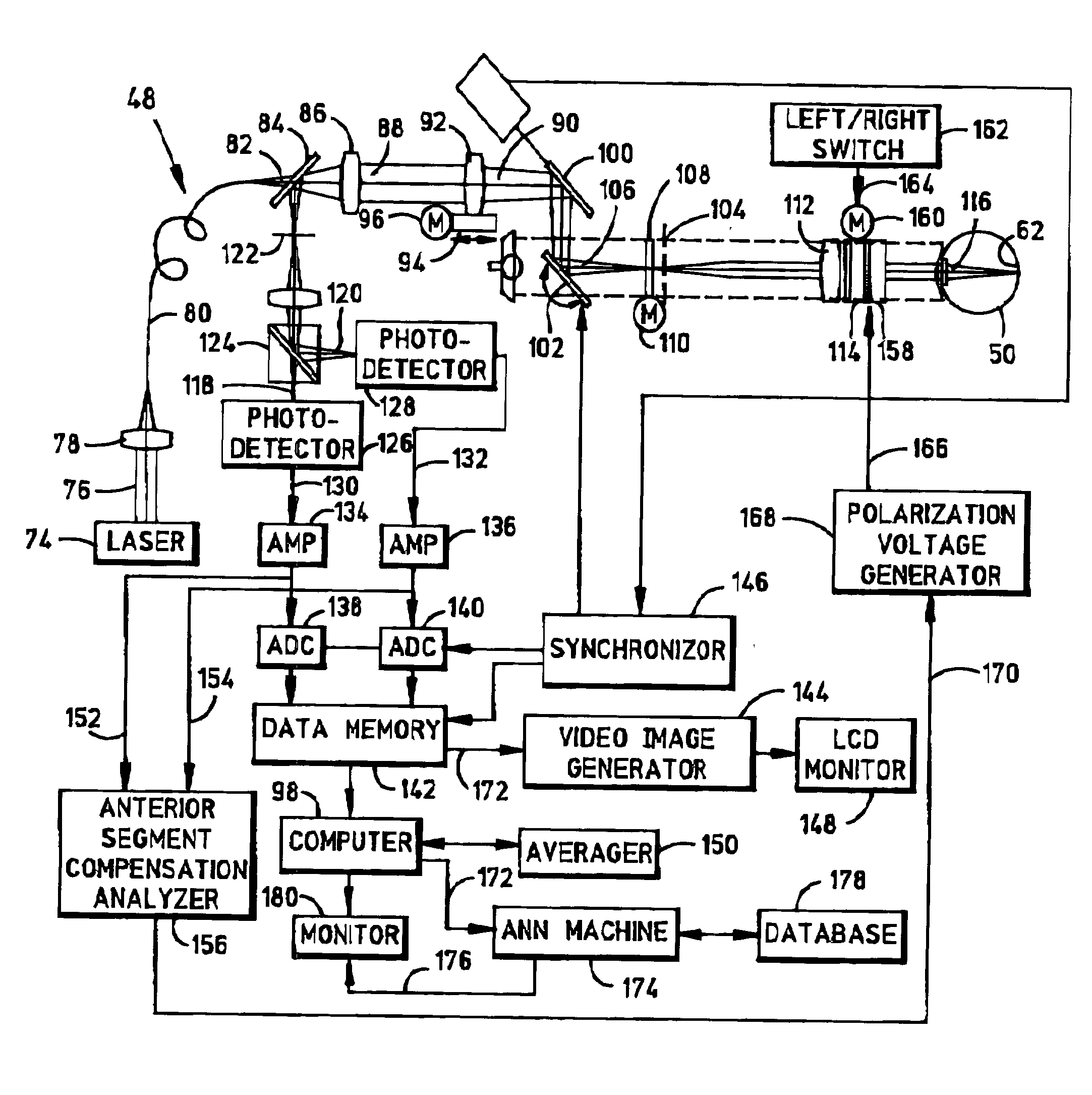

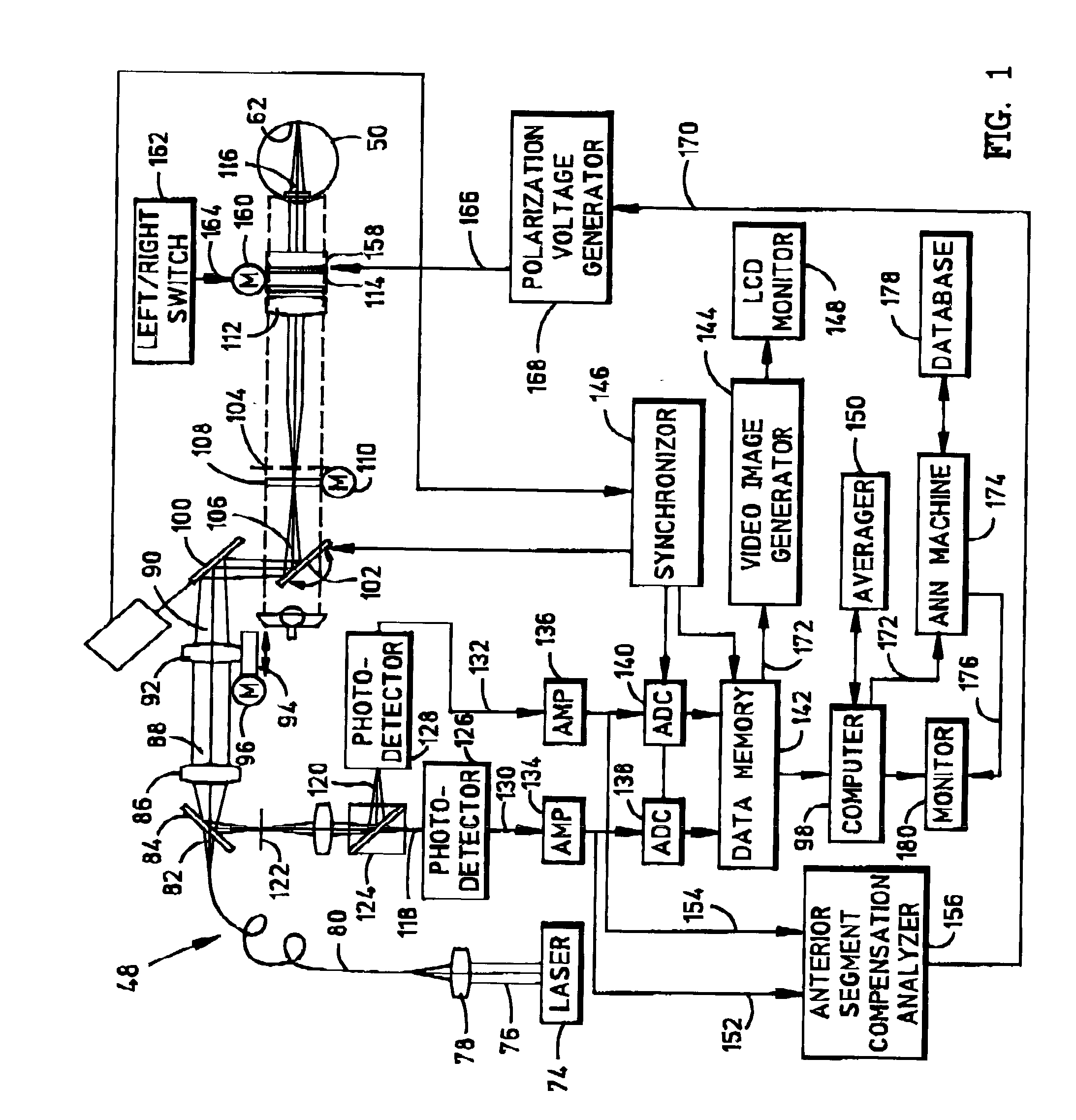

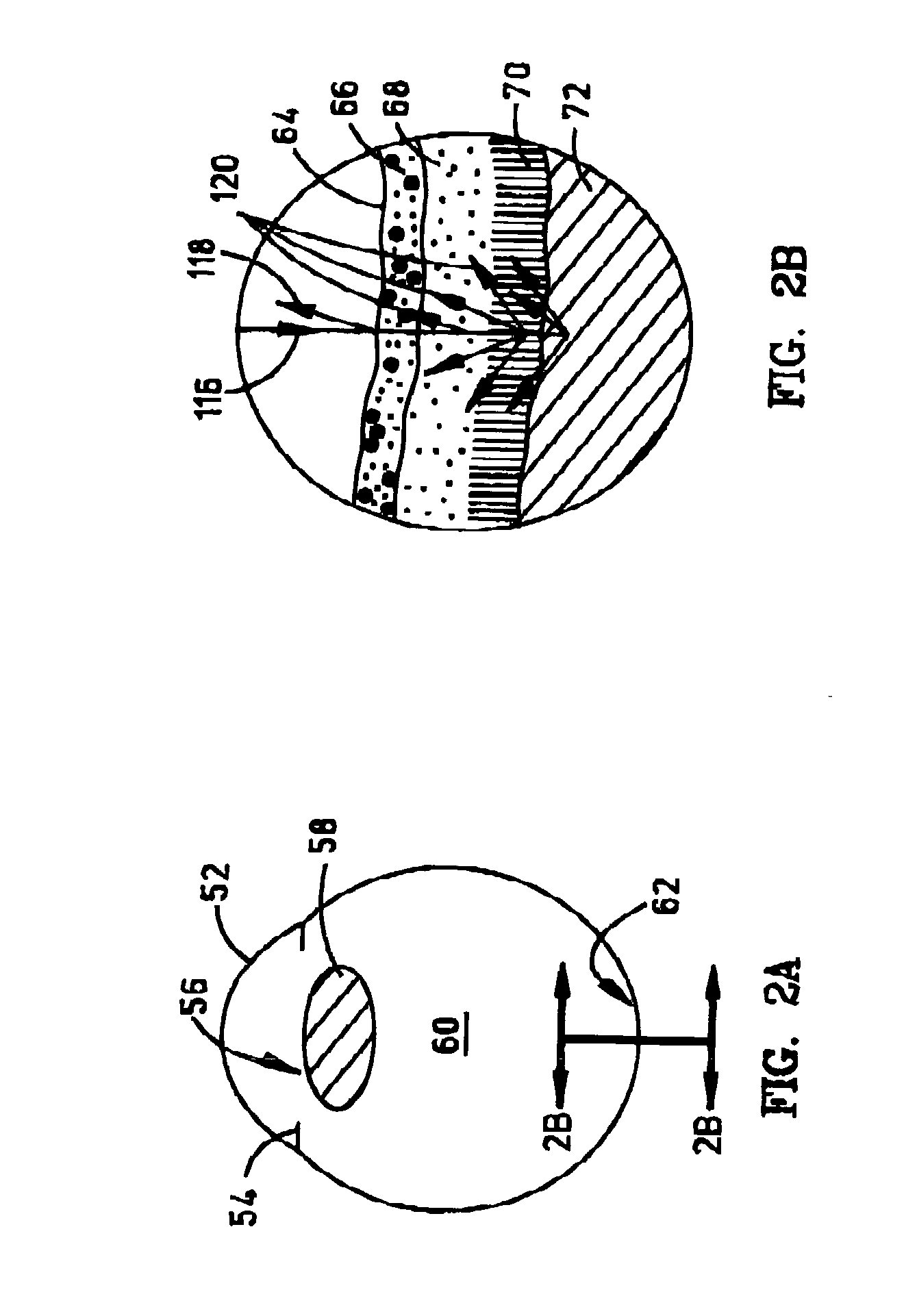

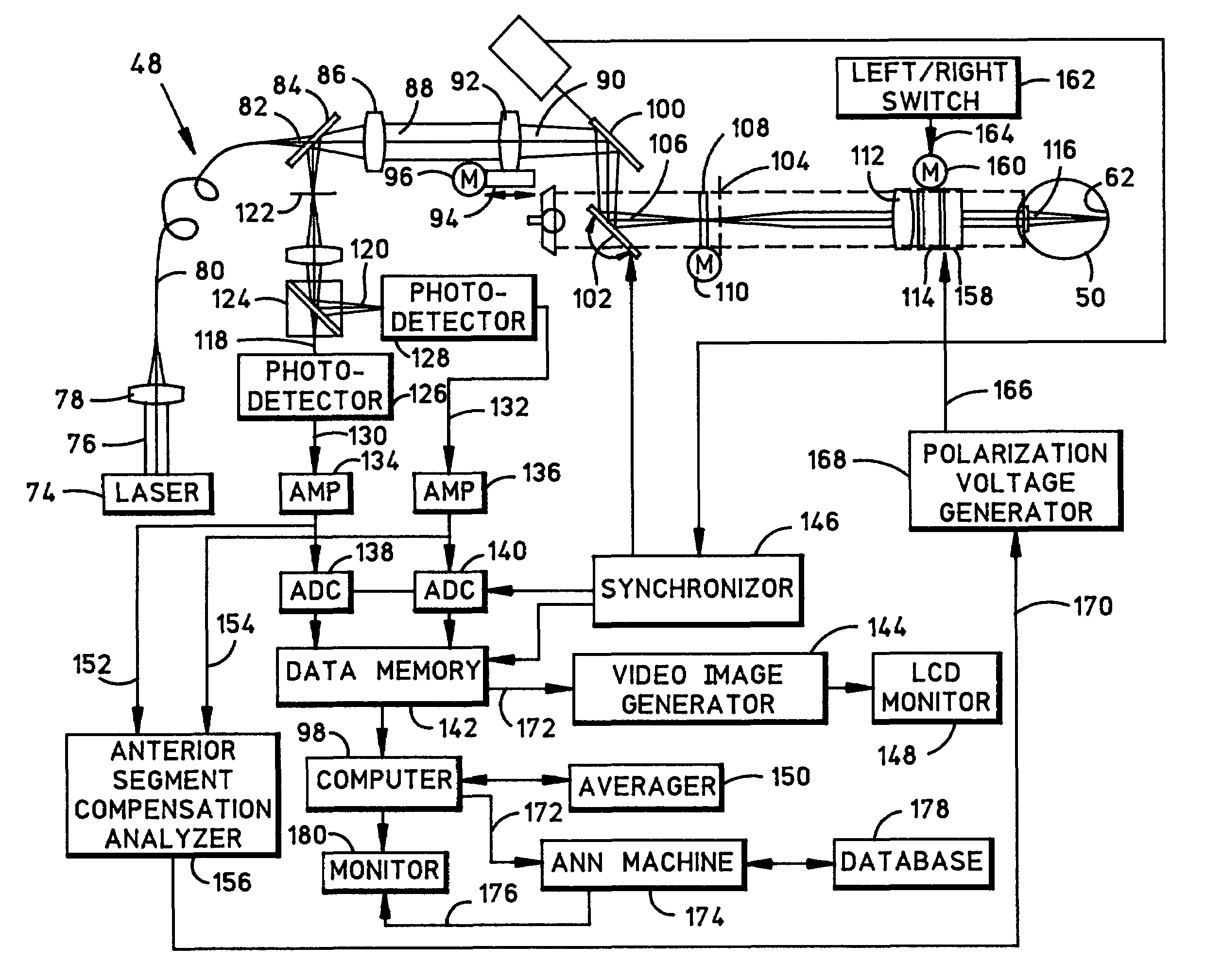

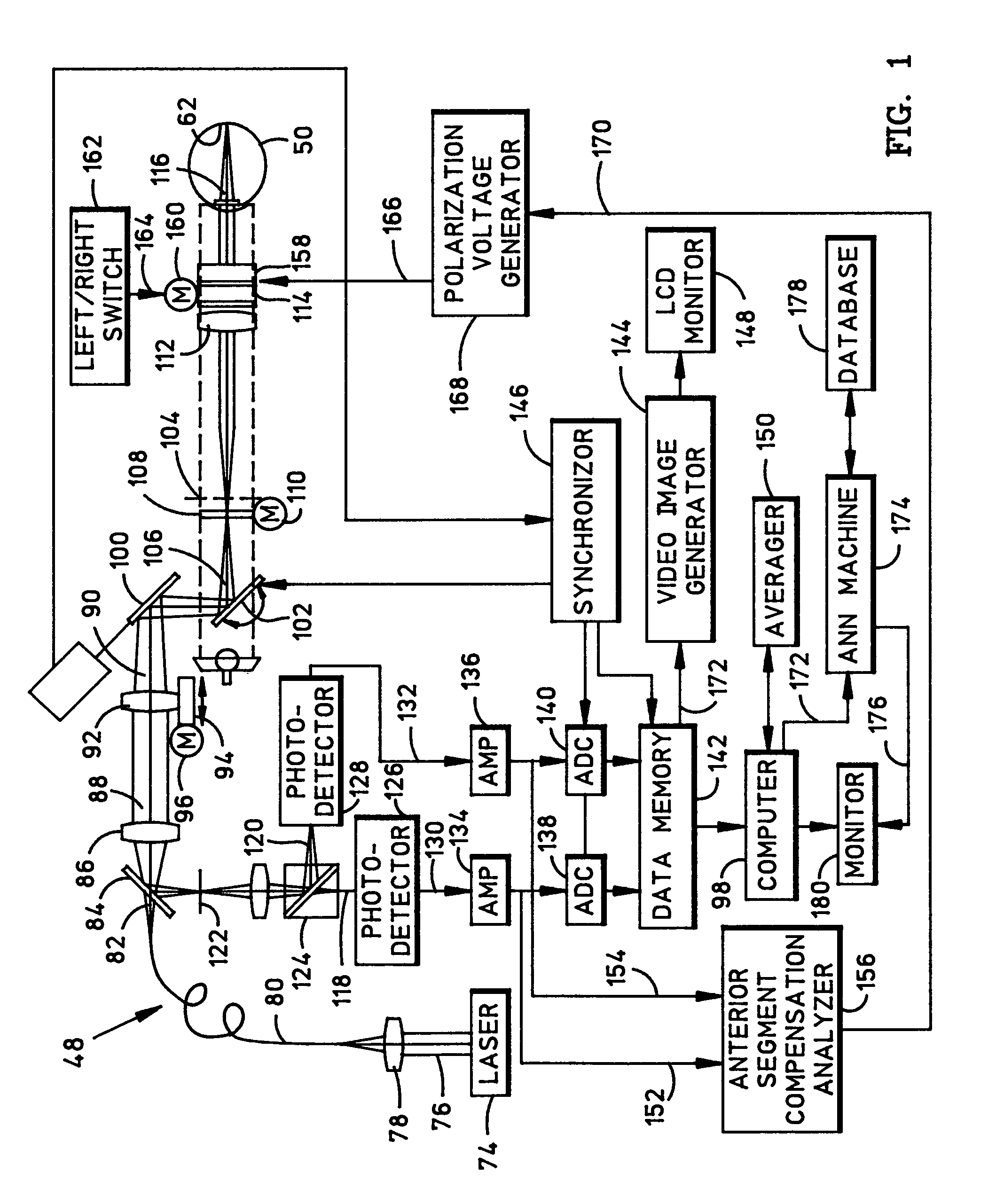

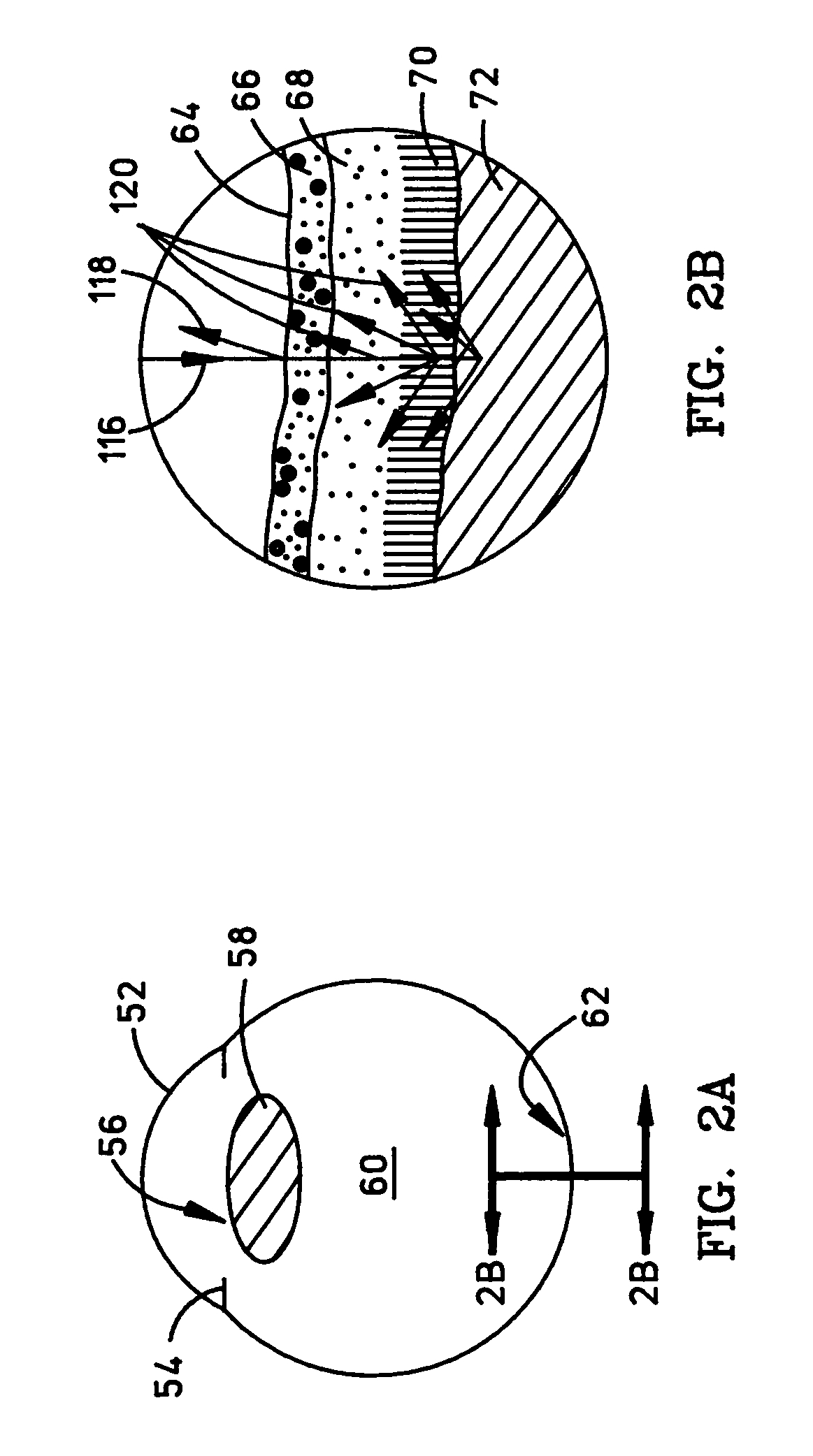

Method and system for detecting the effects of alzheimer's disease in the human retina

InactiveUS20040064064A1Avoid excessive errorLarge featureUsing optical meansOthalmoscopesElectricityBeam splitter

A system for the in vivo detection of the effects of AD in the interior of an eye. A scanning polarimeter, including a residual retardance canceling system and an improved anterior segment retardance compensator, produces an optical analysis signal representing the birefringence of the retinal nerve fiber layer (RNFL) structures of the eye. The birefringence data is more accurate because of compensation for anterior segment birefringence and residual birefringence of optical components, such as, for example, the beam splitters, lenses, scanners and retarders. An electrical analysis signal representing a large (20 by 40 degrees) retardance map is produced and evaluated by an artificial neural network to produce an analysis classification signal representing the contribution of Alzheimer's disease to the birefringence of the retinal layer corresponding to the relationship of the electrical analysis signal to an analysis signal database.

Owner:CARL ZEISS MEDITEC INC

Kiosk For Recycling Electronic Devices

A recycling kiosk for recycling and financial remuneration for submission of an electronic device such as a mobile phone is disclosed herein. The recycling kiosk includes electrical connectors and an inspection area with an upper chamber, a lower chamber, a transparent plate and at least one camera in order to perform a visual analysis and an electrical analysis of the electronic device for determination of a value of the electronic device. The recycling kiosk also includes a processor and a display for user interaction.

Owner:LIBRIZZI MICHAEL +6

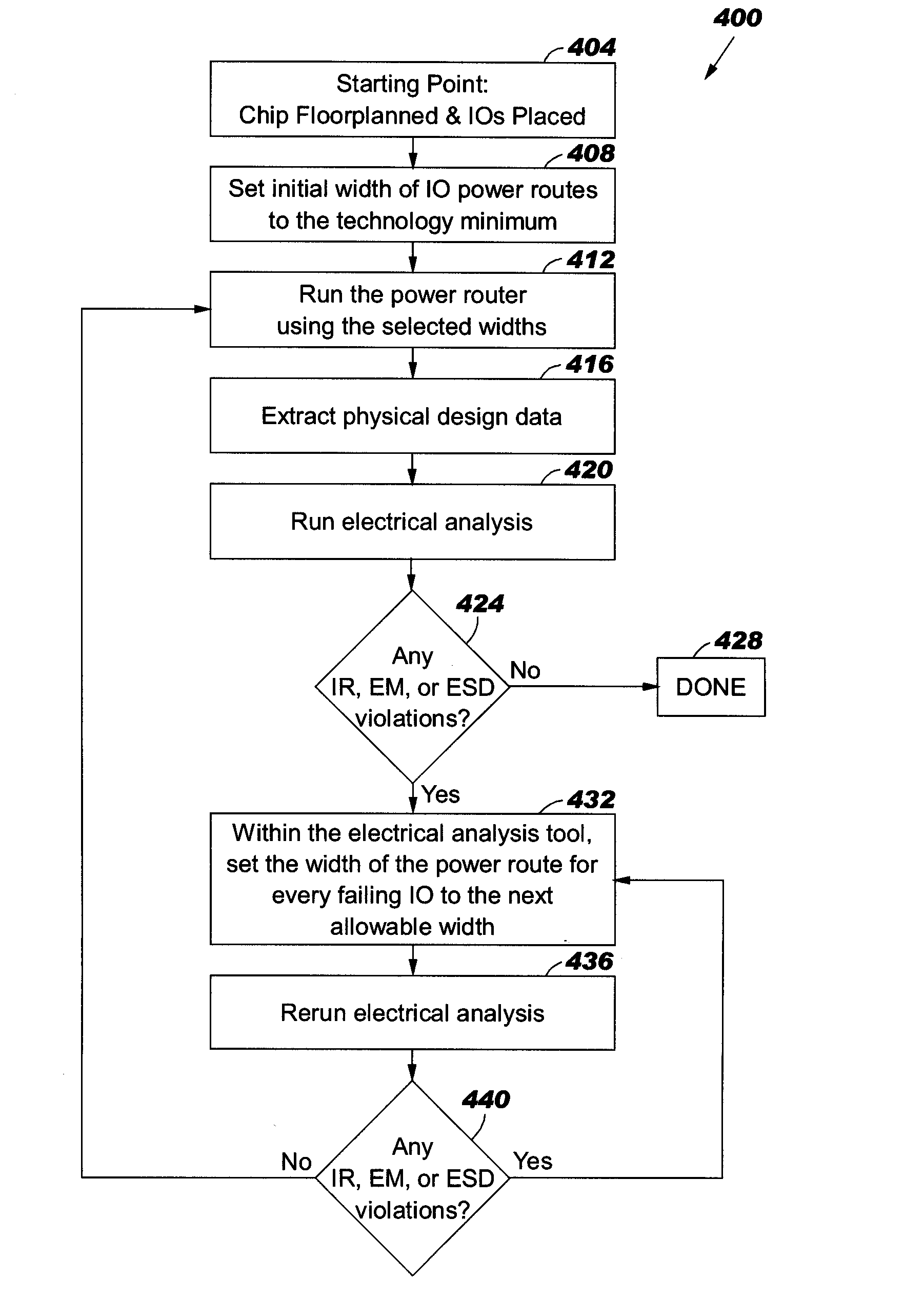

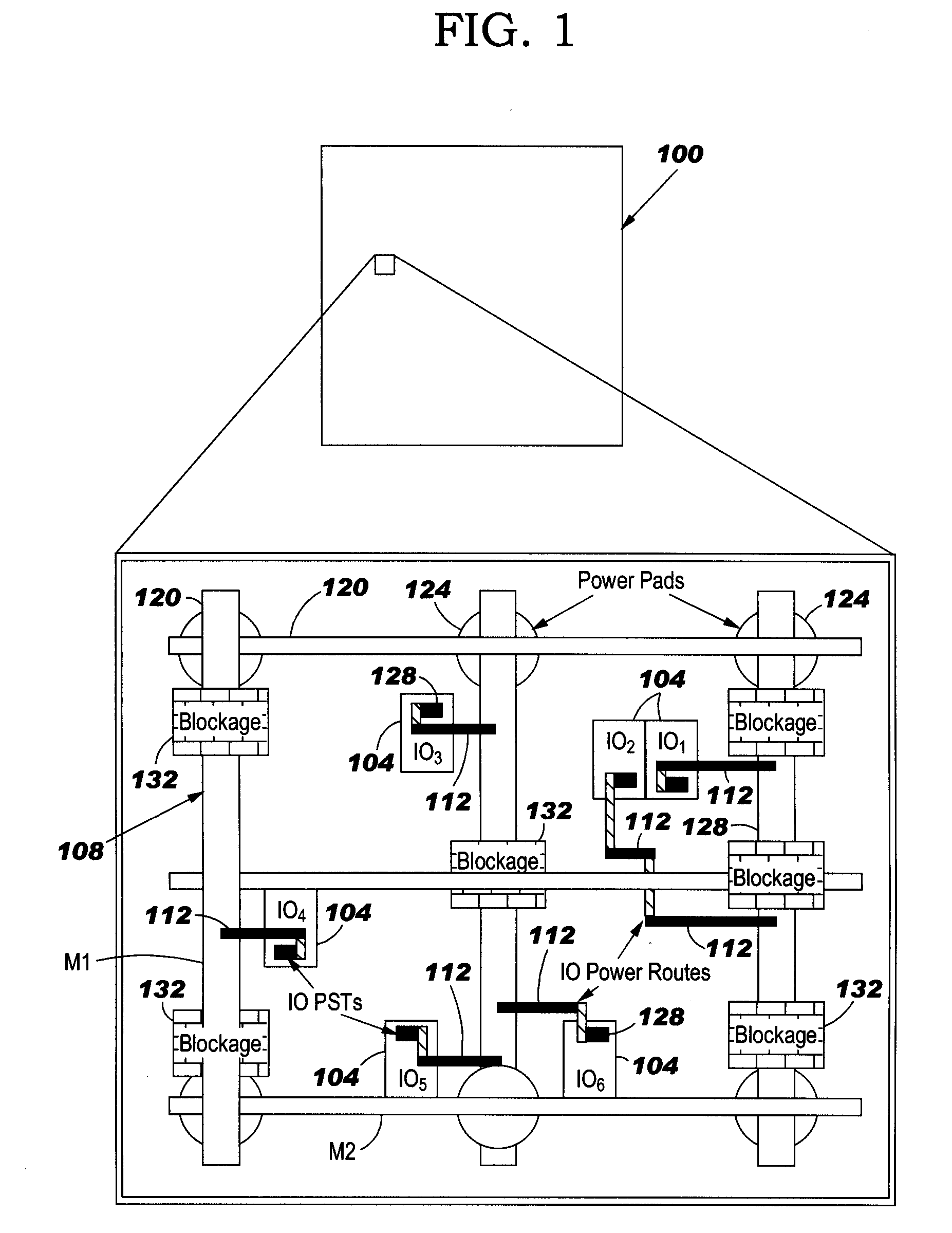

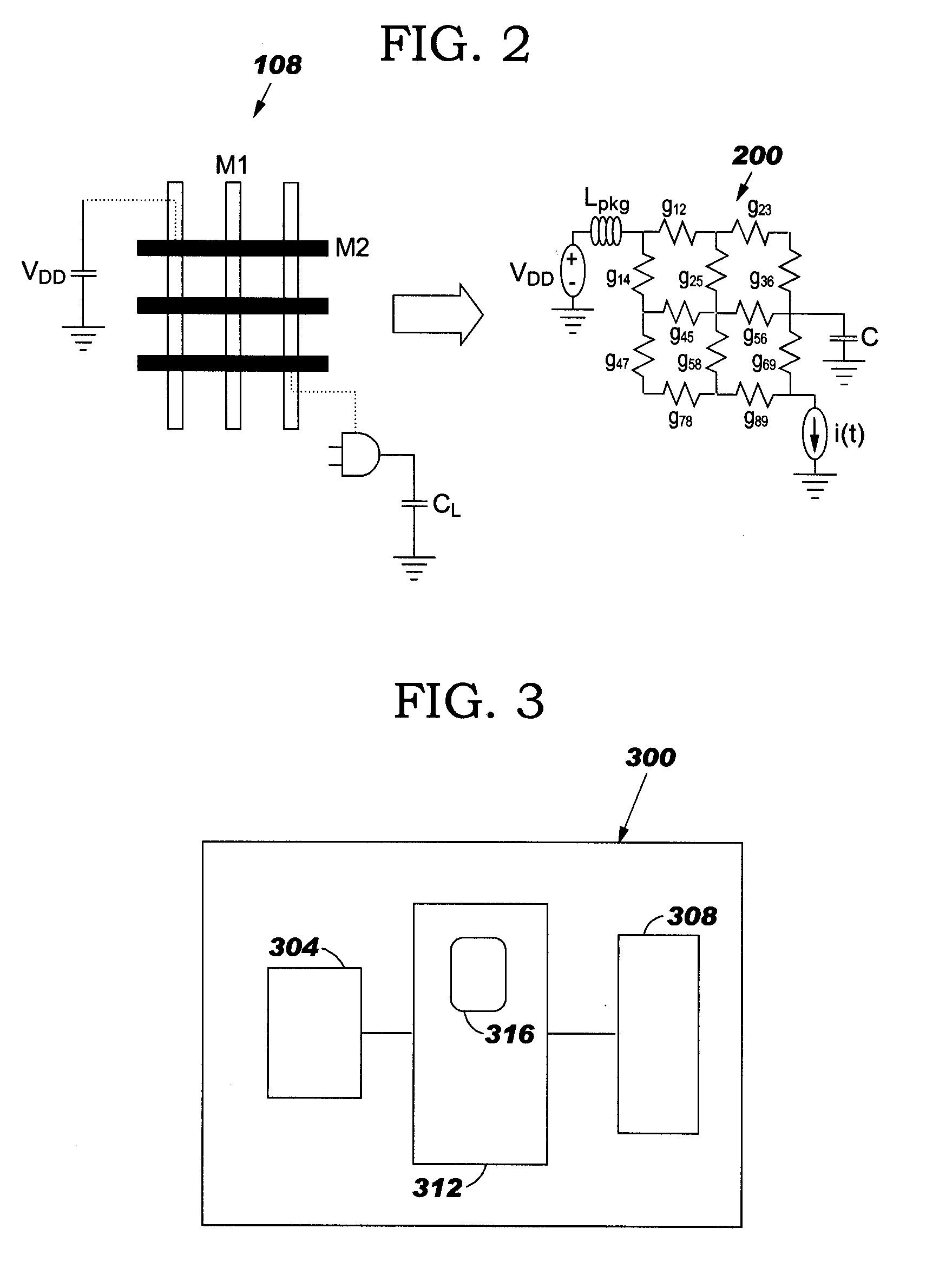

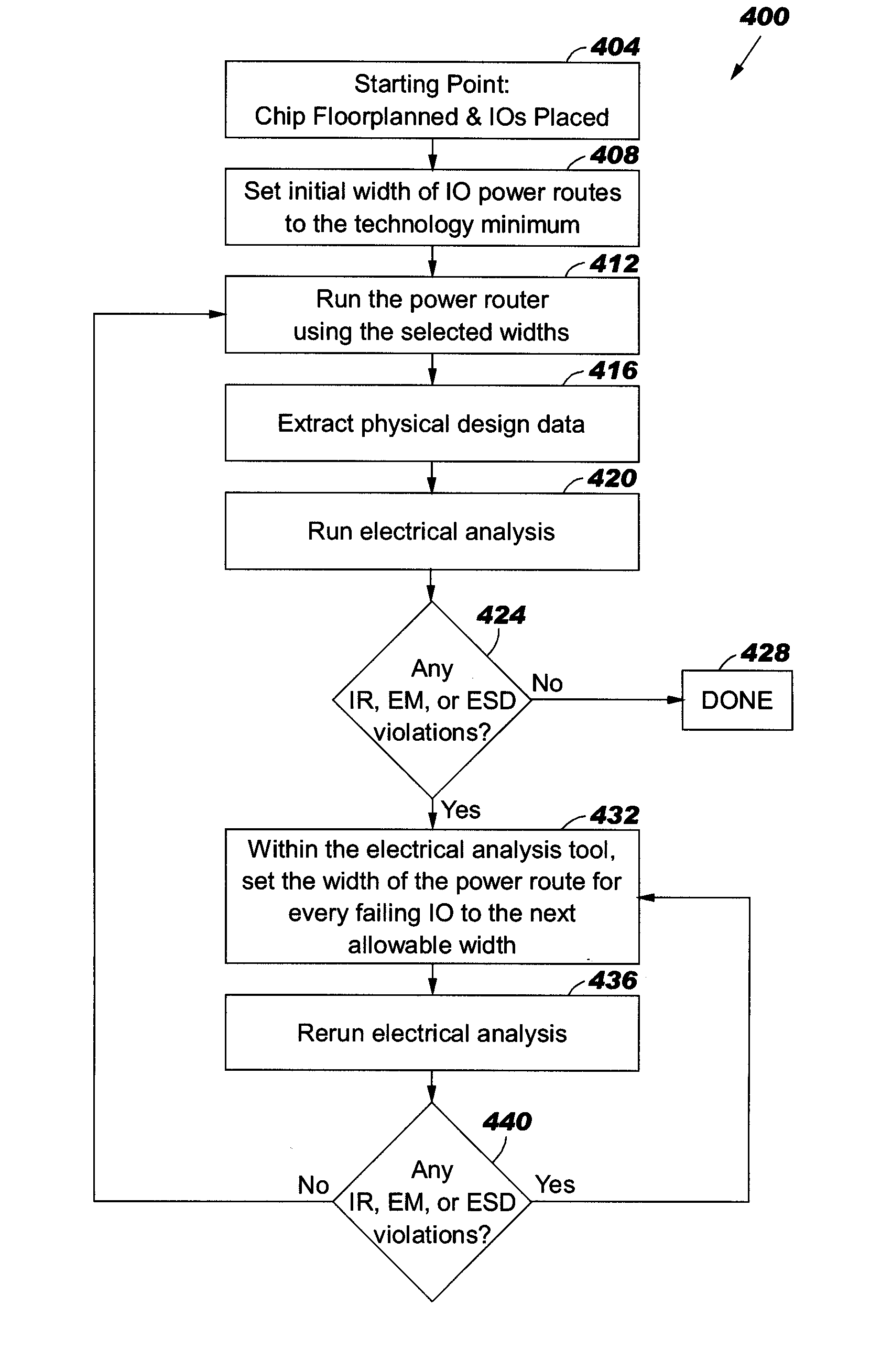

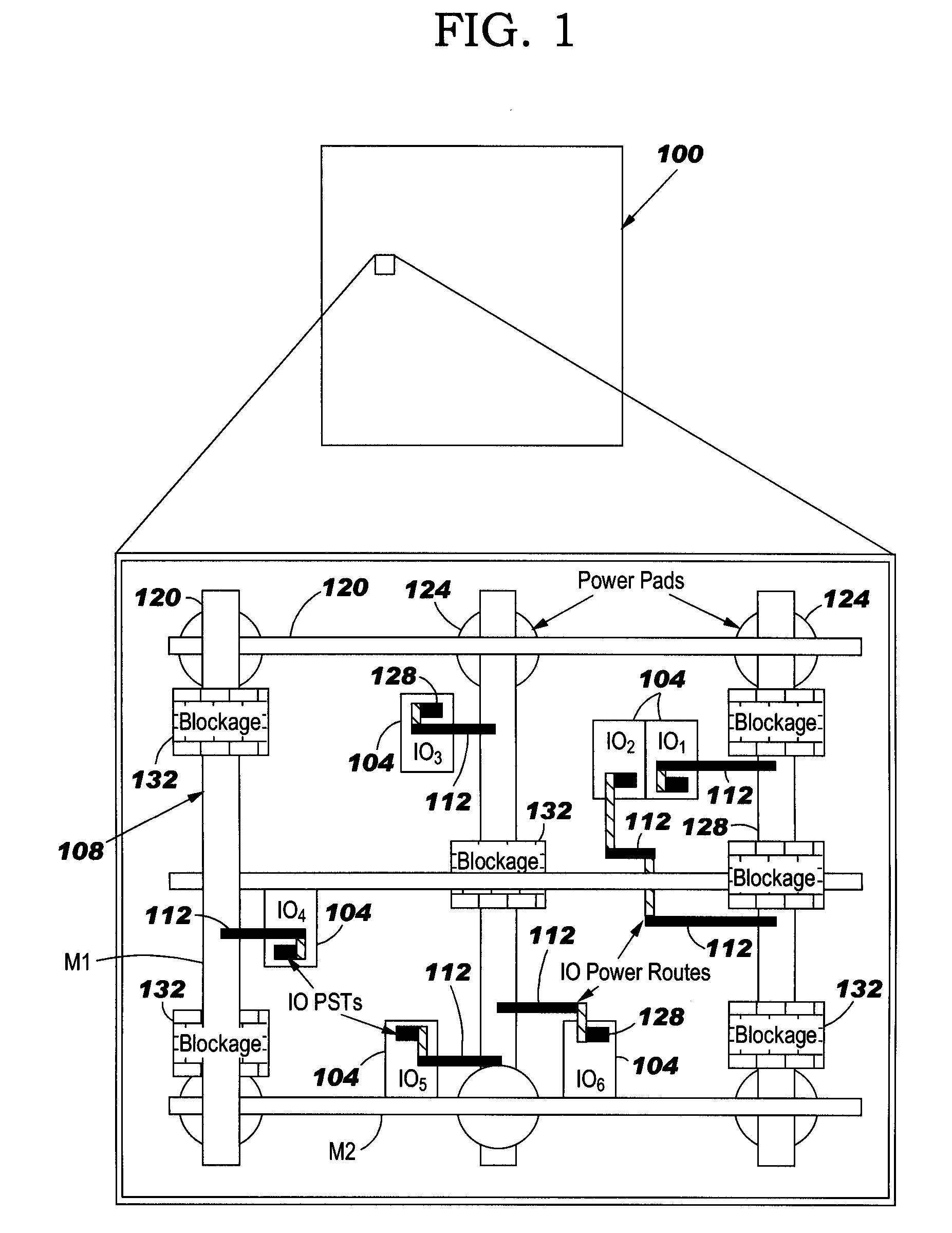

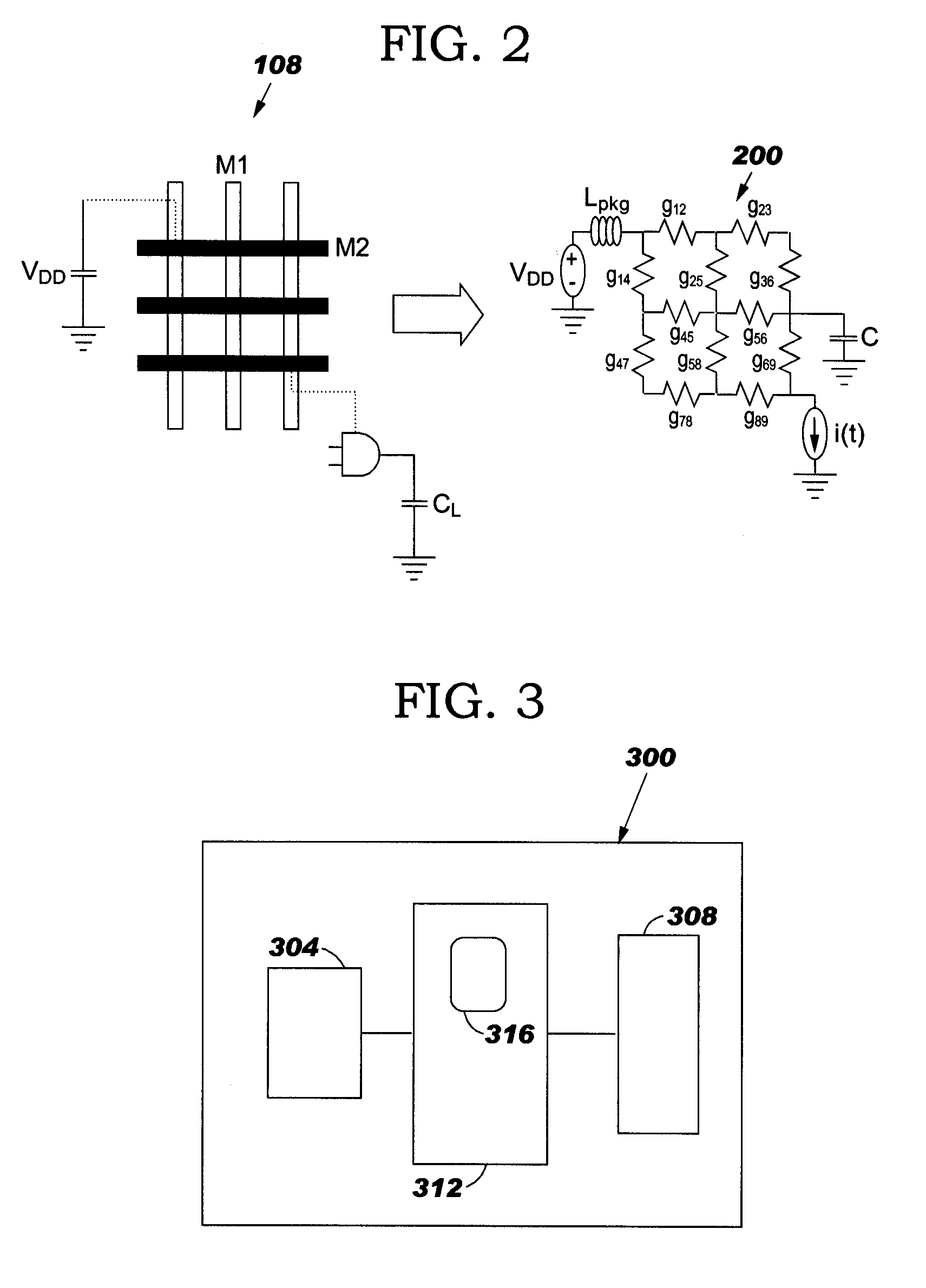

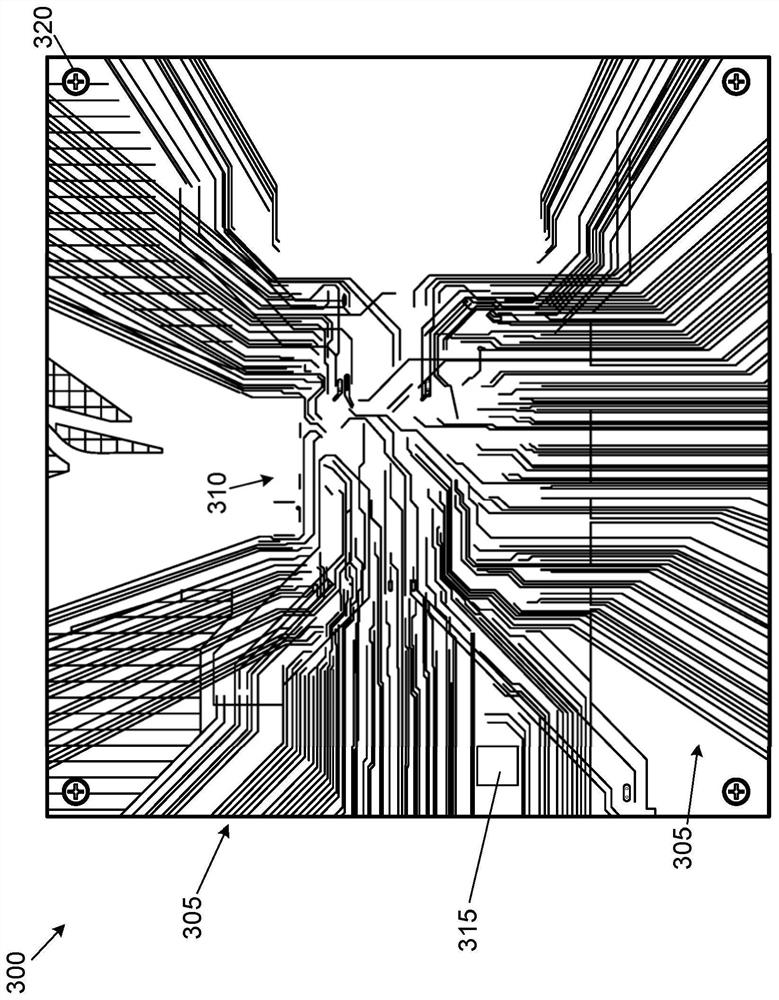

I/O circuit power routing system and method

InactiveUS20050289494A1Computer aided designSoftware simulation/interpretation/emulationIntegratorHemt circuits

A method (400) of determining widths (W) and / or routes of I / O power routes (112) between one or more power distribution networks (108) and a plurality of I / O circuits (104) based on IR drop, electromigration, and electrostatic discharge electrical requirements. The method includes initially routing the I / O power routes and then iteratively analyzing the I / O power routes and iteratively incrementing the width of each power route that fails one or more of the electrical requirements until all power routes meet all electrical requirements. Once all power routes meet the electrical requirements, power routing is performed again to re-route any power routes as necessary to accommodate their wider widths. The method may be implemented in system (300) that includes a power routing tool (304), an electrical analysis tool (308), and a tool integrator (312) that implements an integrated power routing algorithm (316).

Owner:IBM CORP

Method and system for detecting the effects of Alzheimer's disease in the human retina

InactiveUS6988995B2Avoid excessive errorLarge featureUsing optical meansOthalmoscopesElectricityBeam splitter

A system for the in vivo detection of the effects of AD in the interior of an eye. A scanning polarimeter, including a residual retardance canceling system and an improved anterior segment retardance compensator, produces an optical analysis signal representing the birefringence of the retinal nerve fiber layer (RNFL) structures of the eye. The birefringence data is more accurate because of compensation for anterior segment birefringence and residual birefringence of optical components, such as, for example, the beam splitters, lenses, scanners and retarders. An electrical analysis signal representing a large (20 by 40 degrees) retardance map is produced and evaluated by an artificial neural network to produce an analysis classification signal representing the contribution of Alzheimer's disease to the birefringence of the retinal layer corresponding to the relationship of the electrical analysis signal to an analysis signal database.

Owner:CARL ZEISS MEDITEC INC

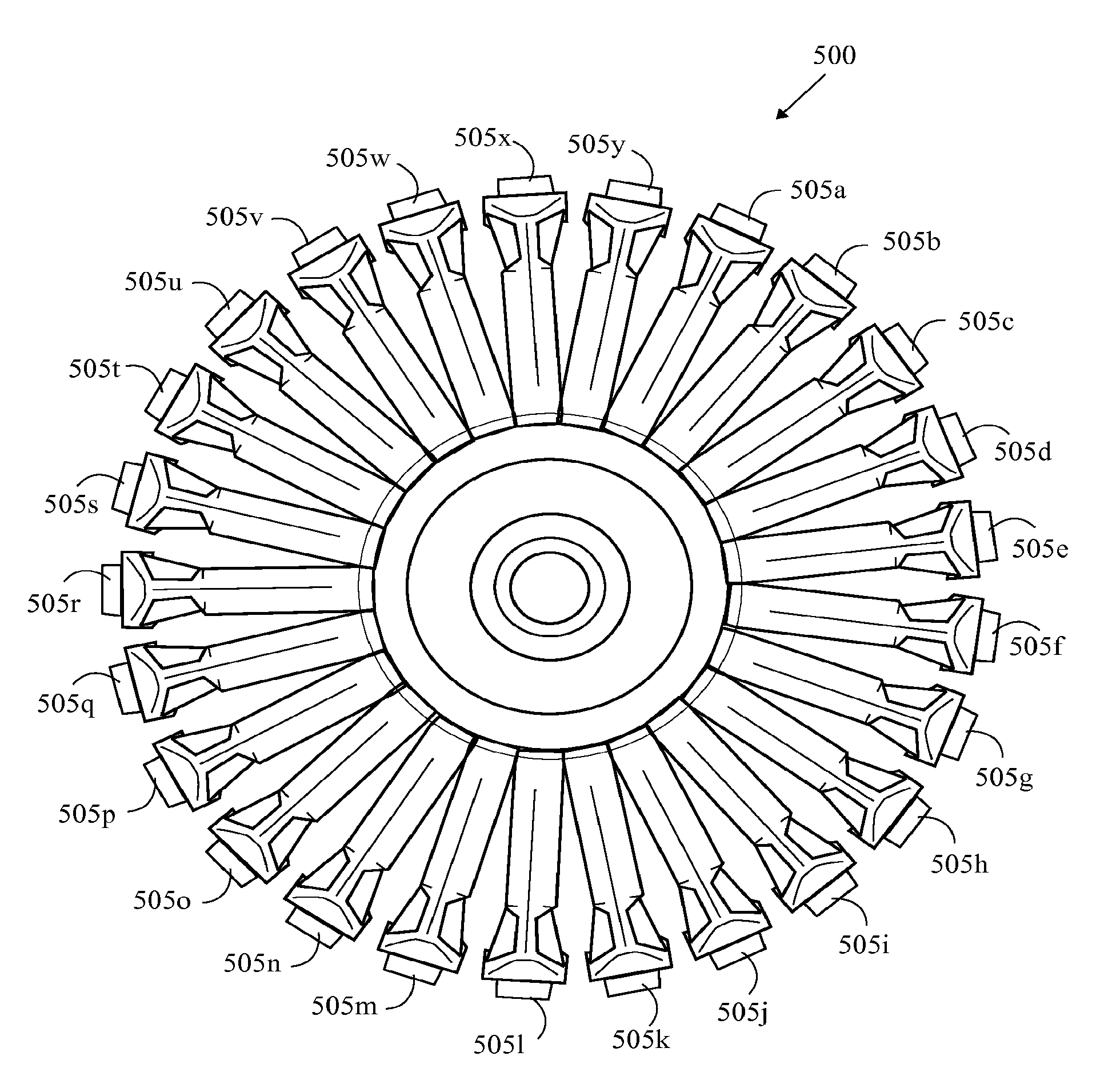

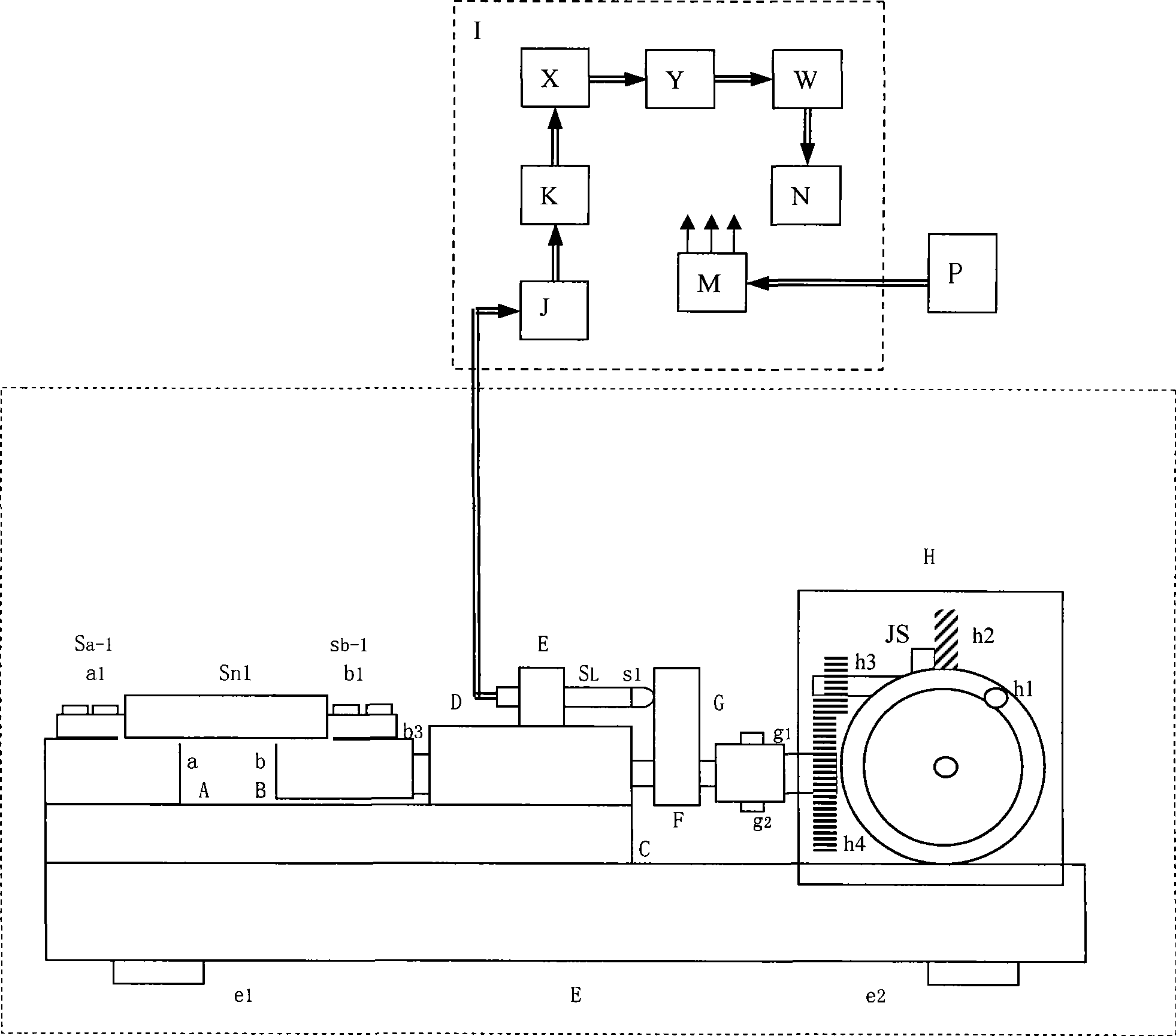

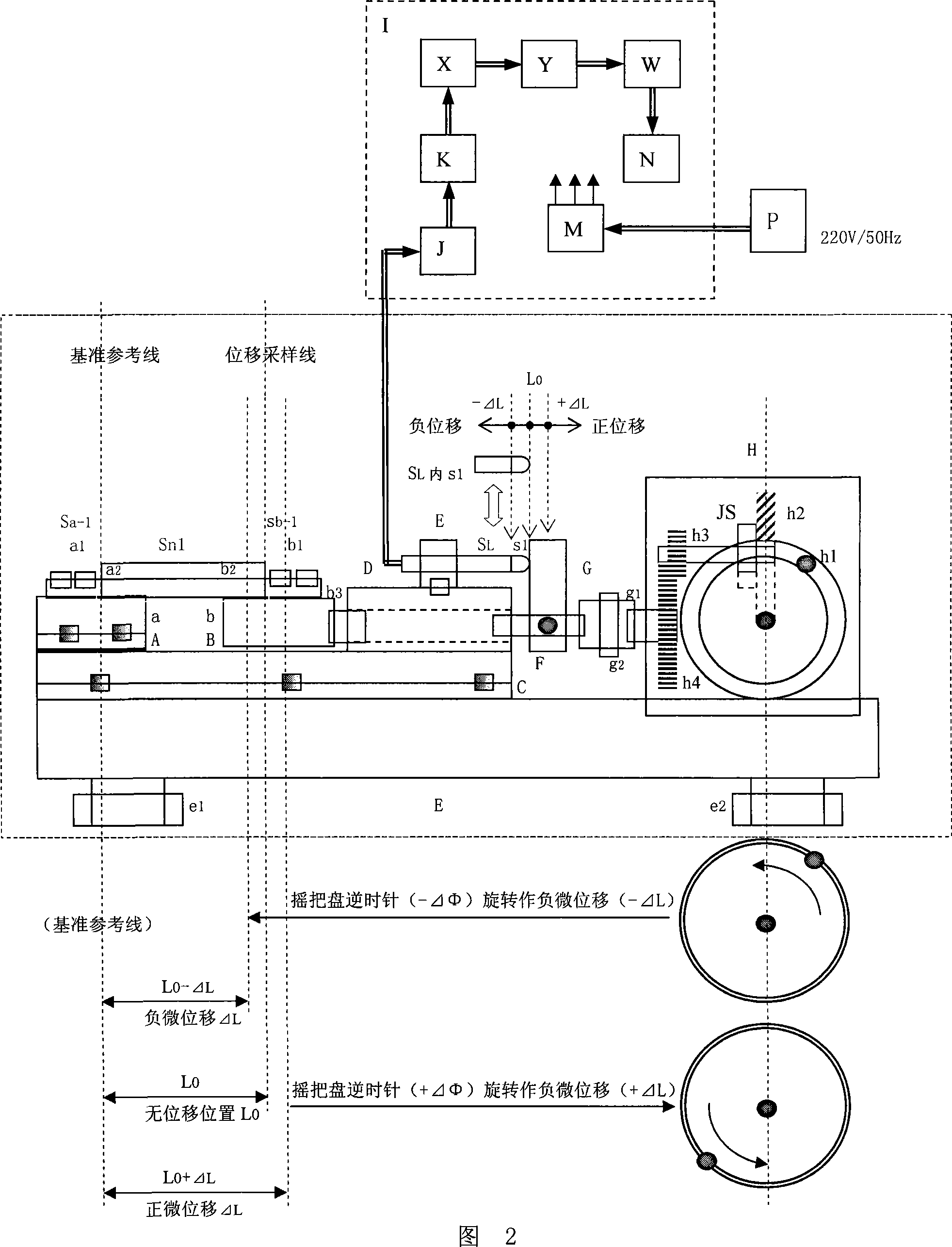

High precision micro displacement detection device for demarcating machinery deformation amount and measurement method thereof

InactiveCN101387489AHigh sensitivityQuick responseUsing electrical meansElectrical/magnetic solid deformation measurementReduction driveEngineering

The invention relates to a device for detecting mechanical micrometric displacement and a method for measuring the same, in particular to a high precision micrometric displacement detection device for labeling the mechanical micro-variation of a special micrometric displacement sensor. An electric analyzing part consists of a shell, a rectification voltage stabilizer, a phase discriminator, a high frequency oscillator, an analog-digital converter, a logic processor, a micrometric displacement display, an inductive micrometric displacement sensor and the like. A mechanical analyzing part consists of a mechanical pedestal part, a high multiplying factor speed reducer, a micrometric displacement generating part and the like. When the measurement is started, the high multiplying factor speed reducer is rocked and rotated to modulate a system to the zero displacement, the displacement variation of the rotation angle of a crank plate is changed from the range of between delta phi below zero and delta phi into the range of between delta L below zero and delta L, and is used as the mechanical input quantity of the special micrometric displacement sensor and detection touch iron of the inductive micrometric displacement sensor through a correlative transmission device acting on two ends of the special micrometric displacement sensor. The device has the advantages of simple structure, strong reliability, high sensitivity and long service life.

Owner:赵亮

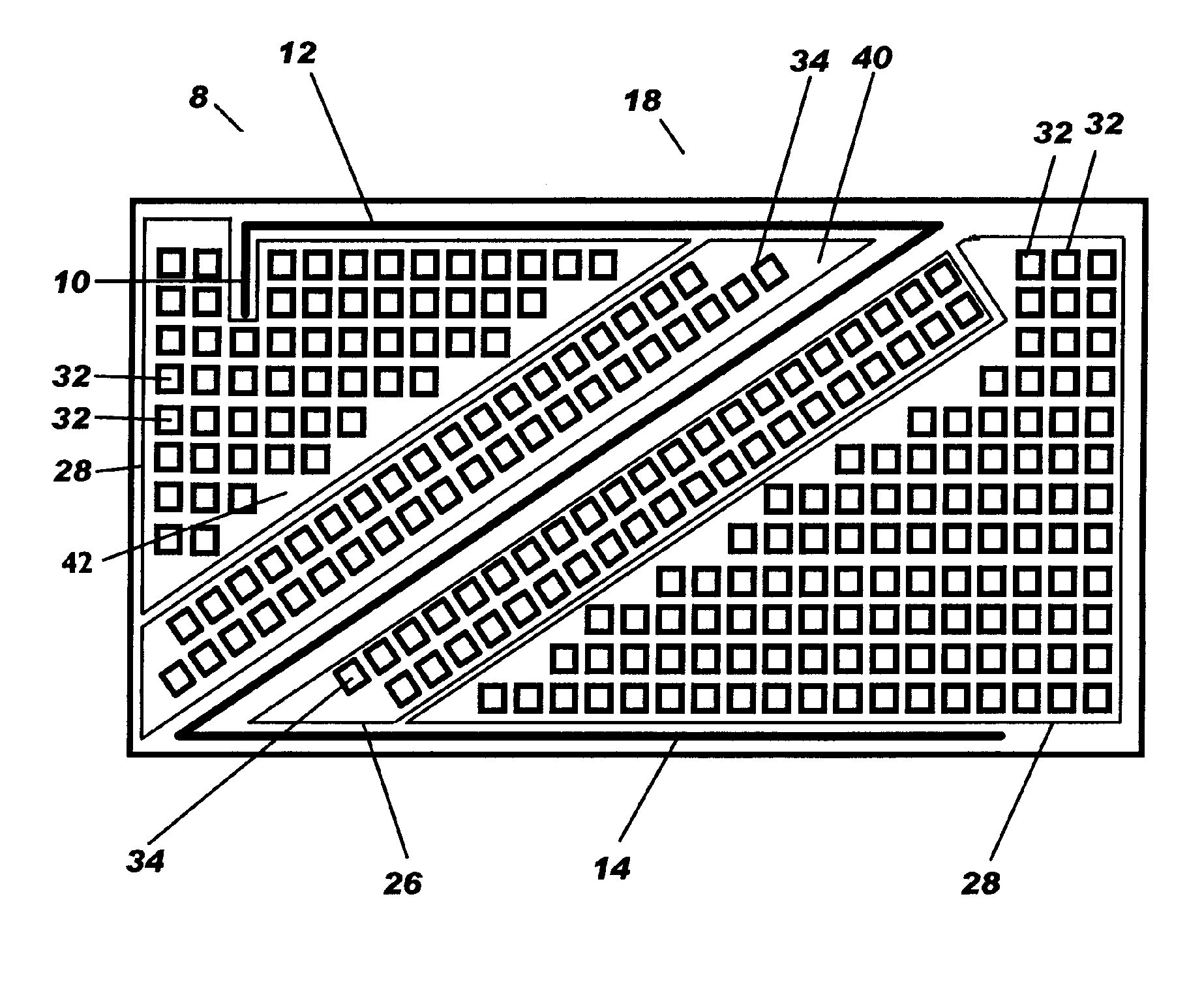

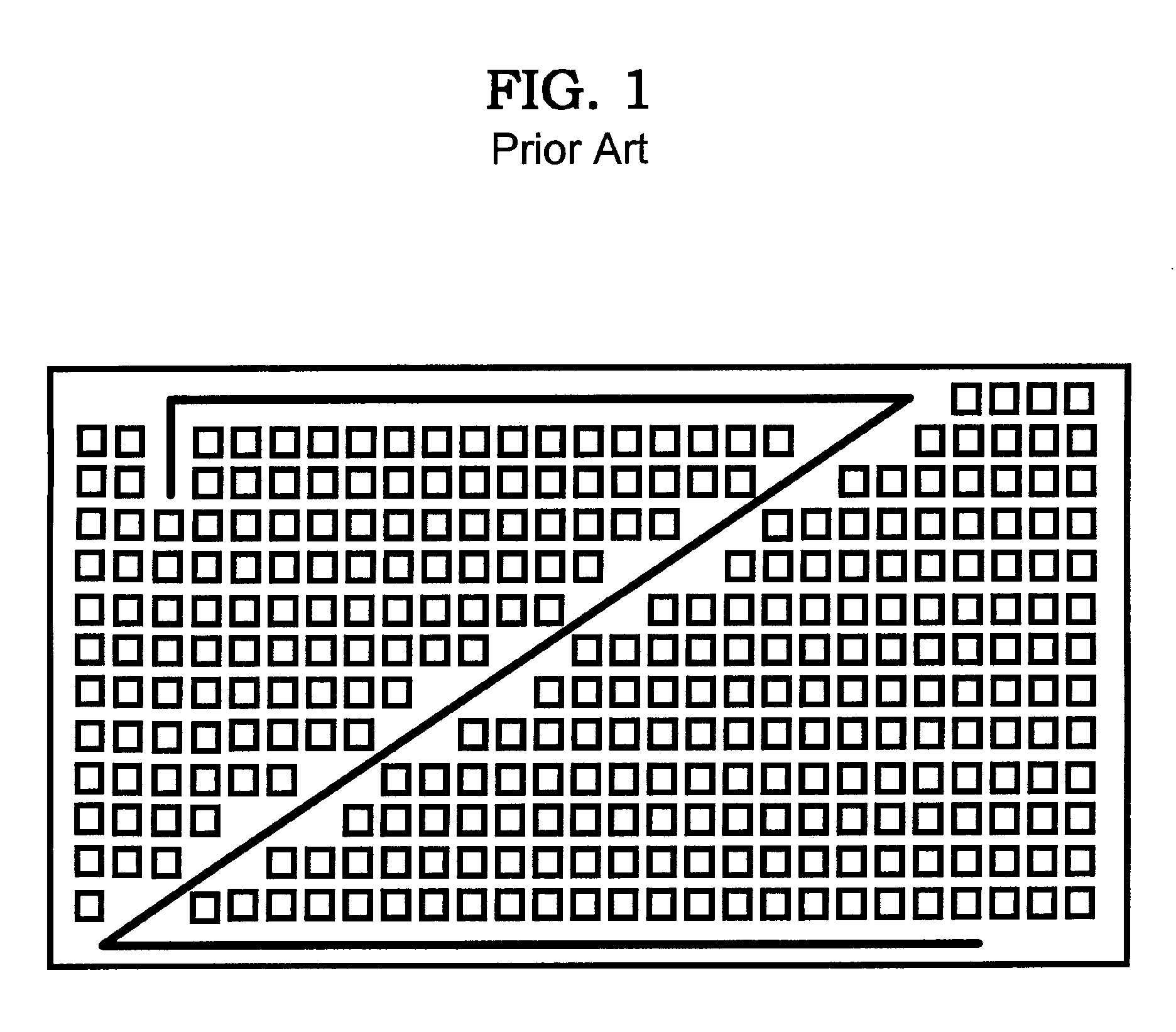

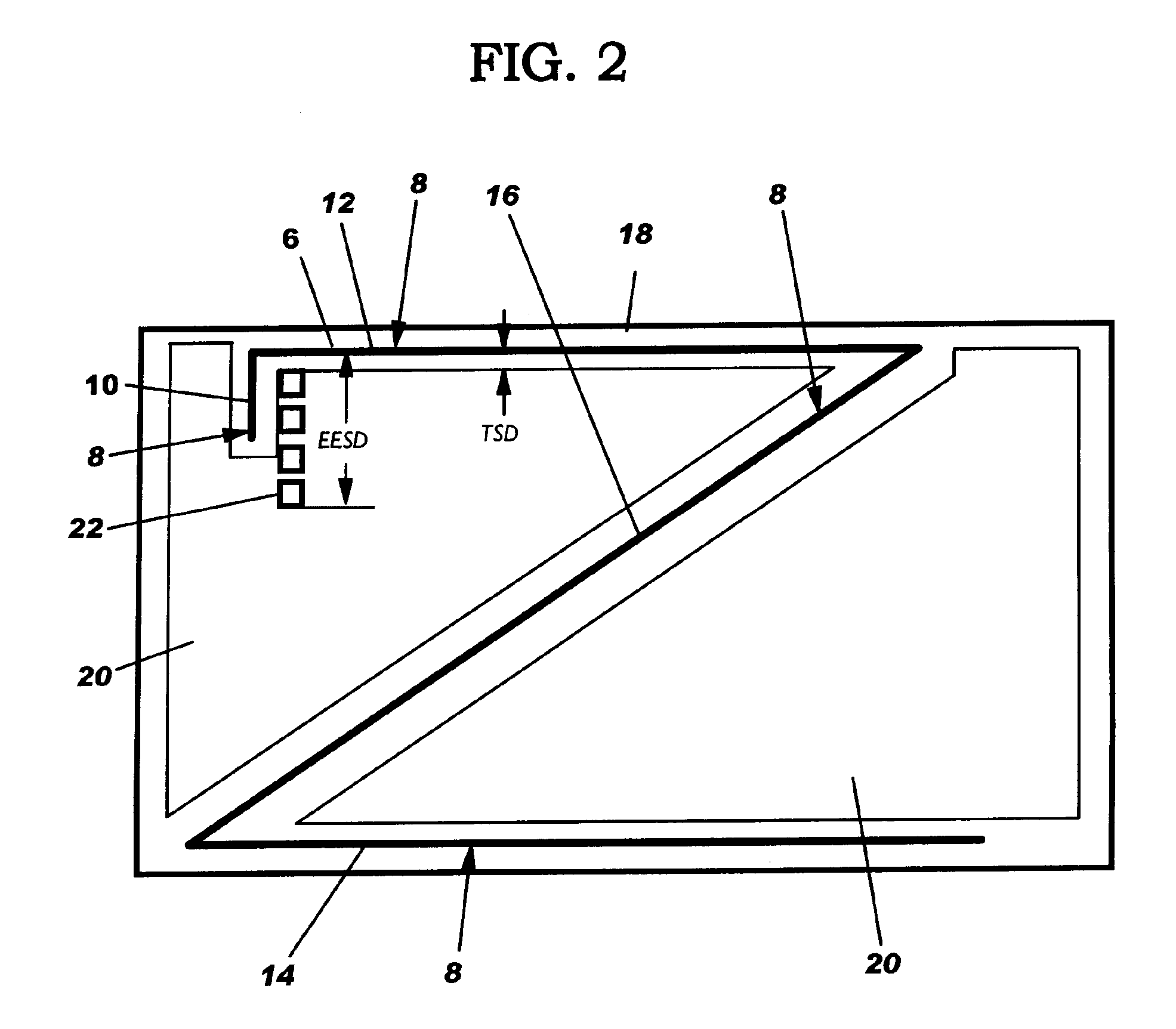

IC tiling pattern method, IC so formed and analysis method

InactiveUS20050273744A1Semiconductor/solid-state device detailsDetecting faulty computer hardwareAnalysis methodIntegrated circuit

The invention provides a method for providing an integrated circuit (6) having a substantially uniform density between parts (10, 12, 14 and 16) of the IC that are non-orthogonally angled. In particular, the invention provides fill tiling patterns (32, 34) oriented substantially parallel to electrical structure regardless of their angle. A method of electrical analysis based on this provision is also provided as is a related program product.

Owner:AURIGA INNOVATIONS INC

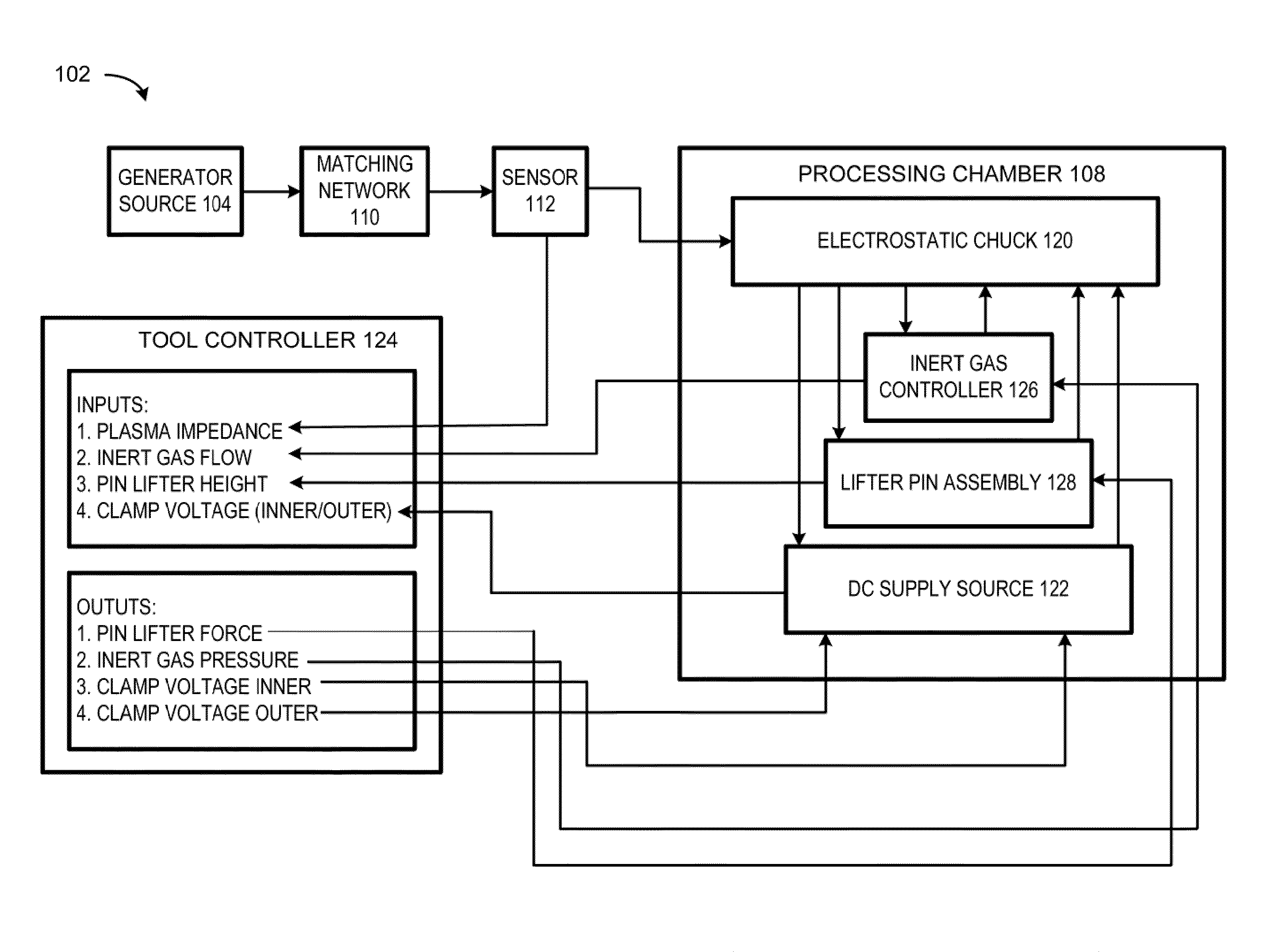

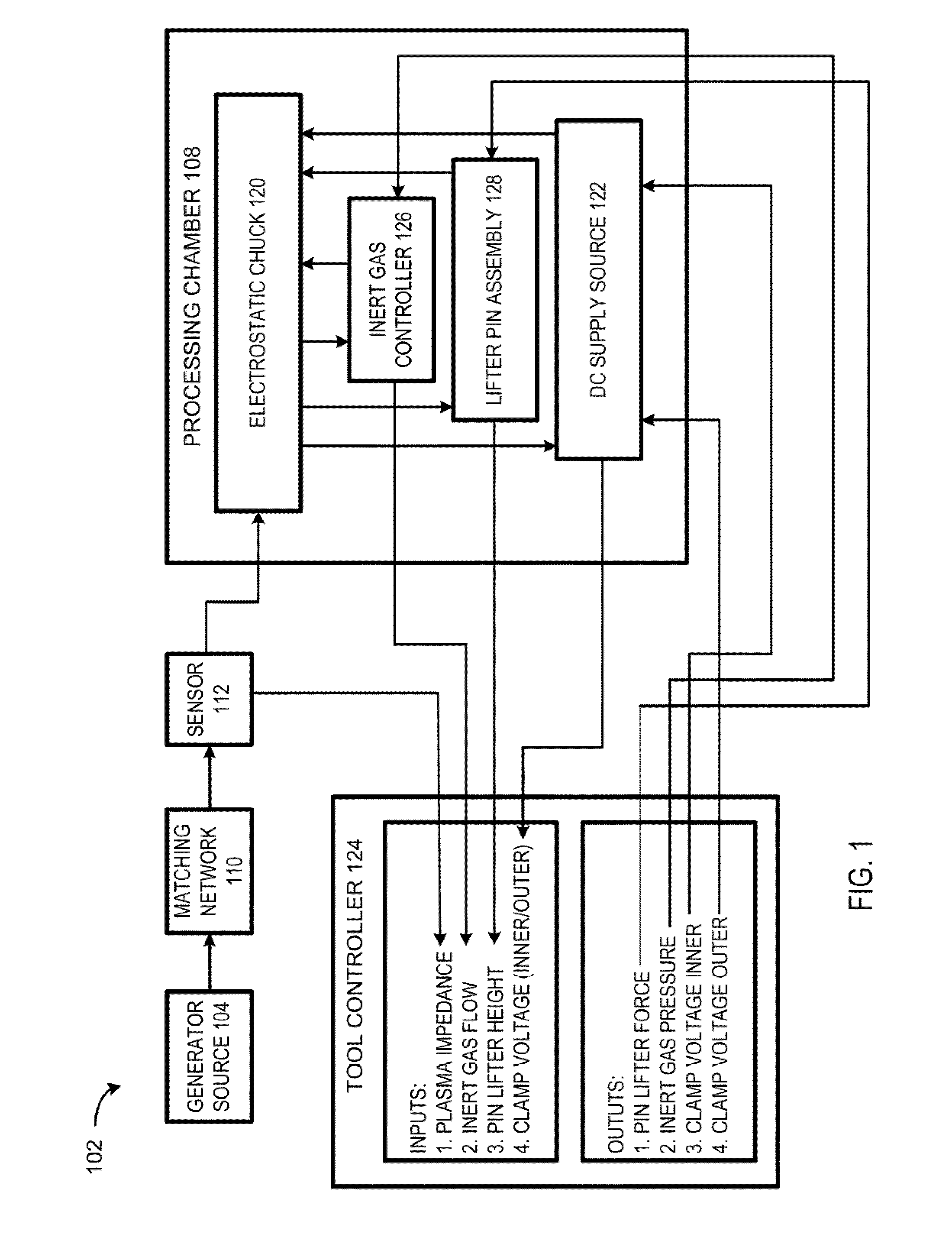

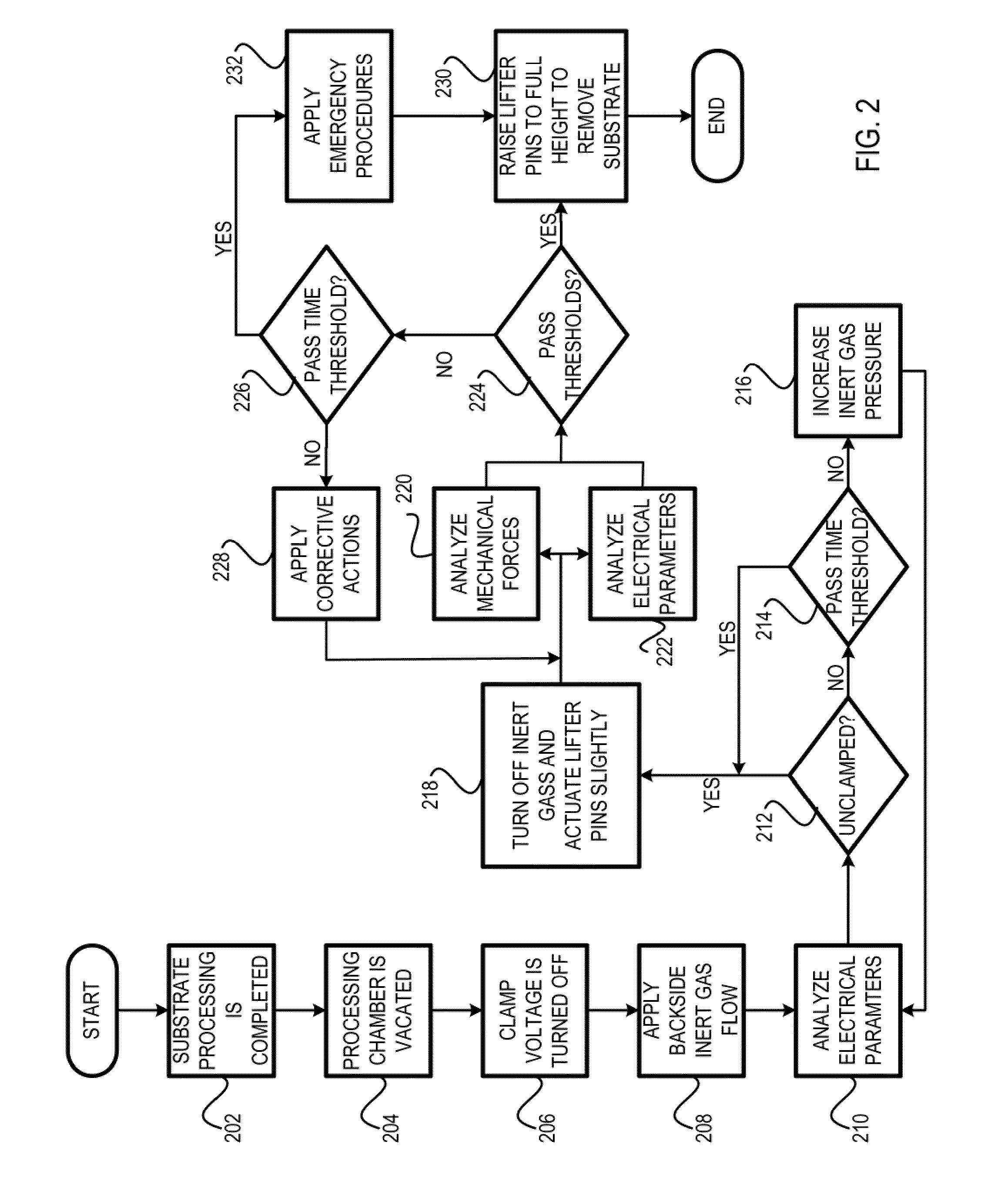

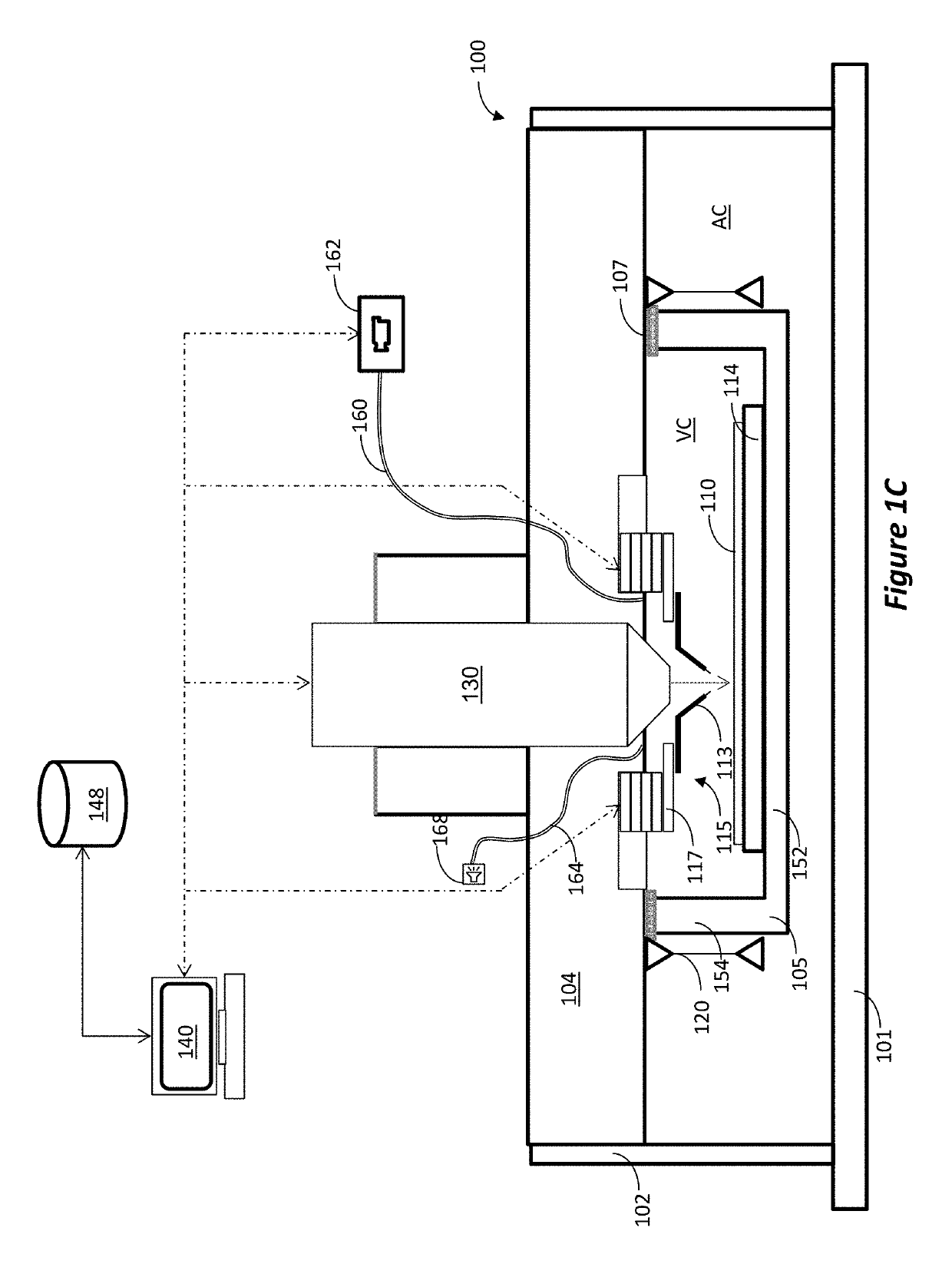

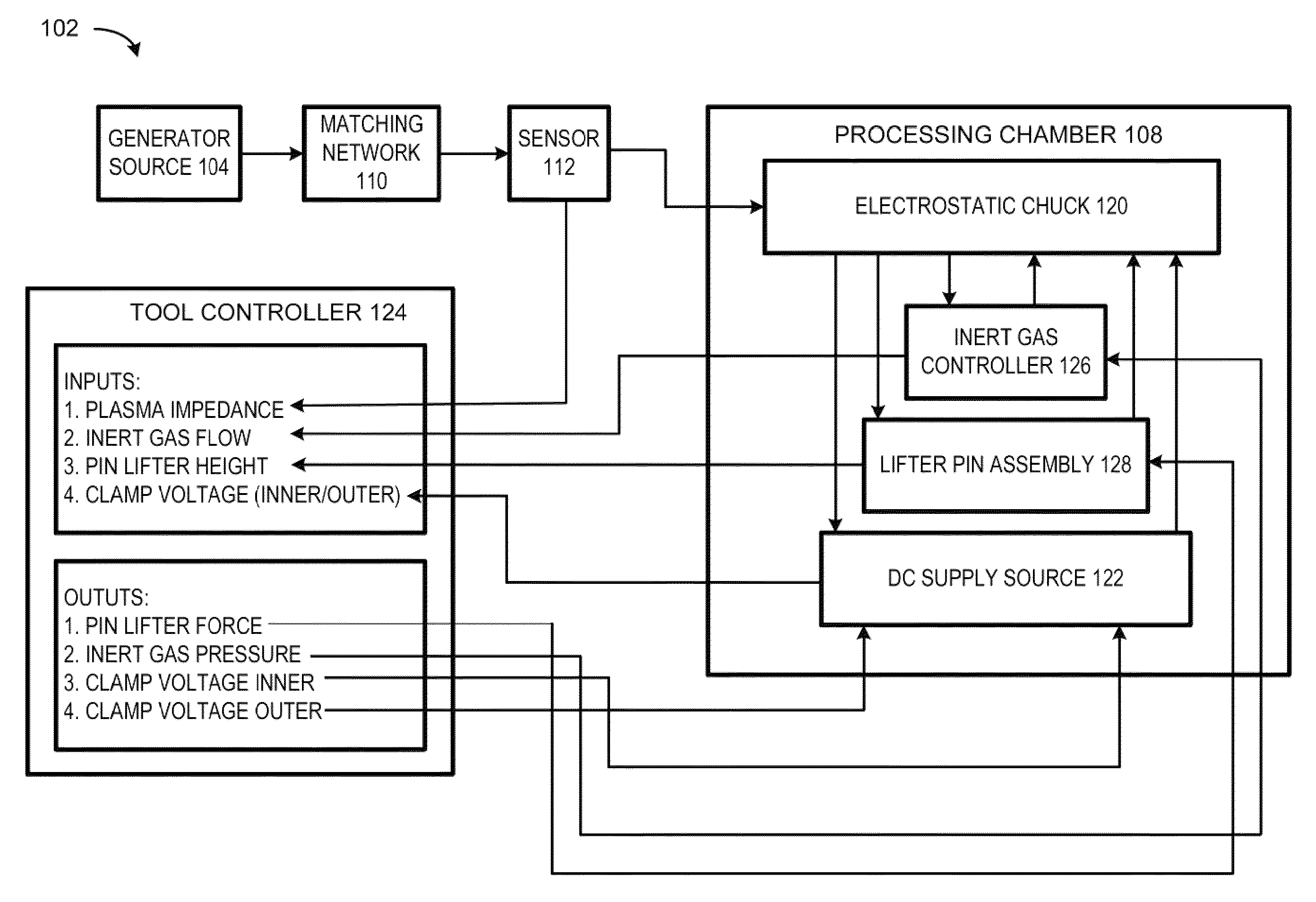

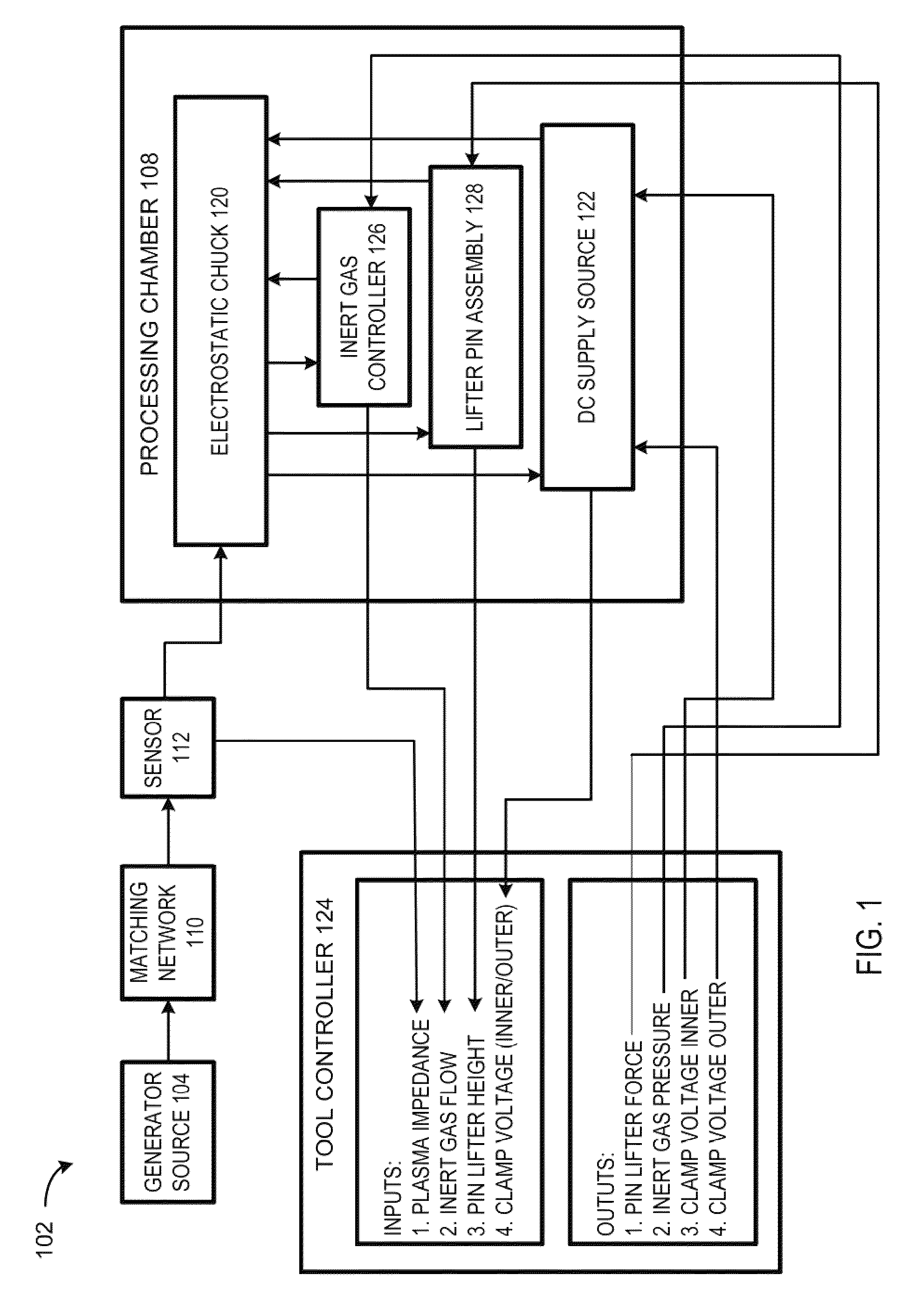

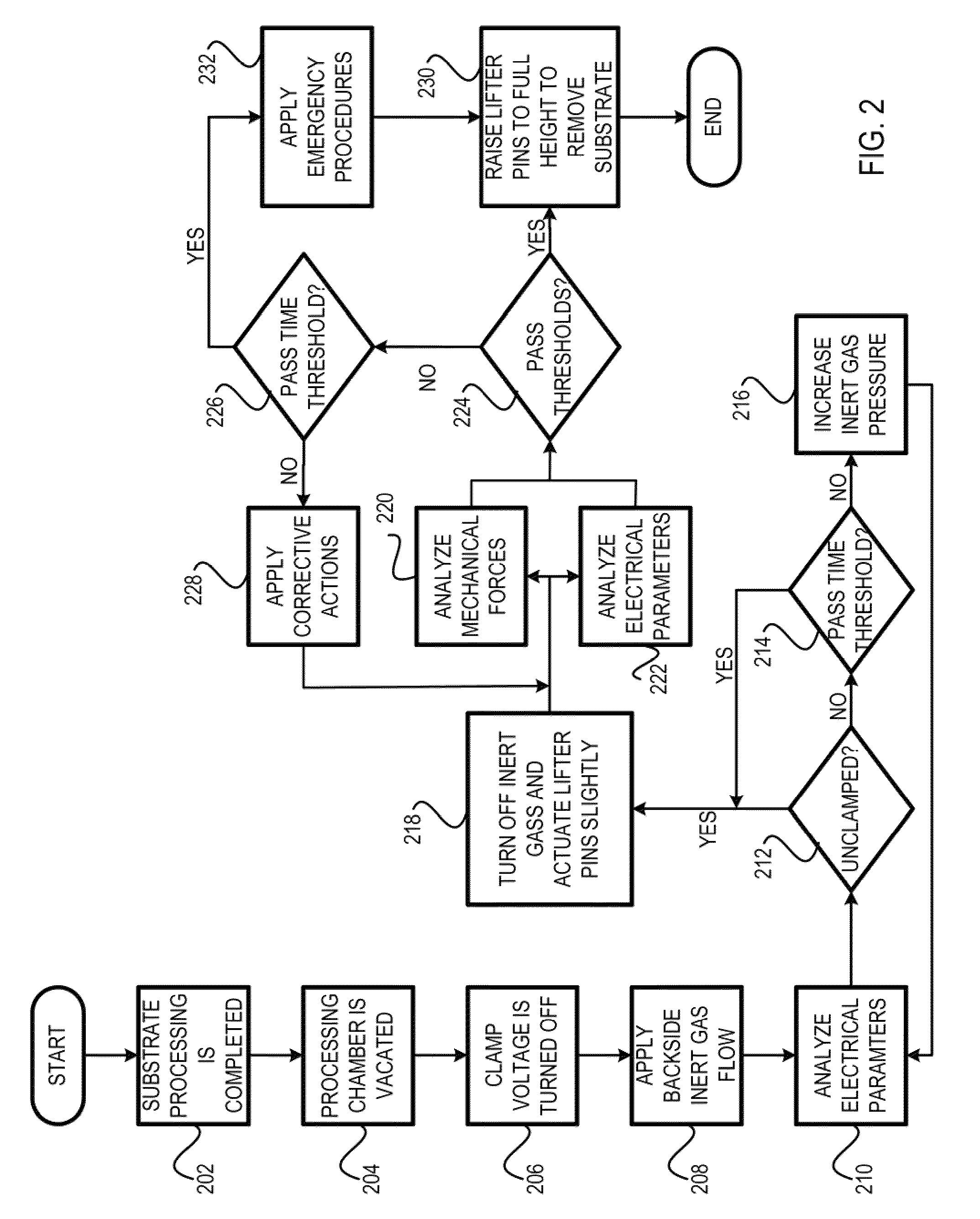

Methods and arrangement for plasma dechuck optimization based on coupling of plasma signaling to substrate position and potential

A method for optimizing a dechuck sequence, which includes removing a substrate from a lower electrode. The method includes performing an initial analysis to determine if a first set of electrical characteristic data of a plasma formed during the dechuck sequence traverses a threshold values. If so, turning off the inert gas. The method also includes raising the lifter pins slightly from the lower electrode to move the substrate in an upward direction. The method further includes performing a mechanical and electrical analysis, which includes comparing a first set of mechanical data, which includes an amount of force exerted by the lifter pins, against a threshold value. The mechanical and electrical analysis also includes comparing a second set of electrical characteristic data against a threshold value. If both traverse the respective threshold value, removes the substrate from the lower electrode since a substrate-released event has occurred.

Owner:LAM RES CORP

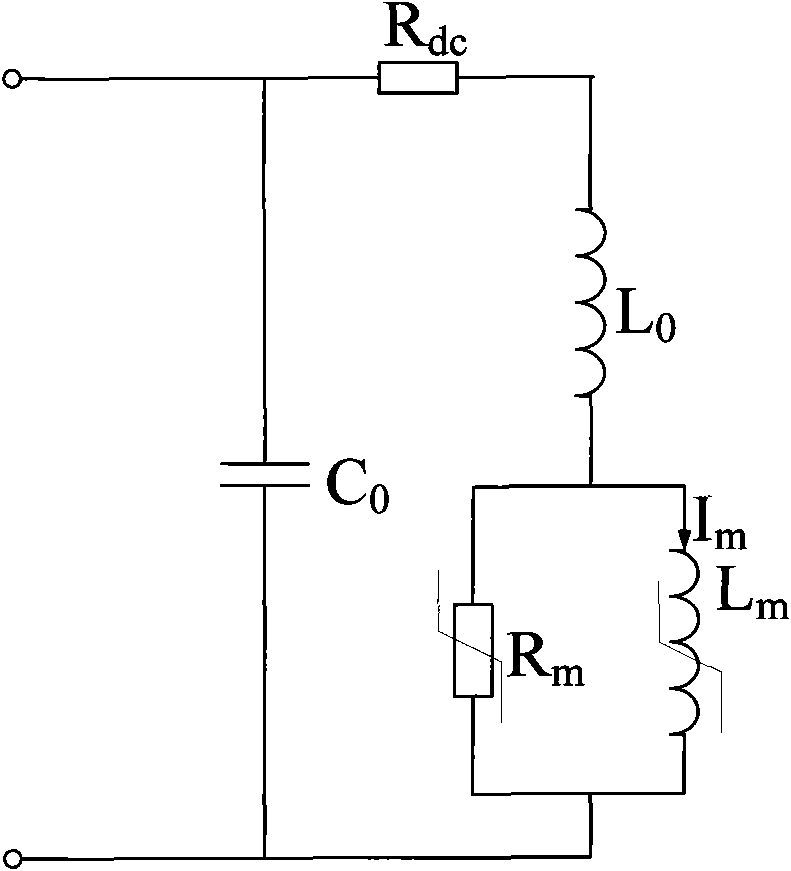

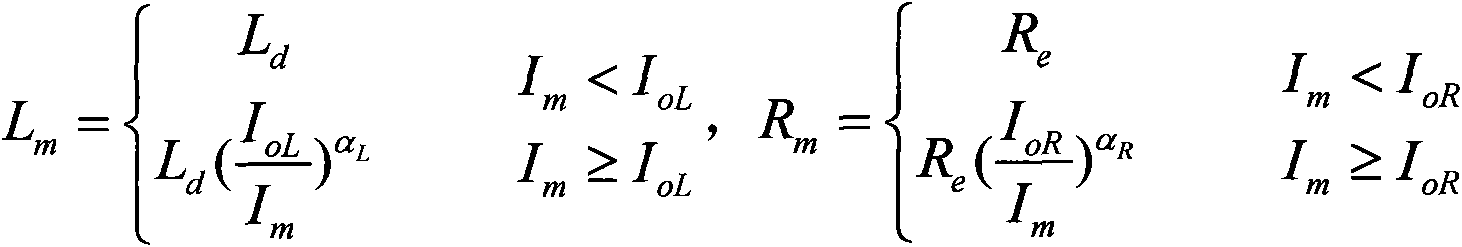

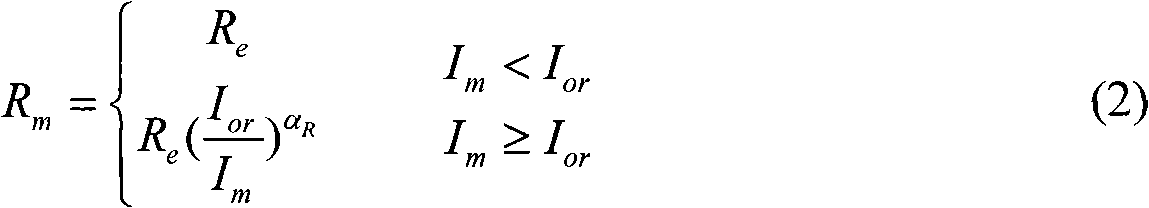

Analytical model for saturable reactor for converter valve

ActiveCN101930492APhysical concepts are clearClear expressionSpecial data processing applicationsElectrical resistance and conductanceCapacitance

The invention provides an analytical model for a saturable reactor for a converter valve. The saturable reactor for the converter valve consists of a coil and an iron core; and the working state of the iron core has a linear stage and a nonlinear stage under rated operation. In order to better perform electrical design and electrical analysis on the saturable reactor, the invention provides an analytical model for the saturable reactor for the converter valve. The analytical model comprises a coil resistance, a coil inductance, a core inductance, a core resistance, a terminal capacitance and other parameters. Corresponding electrical parameters of saturable reactors with different shapes and dimensions can be calculated. The analytical model has the advantages of clear physical conception, and capacities of easily acquiring each parameter needed in the model through a real object and providing a foundation for deep analysis of the saturable reactor.

Owner:CHINA ELECTRIC POWER RES INST +1

I/O circuit power routing system and method

InactiveUS7200829B2Computer aided designSoftware simulation/interpretation/emulationIntegratorEngineering

A method of determining widths and / or routes of I / O power routes between one or more power distribution networks and a plurality of I / O circuits based on IR chop, electromigration, and electrostatic discharge electrical requirements. The method includes initially routing the I / O power routes and then iteratively analyzing the I / O power routes and iteratively incrementing the width of each power route that fails one or more of the electrical requirements until all power routes meet all electrical requirements. Once all power routes meet the electrical requirements, power routing is performed again to re-route any power routes as necessary to accommodate their wider widths. The method may be implemented in a system that includes a power routing tool, an electrical analysis tool, and a tool integrator tat implements an integrated power routing algorithm.

Owner:INT BUSINESS MASCH CORP

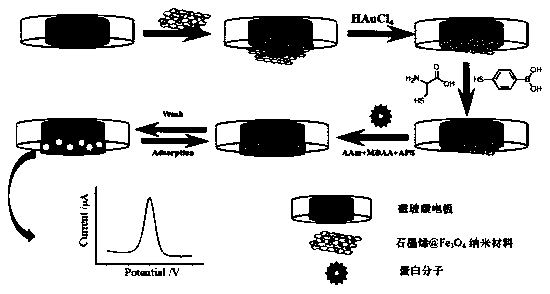

Fabrication method for protein electrochemical imprint sensor of modified magnetic electrode by one-step deposition method

ActiveCN109085225AEasy to makeReduce consumptionMaterial analysis by electric/magnetic meansProtein targetProtein molecules

The invention discloses a fabrication method for a protein electrochemical imprint sensor of a modified magnetic electrode by a one-step deposition method, and relates to the technical field of electrical analysis chemistry and protein recognition sensors. The fabrication method comprises the steps of 1) preparing a graphene@Fe3O4 nanometer composite material; 2) fabricating a graphene@Fe3O4@Au modified magnetic electrode by the one-step electrodeposition method; 3) introducing boric acid, amino and carboxyl active group into a surface of the modified magnetic electrode so that a plurality ofrecognition sites are provided for protein imprint; 4) pre-assembling protein; 5) performing electrochemical polymerization on a protein imprint membrane; and 6) washing template protein with an eluent so as to build the protein molecular imprint electrochemical sensor. The magnetic modified electrode fabricated by the method is beneficial for introducing the active group, increasing the recognition sites, improving selectivity, expanding surface area and improving conductivity of electrode surface, the built protein imprint electrochemical sensor is high in sensitivity and can be used repeatedly, and target protein can be specially recognized.

Owner:MINJIANG UNIV

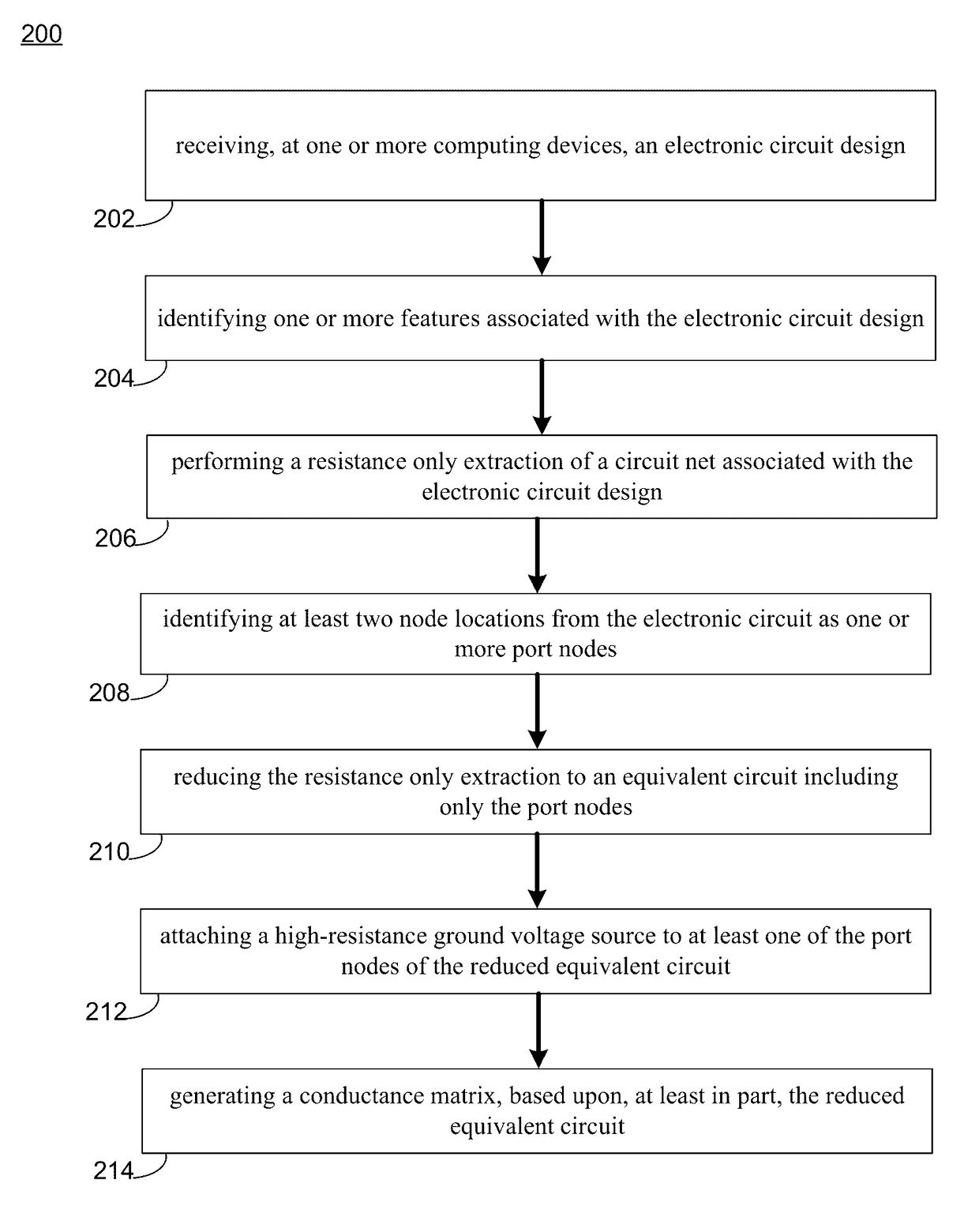

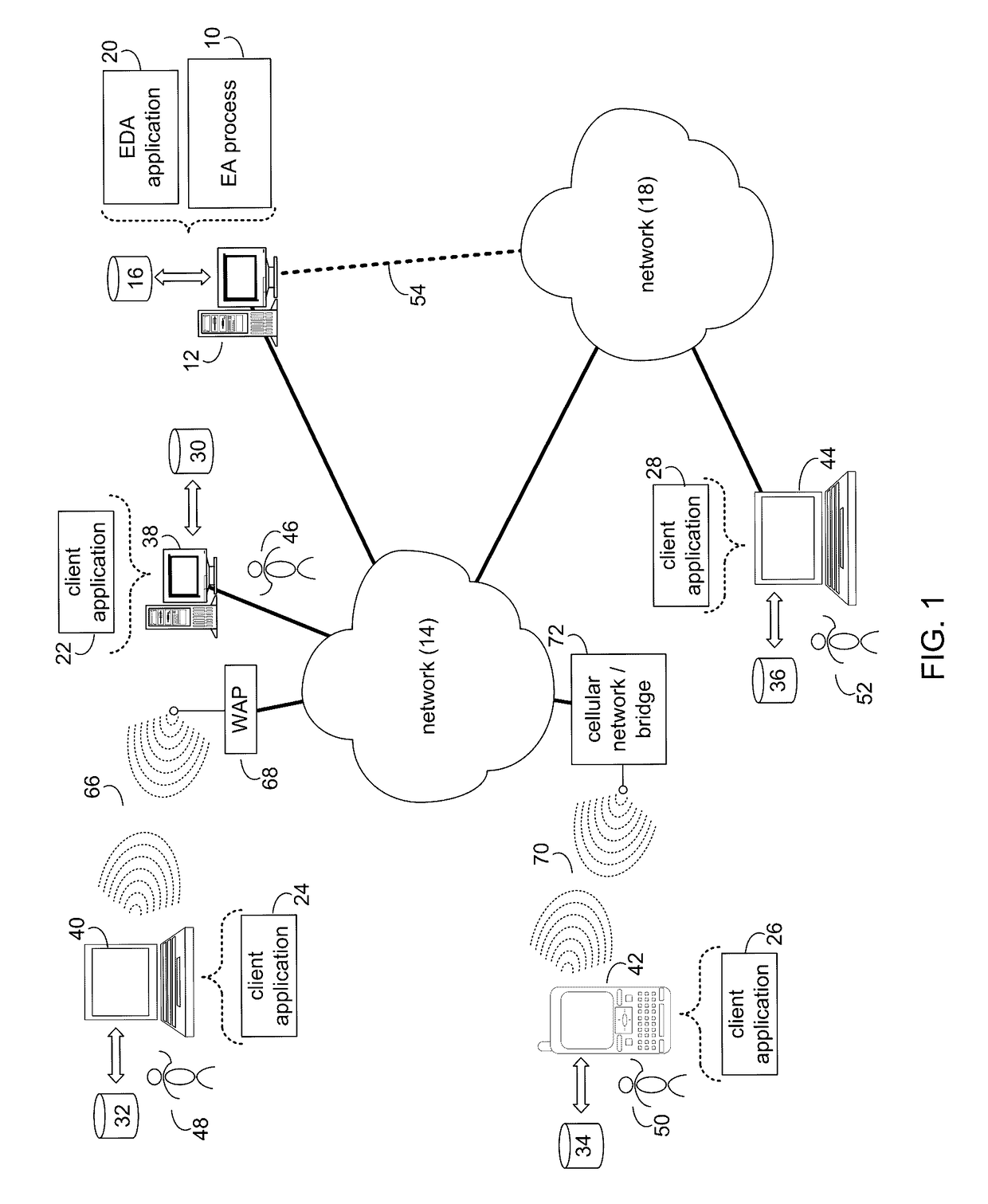

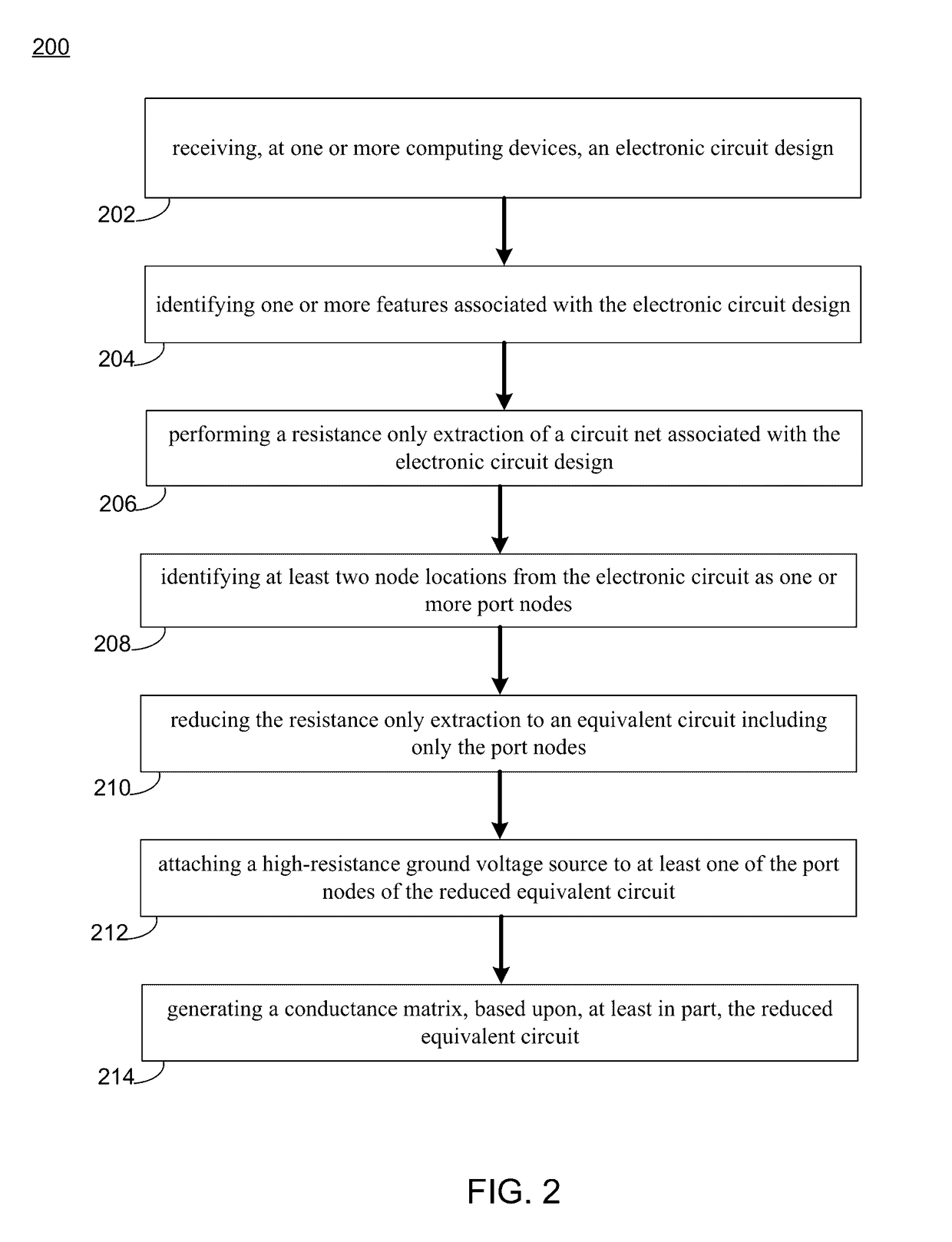

Electrical analysis process

ActiveUS9619604B1Reducing resistance only extractionCAD circuit designSpecial data processing applicationsElectrical resistance and conductanceHigh resistance

The present disclosure relates to a system and method for determining an effective electrical resistance in an electronic circuit design. Embodiments may include receiving, at one or more computing devices, an electronic circuit design and identifying one or more features associated with the electronic circuit design. Embodiments may also include performing a resistance only extraction of a circuit net associated with the electronic circuit design and identifying at least two node locations from the electronic circuit as one or more port nodes. Embodiments may further include reducing the resistance only extraction to an equivalent circuit including only the port nodes and attaching a high-resistance ground voltage source to at least one of the port nodes of the reduced equivalent circuit. Embodiments may also include generating a conductance matrix, based upon, at least in part, the reduced equivalent circuit.

Owner:CADENCE DESIGN SYST INC

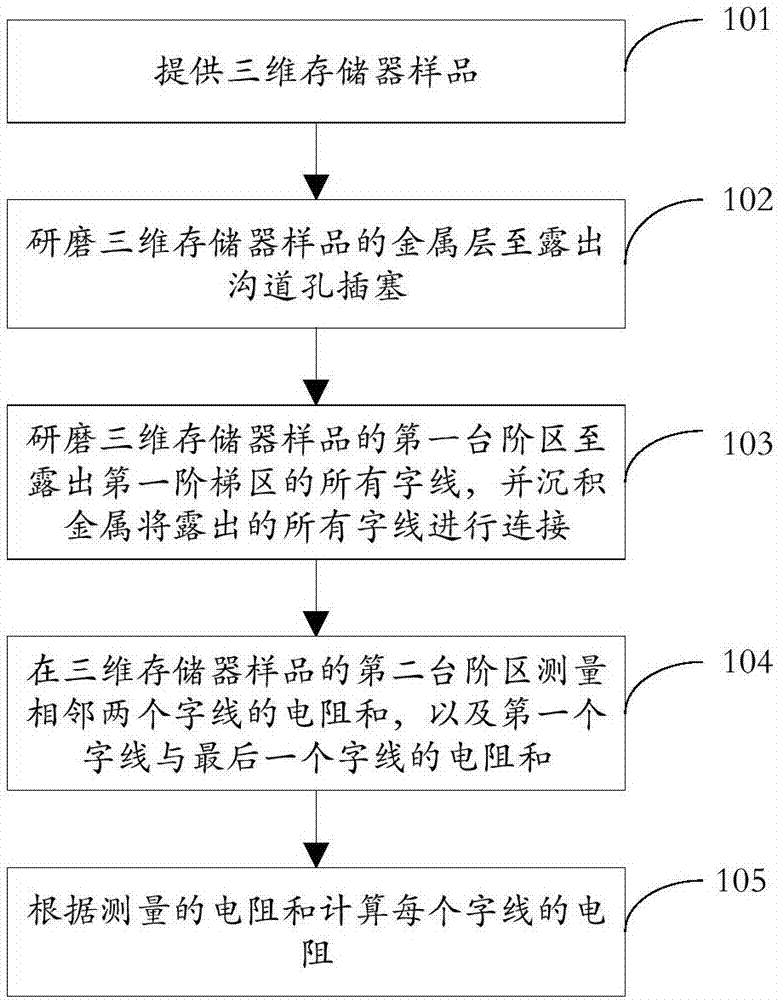

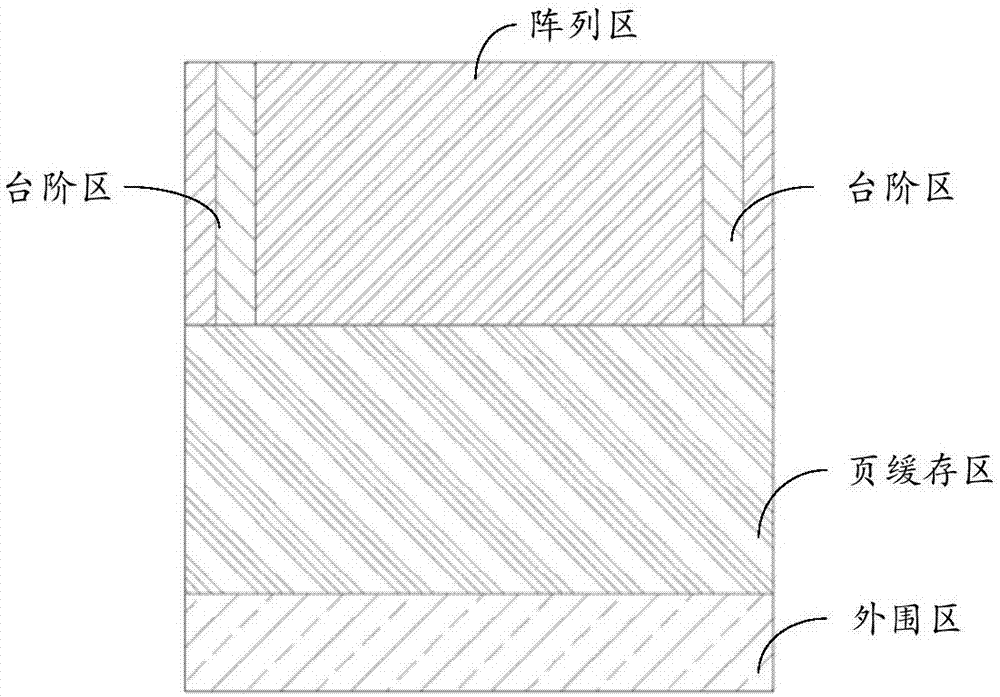

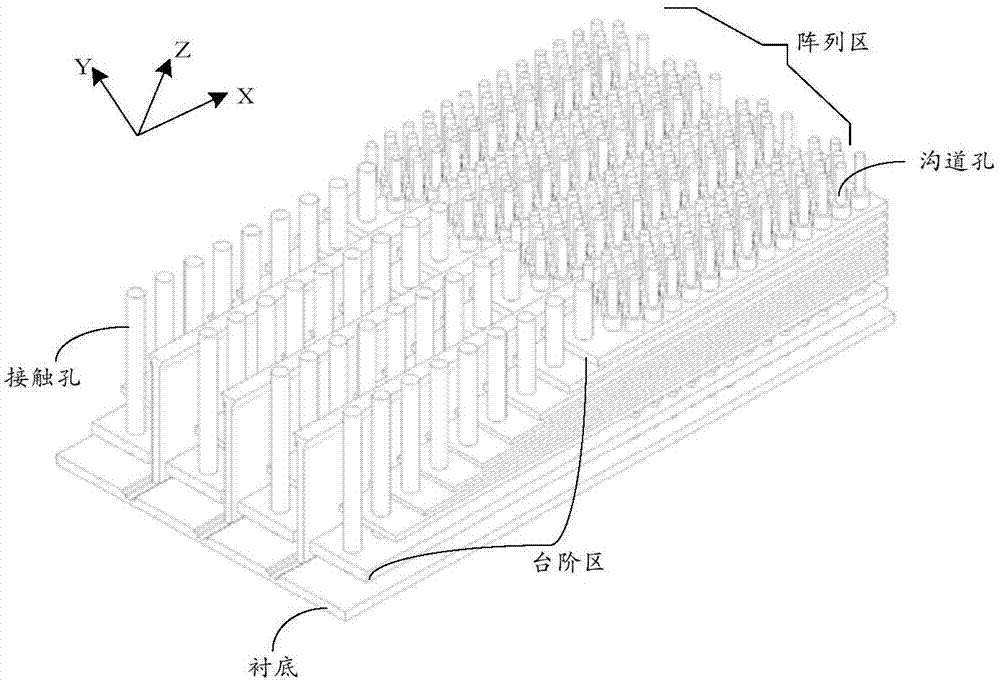

Measurement method of word line resistance of 3D NAND

ActiveCN107993948AAccurate measurementSuccessfully developedSemiconductor/solid-state device testing/measurementResistance/reactance/impedenceLine resistanceComputer science

The invention discloses a measurement method of word line resistance of a 3D NAND, and belongs to the technical field of a semiconductor. The measurement method comprises the steps of providing a 3D NAND sample (there is no via in an array region); performing grinding on a metal layer of the 3D NAND sample until channel hole plugs appear; performing grinding on a first stage region of the 3D NANDsample until all word lines in the first stage region are exposed, and performing metal depositing to enable all exposed word lines to be connected; performing measurement on the sum of resistance oftwo adjacent word lines in a second stage region of the 3D NAND sample, and on the sum of resistance of the first word line and the last word line; and calculating the resistance of each word line according to the measured sum of resistance. By virtue of the measurement method, measurement of resistance of all word lines in the 3D NAND sample is realized quickly and accurately, thereby providing basis for electrical analysis of the 3D NAND and promoting smooth research and development of the 3D NAND product.

Owner:YANGTZE MEMORY TECH CO LTD

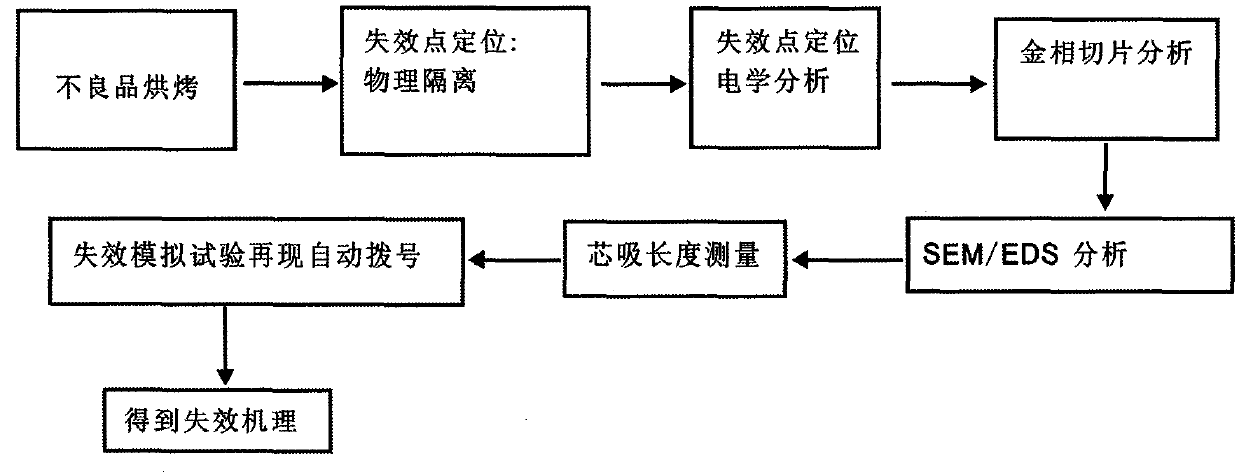

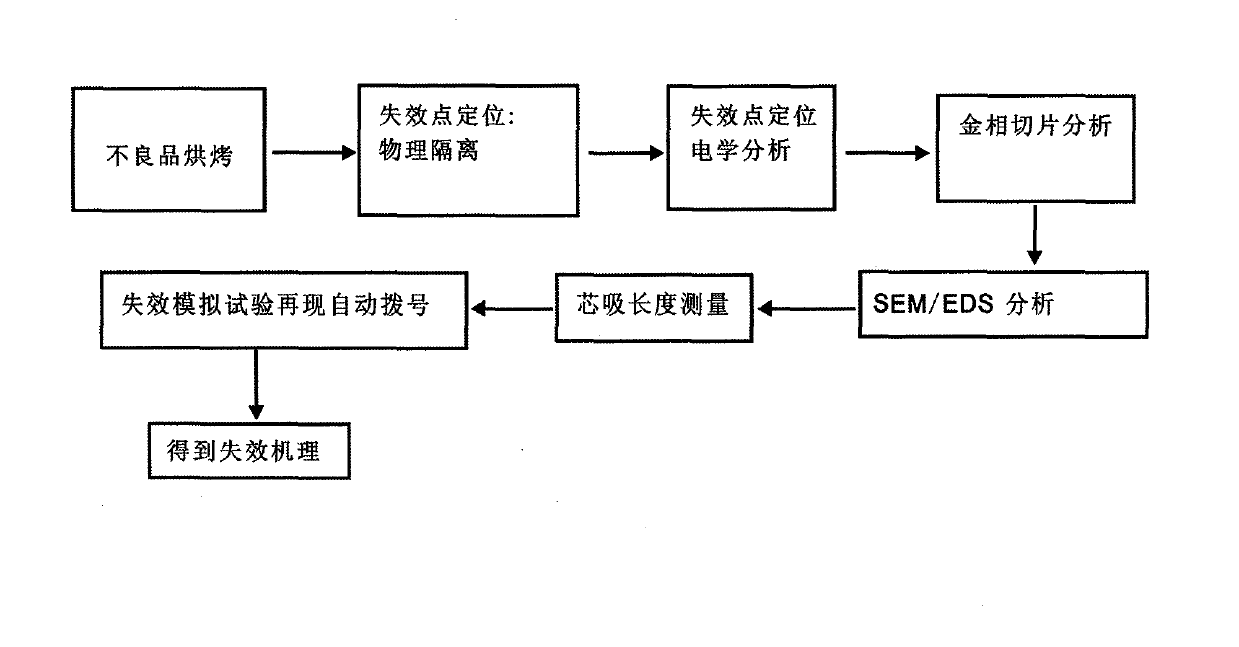

Method for detecting failure mechanism of automatic dialing of mobile phone

The invention discloses a method for detecting a failure mechanism of automatic dialing of a mobile phone, which comprises the following steps specified in the standard: baking, physical isolation of failure point locating, electrical analysis of failure point locating, and microsection analysis. The method can be used for quickly locating the failure point, so as to determine the party responsible for the failure and generate technical innovation references, thereby avoiding reoccurrence of similar failures.

Owner:SHANGHAI FALAB TEST

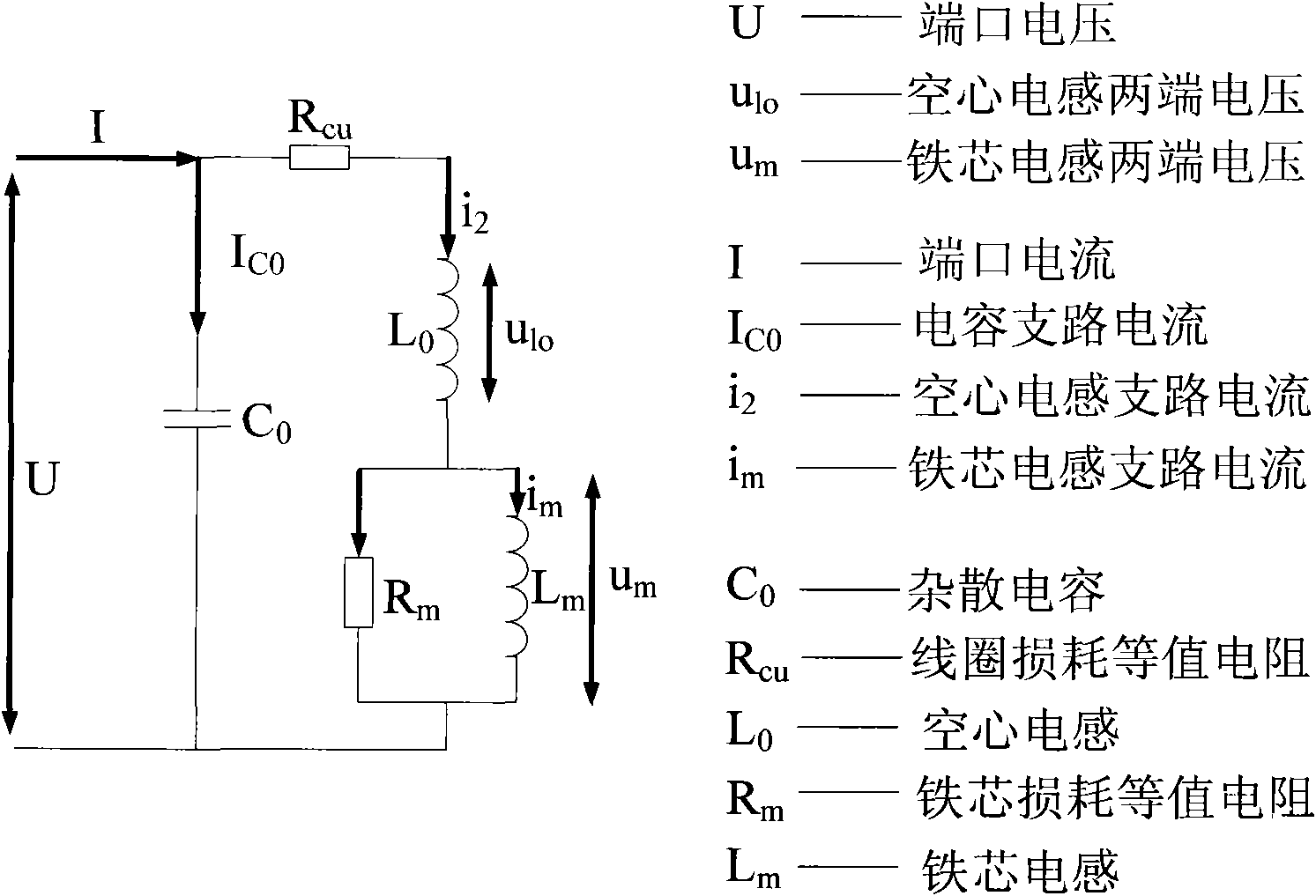

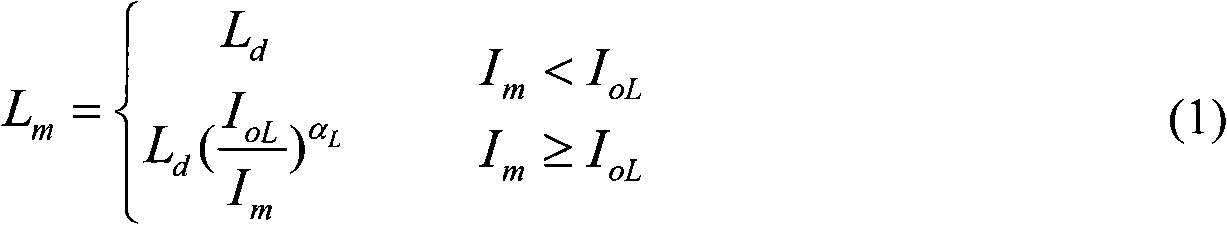

Method for modeling electrical analysis model of saturable reactor for converter valve

InactiveCN101937484ADetailed topologyExact mathematical relationshipSpecial data processing applicationsElectric powerPower electronics

The invention relates to the field of power electronics and power systems, in particular to a method for modeling an electrical analysis model of a saturable reactor for a converter valve. In the invention, on the basis of analyzing the electrical properties of a converter valve assembly and a saturable reactor, serial and parallel forms of all electrical assemblies of an equivalent circuit of the saturable reactor are provided; and on the basis of the topological relation of the equivalent circuit, nonlinear relations of two parameters of an iron core inductor and an iron core loss equivalent resistor with current flowing through an iron core inductor branch are expressed in the form of a mathematical formula. Proved by tests, the saturable reactor manufactured with the technological level at present meets the mathematical formula, thereby the scientificity of the formula is further verified.

Owner:CHINA ELECTRIC POWER RES INST +1

Method for detecting inner circuits in PCBs (printed circuit boards) by software GNENESIS

InactiveCN103116675AAvoid badAvoid scrappingSpecial data processing applicationsReliability engineeringComputer engineering

The invention relates to a method for detecting inner circuits in PCBs (printed circuit boards) by software GENESIS. The method includes opening a backup drawing in the software GENESIS, closing attributes of other circuit layers of the drawing, and reversing attributes of an inner backup layer and a pore layer; subtracting a line width value of an inner circuit of a positive plate by a minimum line width required and allowed by process, adding minimum interval required and allowed by the process to spacing of the inner circuit of a negative plate, and performing electrical analysis of the inner layer; and locating independent thin lines unsatisfactory to the process according to open circuit contacts in reports of the inner layer electrical analysis. Existence of the thin lines unsatisfactory to the process in the inner circuits of the circuit boards can be judged accurately and quickly by the method, correction is made timely before production, defectiveness and scrappage of formed products are avoided, and cost is saved for manufactures effectively.

Owner:VICTORY GIANT TECH HUIZHOU CO LTD

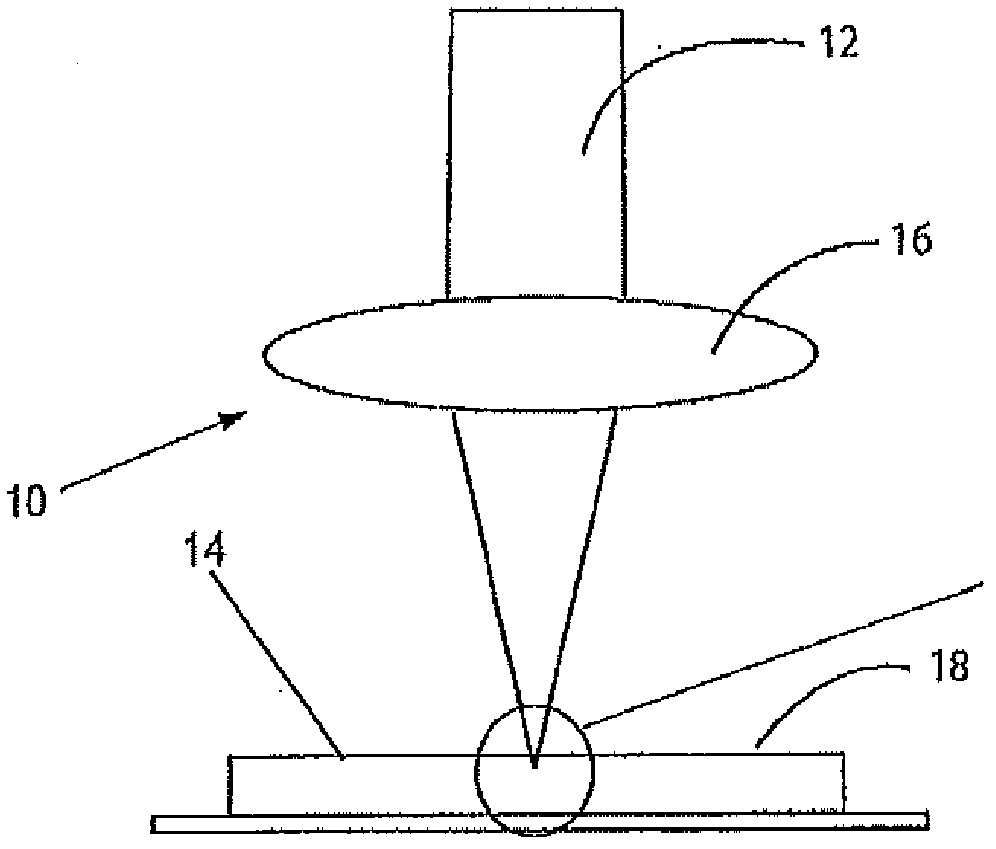

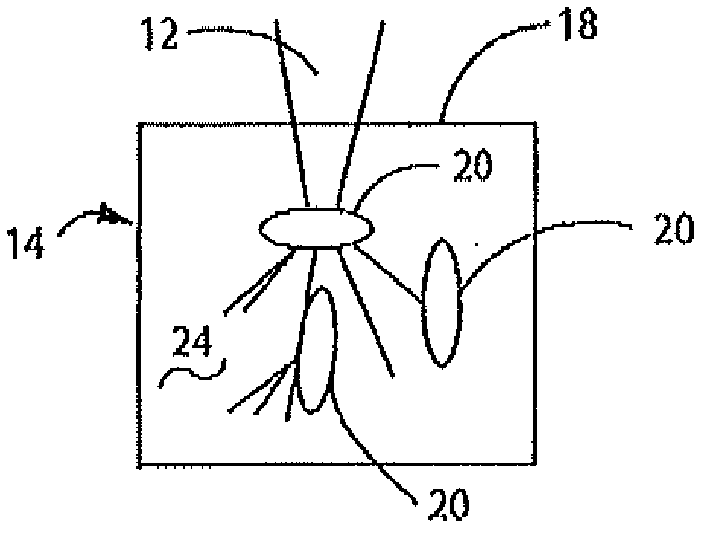

Method and system for exposing delicate structures of a device encapsulated in a mold compound

InactiveCN102714194ASemiconductor/solid-state device detailsSolid-state devicesElectricityCompound a

A system utilizes a laser to remove the mold compound of an IC without damaging the internal die, wire leads, solder connections and any other critical structures encapsulated within the mold compound, thereby leaving them available for the provisional and electrical analysis. A laser beam is focused through appropriate optics onto a plane corresponding to the surface of an IC. A layer of material which is opaque at the wave length of the laser beam is applied at the surface of the IC chip to be ablated prior to each pass of the laser. A spray nozzle may be provided to move in synchronous motion ahead of the laser being to apply coat of the opaque material.

Owner:CONTROL LASER

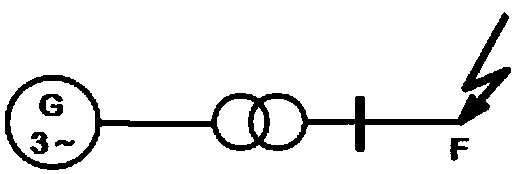

Short-circuiting current analysis system and analysis method thereof

InactiveCN107561399AShort circuit fault in timeTimely detectabilityFault locationCurrent analysisShort circuit analysis

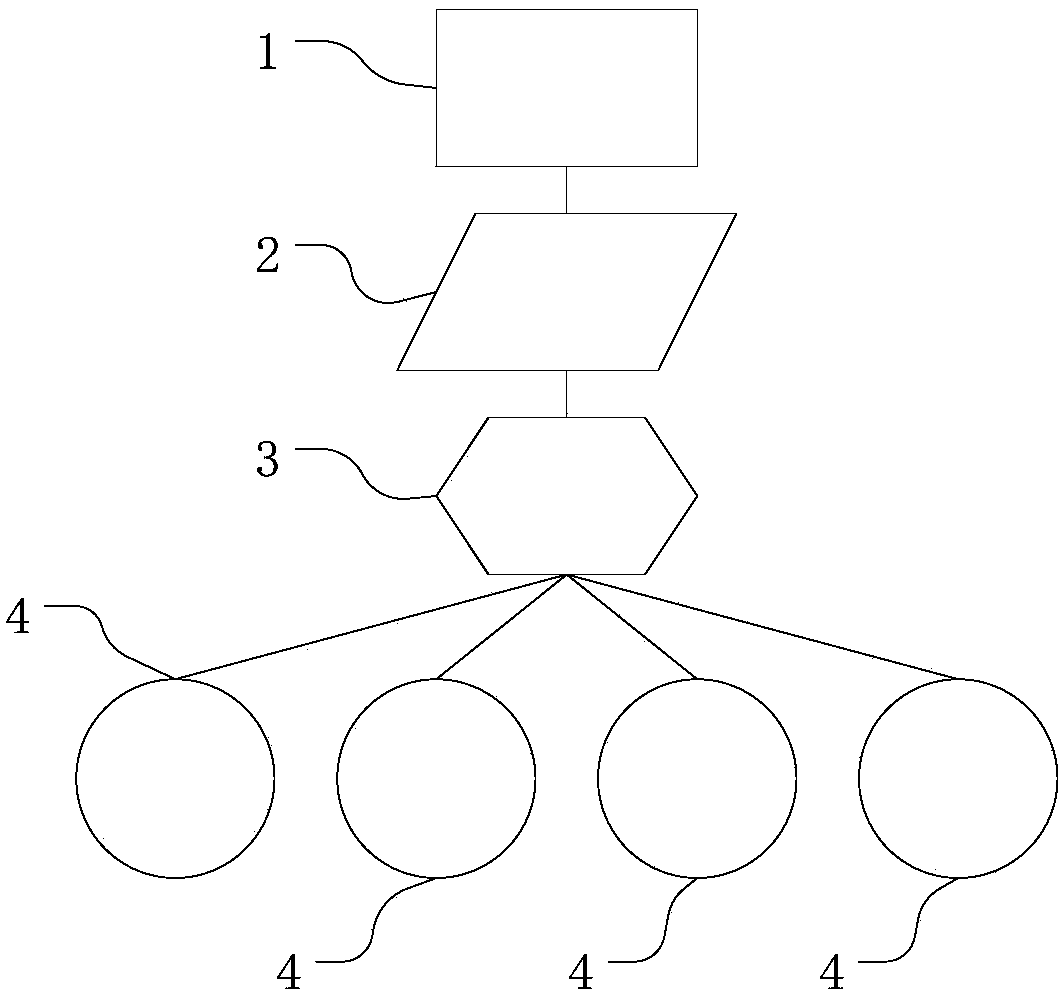

The invention discloses a short-circuit current analysis system, comprising: a GIS interface, a database, a short-circuit analysis module, and several clients. The short-circuit analysis module includes a processor, a topology and an electrical analysis module. The client is connected to the short-circuit analysis module, which is connected to the Database, database connection GIS interface. The invention also discloses an analysis method of the short-circuit current analysis system. It can realize the timely detection and evaluation of the short-circuit fault in the circuit, guarantee the safety of the circuit operation, and provide a reliable evaluation method for the troubleshooting of the circuit fault. It is of great significance to the normal operation of the circuit.

Owner:GUANGXI POWER GRID CO LTD NANNING POWER SUPPLY BUREAU

Compact opto-electric probe

PendingCN113125935AElectrical measurement instrument detailsContactless circuit testingOptical testPhotovoltaic detectors

Embodiments of the present disclosure relate to a compact opto-electric probe. Described are various configurations for performing efficient optical and electrical testing of an opto-electrical device using a compact opto-electrical probe. The compact opto-electrical probe can include electrical contacts arranged for a given electrical contact layout of the opto-electrical device, and optical interface with a window in a probe core that transmits light from the opto-electrical device. An adjustable optical coupler of the probe can be mechanically positioned to receive light from the device's emitter to perform simultaneous optical and electrical analysis of the device.

Owner:OPENLIGHT PHOTONICS INC

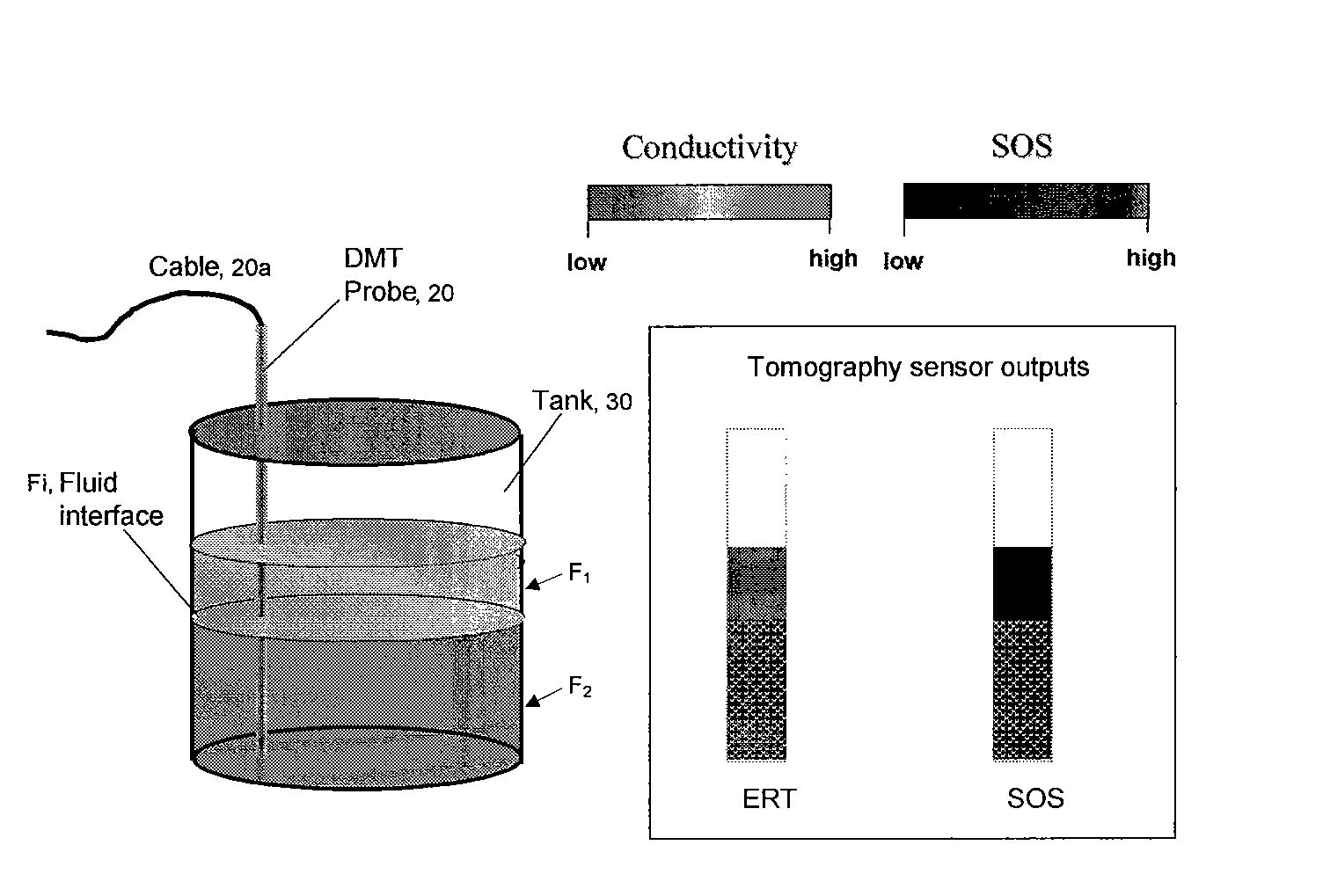

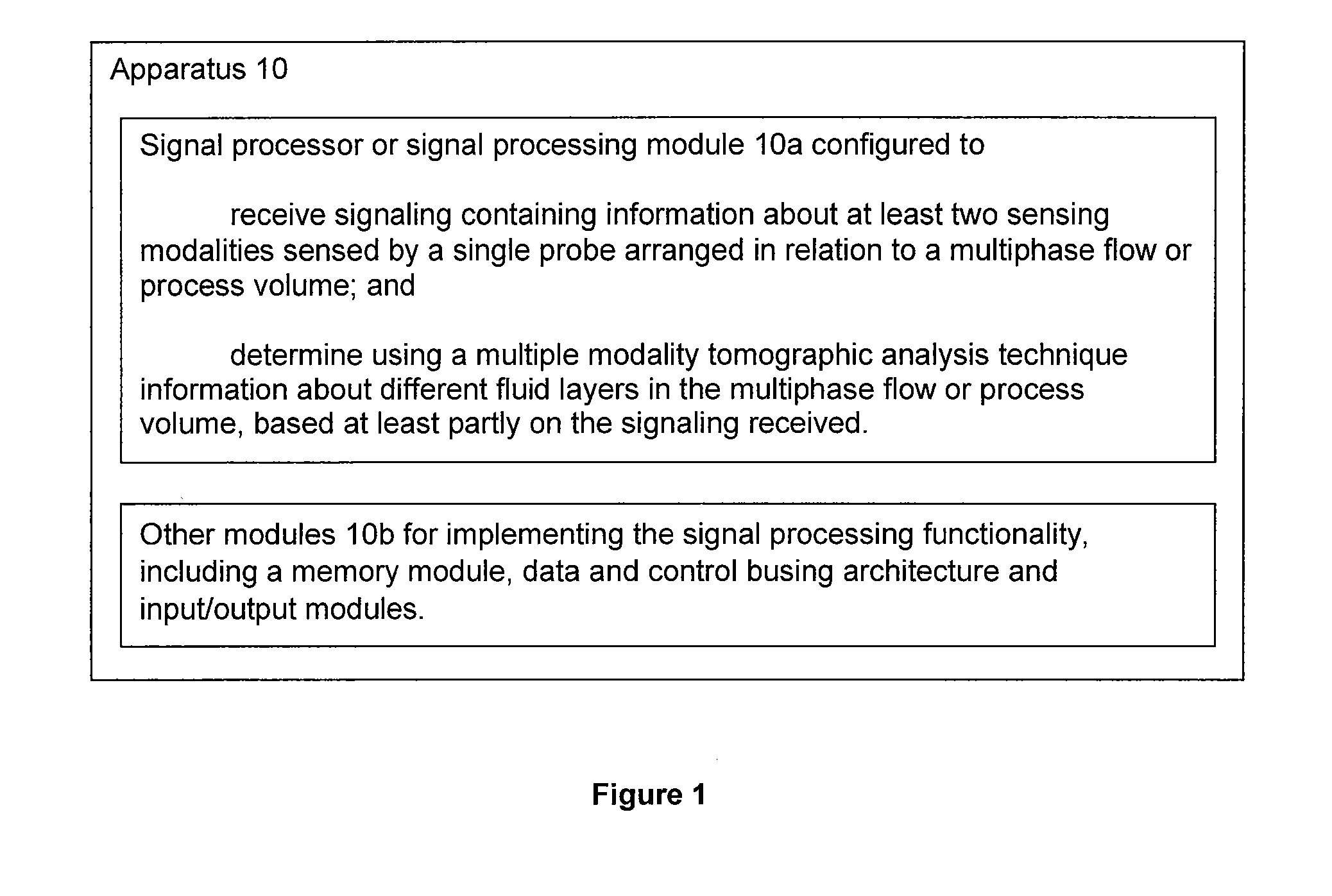

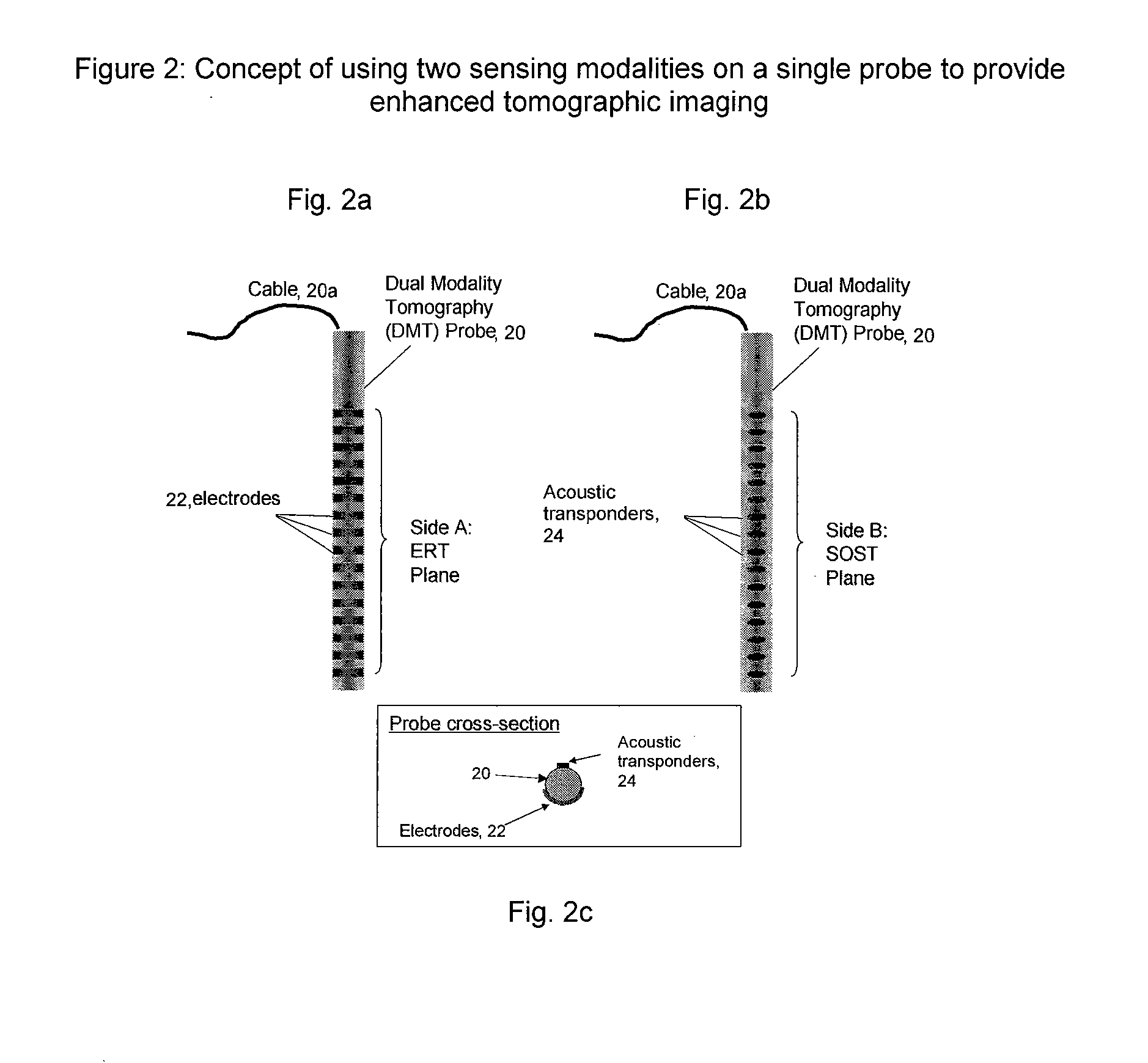

Dual acoustic and electrical analysis technique for the tomographic determination of multiphase flows in pipes and/or liquid/froth interfaces in process tanks

ActiveUS20150020579A1Analysing solids using sonic/ultrasonic/infrasonic wavesMaterial testing goodsFluid layerEngineering

Apparatus is provided featuring a signal processor or processing module configured to: receive signaling containing information about at least two sensing modalities sensed by a single probe arranged in relation to a multiphase flow or process volume; and determine using a multiple modality tomographic analysis technique information about different fluid layers in the multiphase flow or process volume, based at least partly on the signaling received. The signal processor or processing module may be configured to provide corresponding signaling containing corresponding information about different fluid layers in the multiphase flow or process volume.

Owner:CIDRA CORP SERVICES

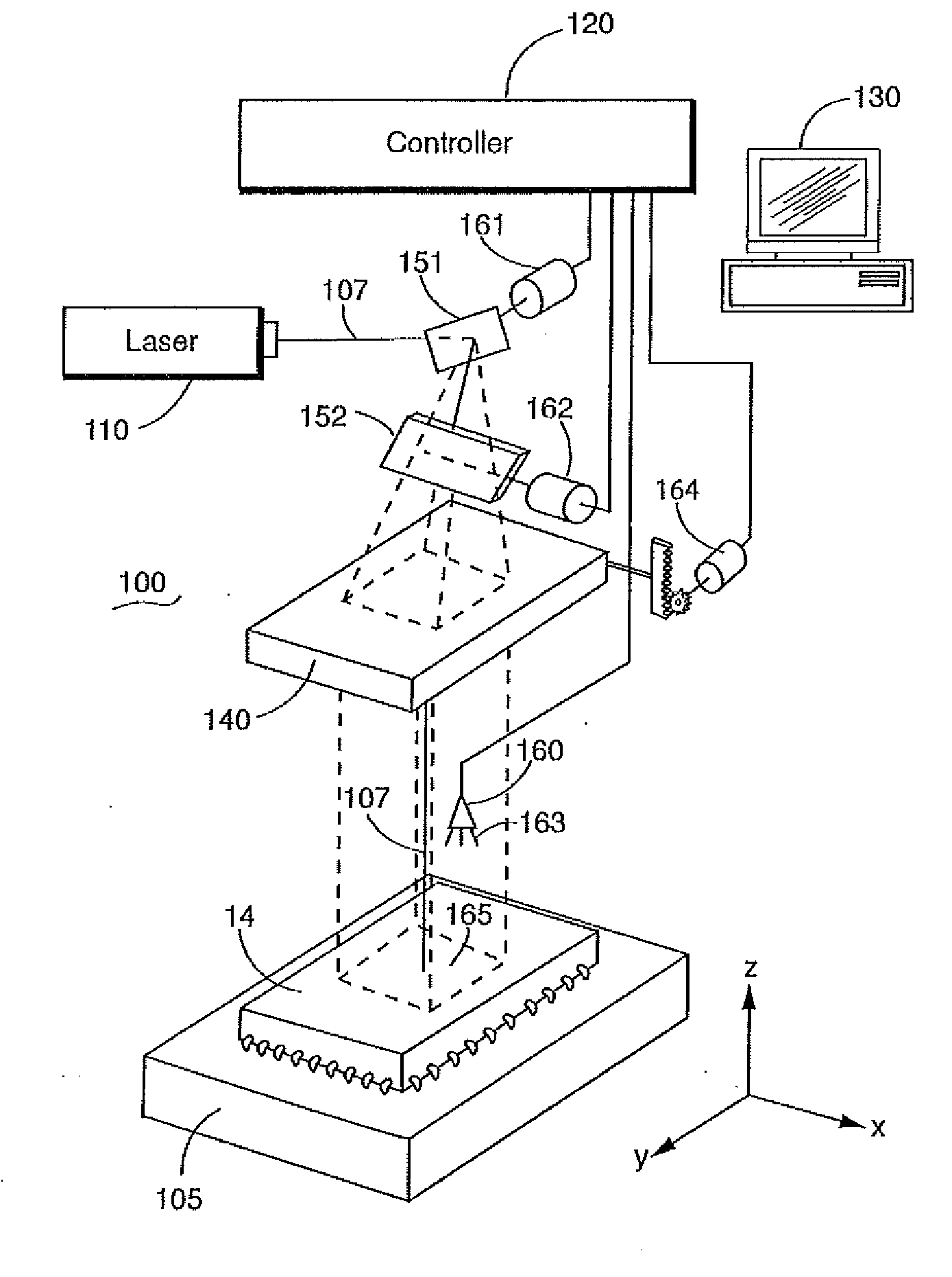

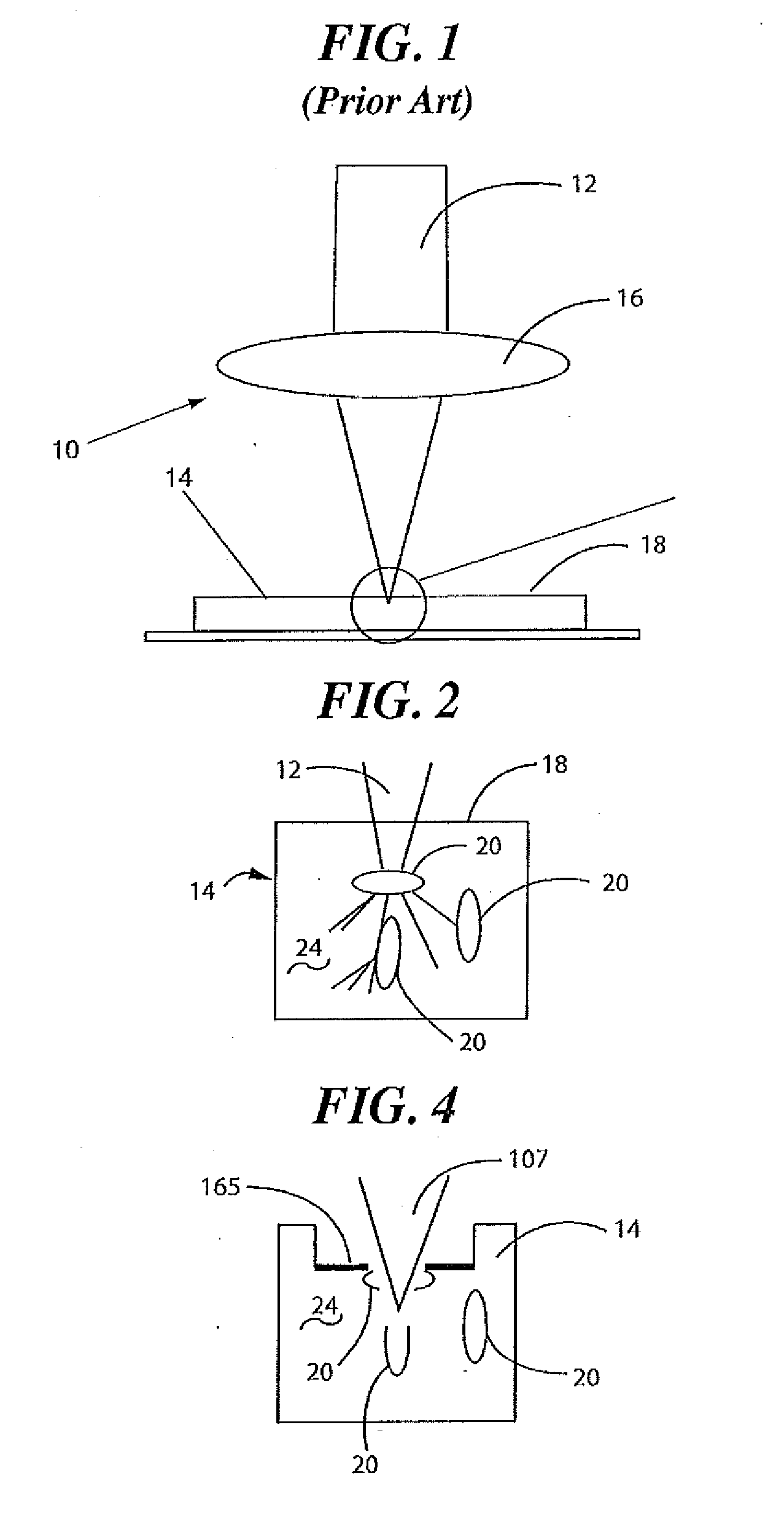

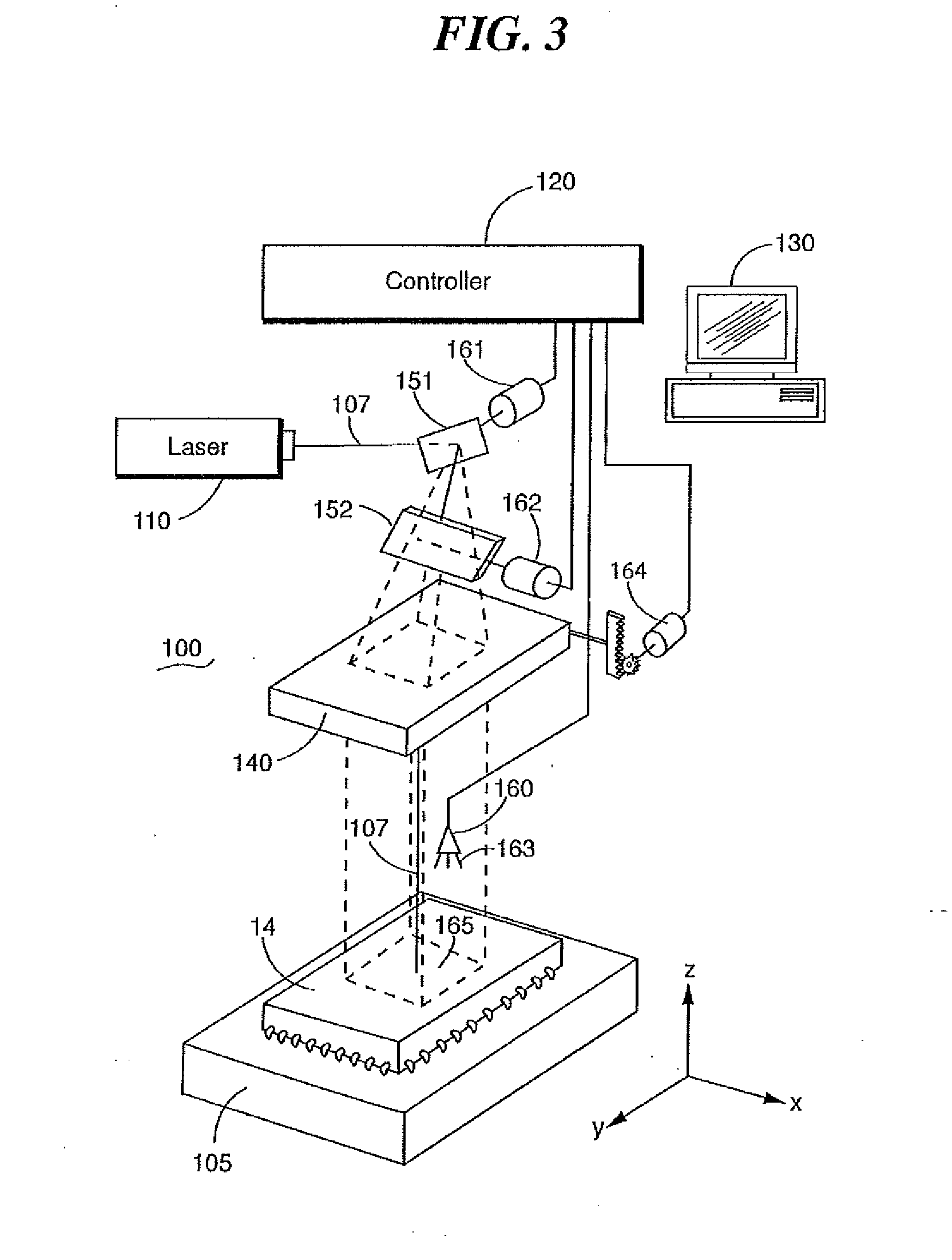

Method and system for exposing delicate structures of a device encapsulated in a mold compound

InactiveUS20110089152A1Solid-state devicesSemiconductor/solid-state device manufacturingCompound aCritical structure

A system utilizes a laser to remove the mold compound of an IC without damaging the internal die, wire leads, solder connections and any other critical structures encapsulated within the mold compound, thereby leaving them available for the provisional and electrical analysis. A laser beam is focused through appropriate optics onto a plane corresponding to the surface of an IC. A layer of material which is opaque at the wave length of the laser beam is applied at the surface of the IC chip to be ablated prior to each pass of the laser. A spray nozzle may be provided to move in synchronous motion ahead of the laser being to apply coat of the opaque material.

Owner:CONTROL LASER

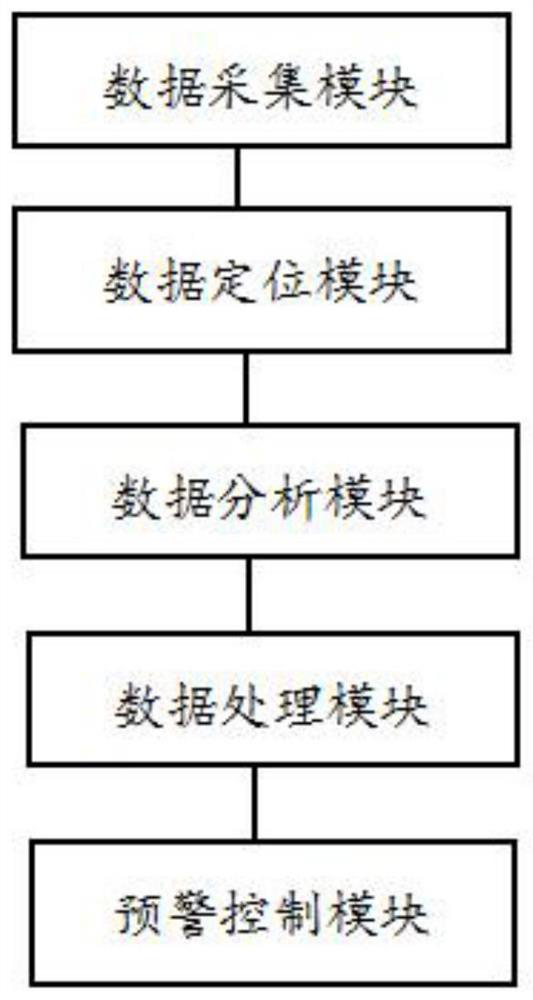

Intelligent electrical control system for a building

ActiveCN112947158AReach warningAchieve the purpose of regulationProgramme controlComputer controlControl systemData information

The invention discloses an intelligent electrical control system for a building. A building collection unit is used for collecting the data information of the building, and an electrical collection unit is used for collecting the electrical information of the building. A data positioning module is used for positioning and processing coordinates of floors and building households on the building, and coordinate processing information is obtained; a data analysis module is used for receiving the data information and the electrical information, analyzing the data information to obtain data analysis information, analyzing the electrical information to obtain electrical analysis information, and combining the data analysis information and the electrical analysis information to obtain a data analysis set; a data processing module is used for receiving the data analysis set and processing the data analysis set to obtain a data processing set, and an early warning control module is used for early warning, regulating and controlling the electrical state of the building according to the data processing set; the system is used for solving the problem that the electrical operation state of each building user in a building cannot be monitored, and the problem that early warning and regulation are carried out on the building user in an abnormal state.

Owner:ANHUI UNIVERSITY OF ARCHITECTURE

Through process flow intra-chip and inter-chip electrical analysis and process control using in-line nanoprobing

ActiveUS10539589B2Quality improvementReduce riskSemiconductor/solid-state device testing/measurementElectric discharge tubesWaferingNanoprobe

System for performing in-line nanoprobing on semiconductor wafer. A wafer support or vertical wafer positioner is attached to a wafer stage. An SEM column, an optical microscope and a plurality of nanoprobe positioners are all attached to the ceiling. The nanoprobe positioners have one nanoprobe configured for physically contacting selected points on the wafer. A force (or touch) sensor measures contact force applied by the probe to the wafer (or the moment) when the probe physically contacts the wafer. A plurality of drift sensors are provided for calculating probe vs. wafer alignment drift in real-time during measurements.

Owner:DCG SYST

Methods and arrangement for plasma dechuck optimization based on coupling of plasma signaling to substrate position and potential

ActiveUS8797705B2Semiconductor/solid-state device manufacturingEmergency protective arrangement detailsCouplingEngineering

A method for optimizing a dechuck sequence, which includes removing a substrate from a lower electrode. The method includes performing an initial analysis to determine if a first set of electrical characteristic data of a plasma formed during the dechuck sequence traverses a threshold values. If so, turning off the inert gas. The method also includes raising the lifter pins slightly from the lower electrode to move the substrate in an upward direction. The method further includes performing a mechanical and electrical analysis, which includes comparing a first set of mechanical data, which includes an amount of force exerted by the lifter pins, against a threshold value. The mechanical and electrical analysis also includes comparing a second set of electrical characteristic data against a threshold value. If both traverse the respective threshold value, removes the substrate from the lower electrode since a substrate-released event has occurred.

Owner:LAM RES CORP