Micron level chip packing structure

A chip packaging structure, micron-level technology, applied in electrical components, electrical solid-state devices, circuits, etc., can solve the problems of affecting the performance of the chip, reducing the bonding force of the ball joint, and reducing the stability.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

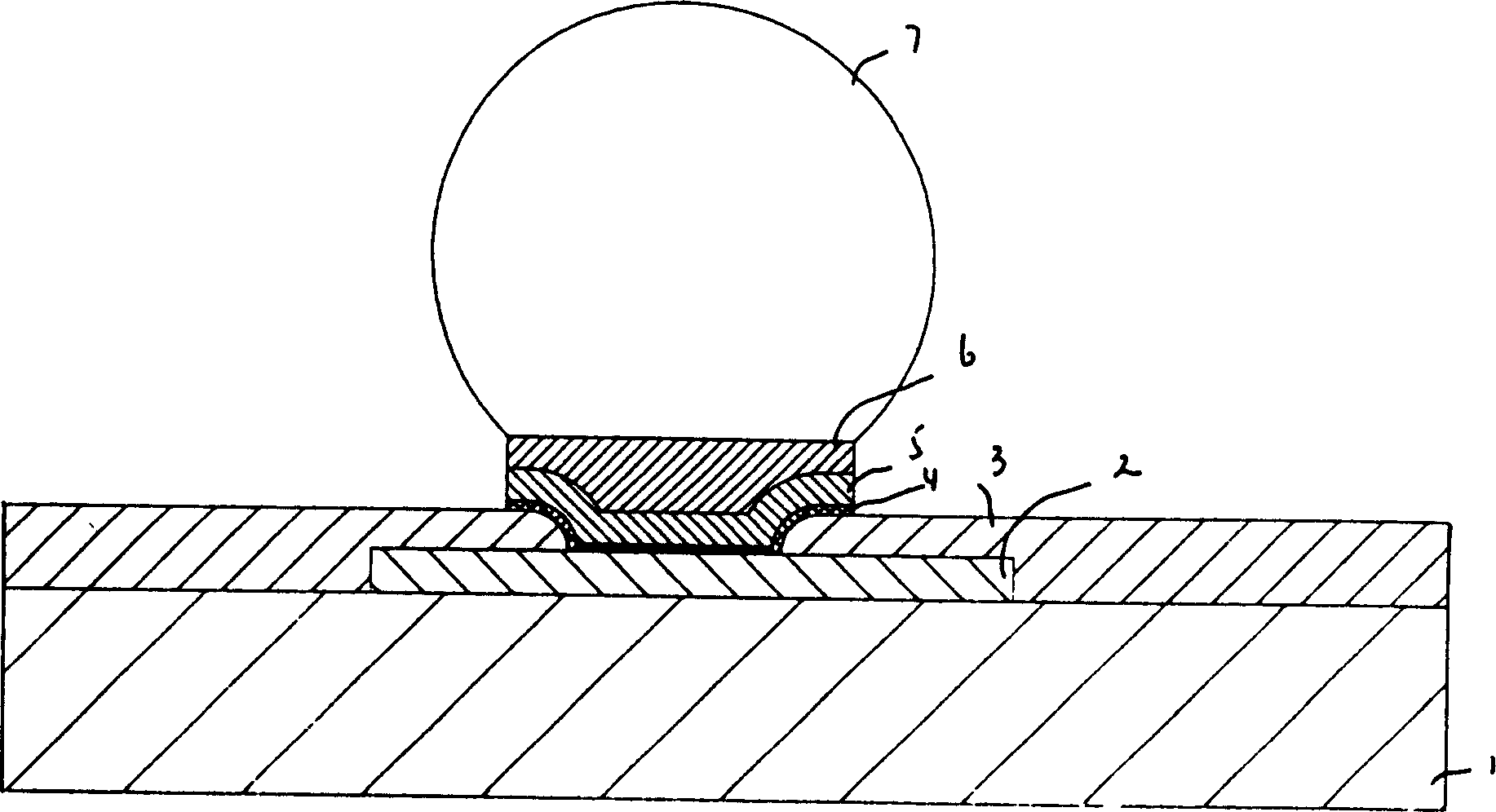

[0014] see figure 1 , the present invention is a micron-scale chip packaging structure, which is provided with a welding pad 2 on one surface of the chip body 1, the outer periphery of the welding pad 2 and the surface of the chip body 1 outside the outer periphery are provided with a protective layer 3, the surface of the welding pad 2 and A titanium layer 4, a copper layer 5 and a copper pillar 6 are sequentially superimposed on the protective layer 3 on the outer periphery, and solder balls 7 are planted on the top of the copper pillar 6, and all the solder balls are placed on the top of the copper pillar.

[0015] The thickness of the copper pillar 6 should be determined according to the reliability requirements of the chip, and is generally controlled within 5 μm˜100 μm.

Embodiment 2

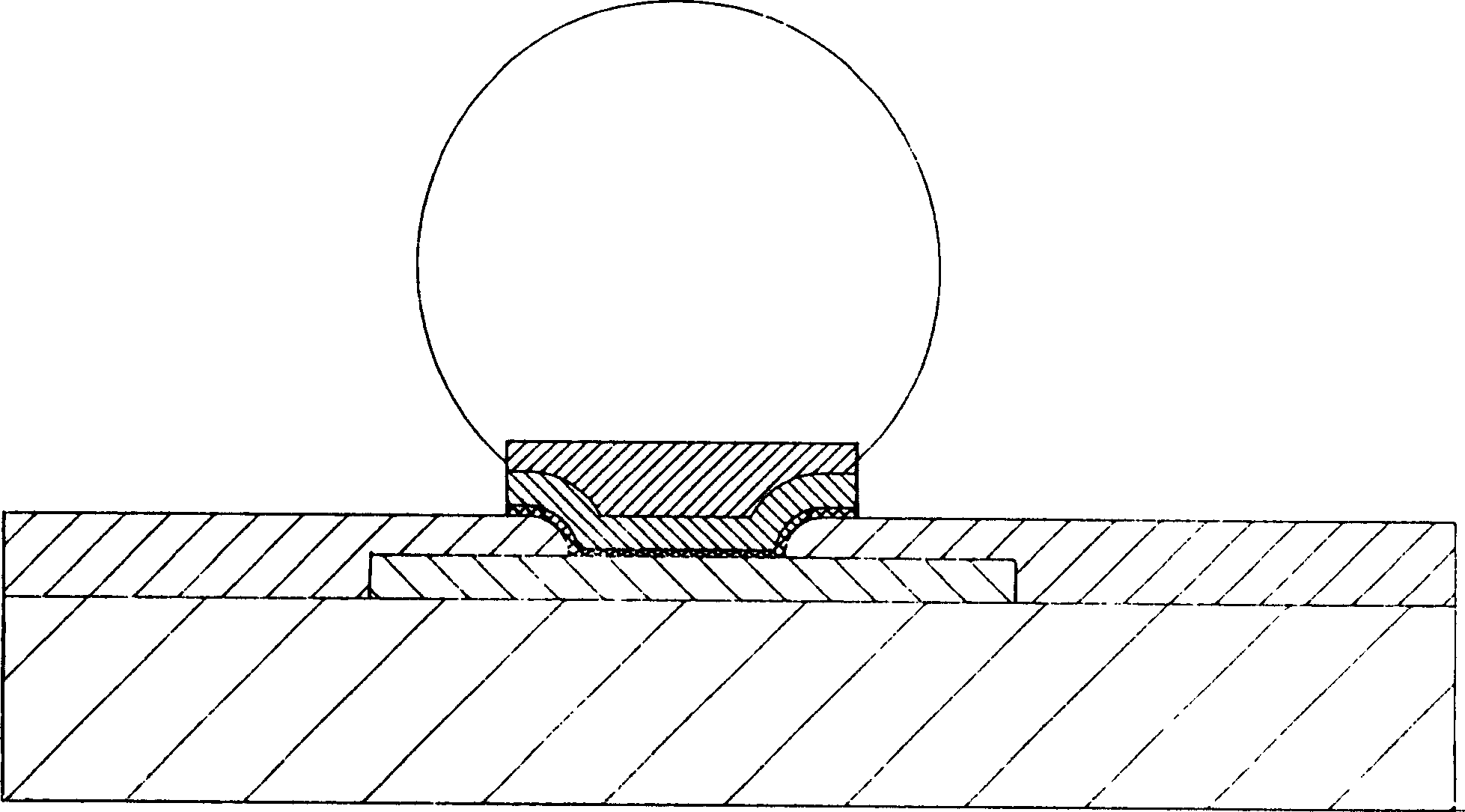

[0017] see figure 2 , the difference between this embodiment and the first embodiment is only that the solder balls 7 partially cover the copper pillars 6 .

Embodiment 3

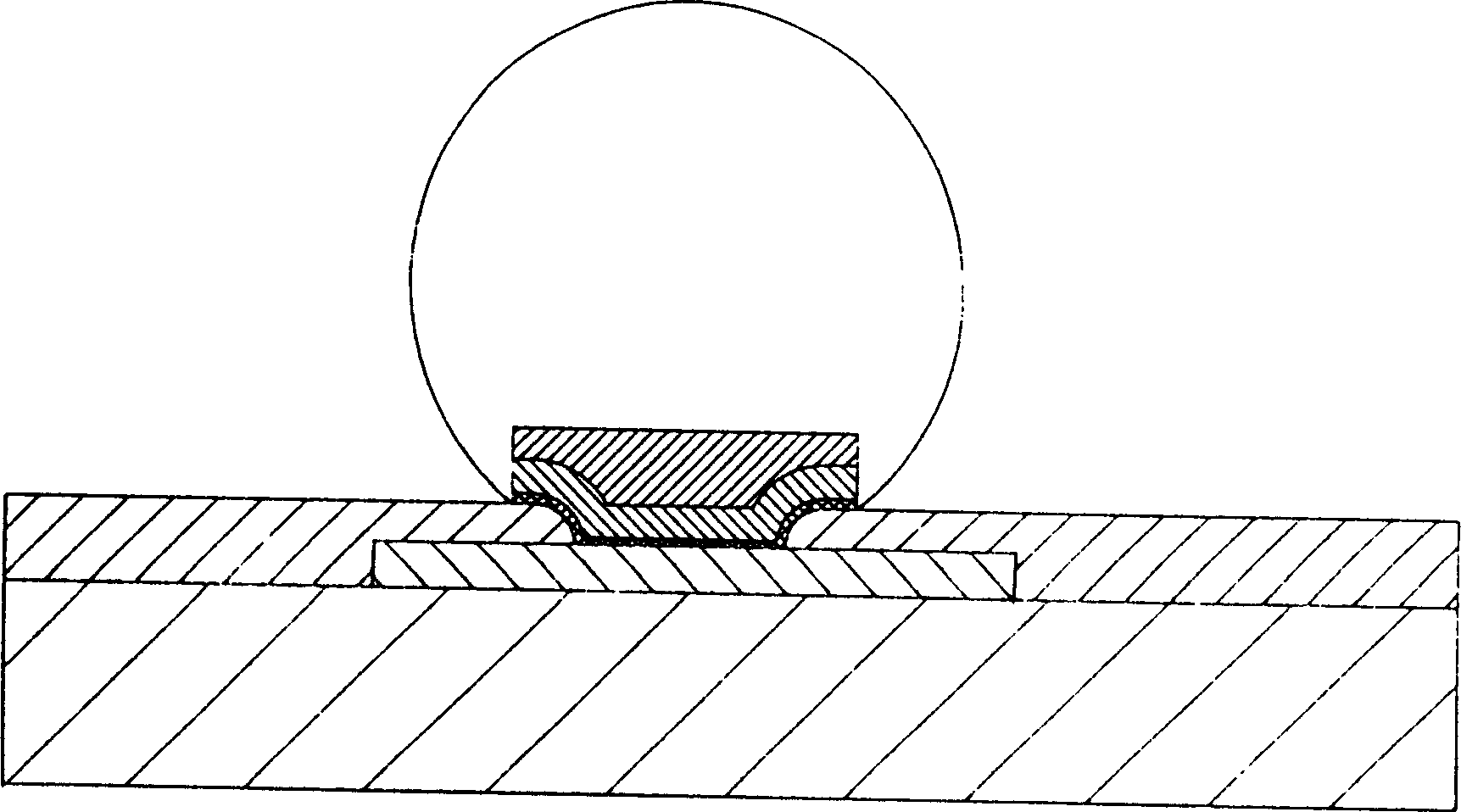

[0019] see image 3 The only difference between this embodiment and the first embodiment is that the solder balls 7 completely cover the copper pillars 6 , the copper layer 5 and the titanium layer 4 .

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More