Method and apparatus for measuring stress in semiconductor wafers

A technology of wafer and overall measurement, applied in the direction of measuring device, measuring force, adopting optical device, etc., can solve the problems of reduced reliability and reduced output

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0139] Description of preferred embodiments

[0140] As an introduction to the present invention, the measurement method of PCT Patent Application No. WO0012958 is discussed in detail.

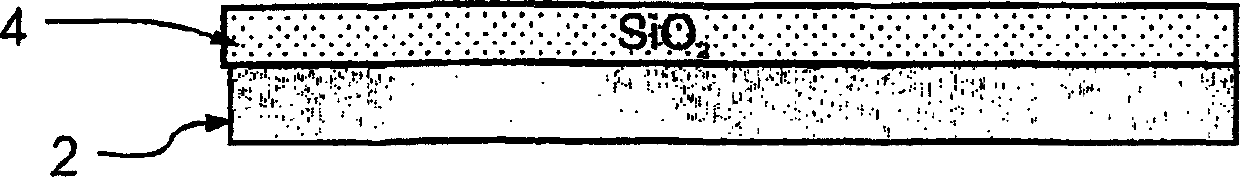

[0141] Reference is now made to FIG. 1A which shows a schematic cross-sectional view of a silicon wafer at an intermediate stage in the production process. Silicon wafer 2 has SiO attached to it 2 Layer 4. In Figure 1A the SiO 2 Layer 4 is homogeneous and only a single measurement is required to determine the layer thickness.

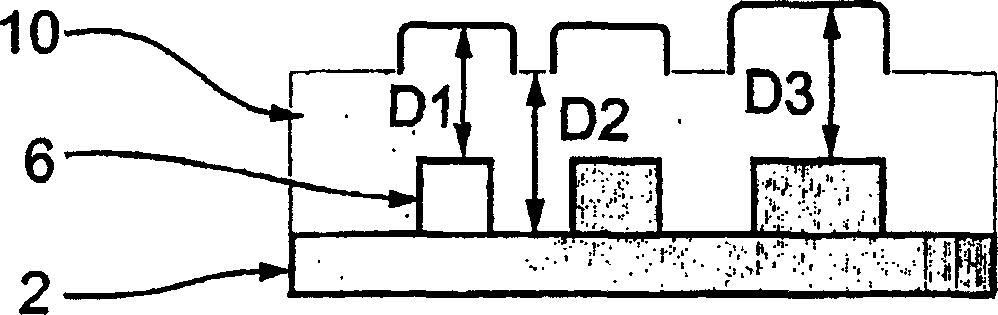

[0142] Reference is now made to FIG. 1B which shows a schematic cross-sectional view of another silicon wafer at another intermediate stage in the production process. In Figure 1B wafer 2 comprises a series of metal structures 6, and a continuous SiO 2 Layer 10. As will be explained in more detail below, the TMS measuring system is particularly suitable for measuring the thickness of transparent films. In this case, SiO 2 The layer 10 has thickness differences a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More