Vertical-type power metal oxide semiconductor device with excess current protective function

An oxide semiconductor, vertical technology, used in semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., and can solve problems such as thermal damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

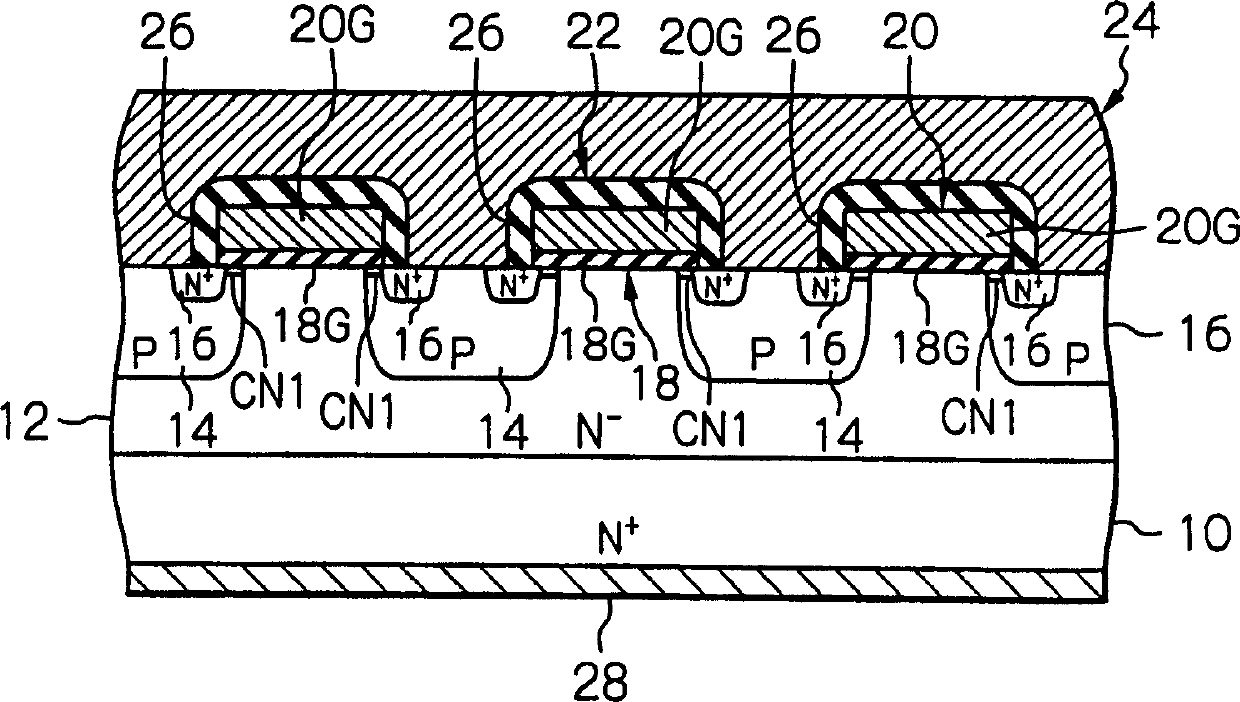

[0088] Referring to FIGS. 11A to 11J , a production method for producing the first embodiment of the vertical type power MOS device according to the present invention will now be explained.

[0089] First, as shown in Figure 11A, N + type semiconductor substrate 112, and N - Type epitaxial layer 114 is formed as N + N on the type semiconductor substrate 112 - type drift layer. For example, from such as arsenic (As + ) and other N-type impurities such as N + type monocrystalline silicon wafer obtained N + type semiconductor substrate 122, and a plurality of chip areas in which vertical type power MOS devices will be fabricated are limited to N by scribing + type semiconductor substrate 122. Moreover, N - Type epitaxial layer or drift layer 114 contains N-type impurities, such as arsenic (As + )Wait.

[0090] After completing the N - After the formation of the type drift layer 114, as shown in FIG. 11B, by using photolithography process and wet or dry etching process ...

no. 2 example

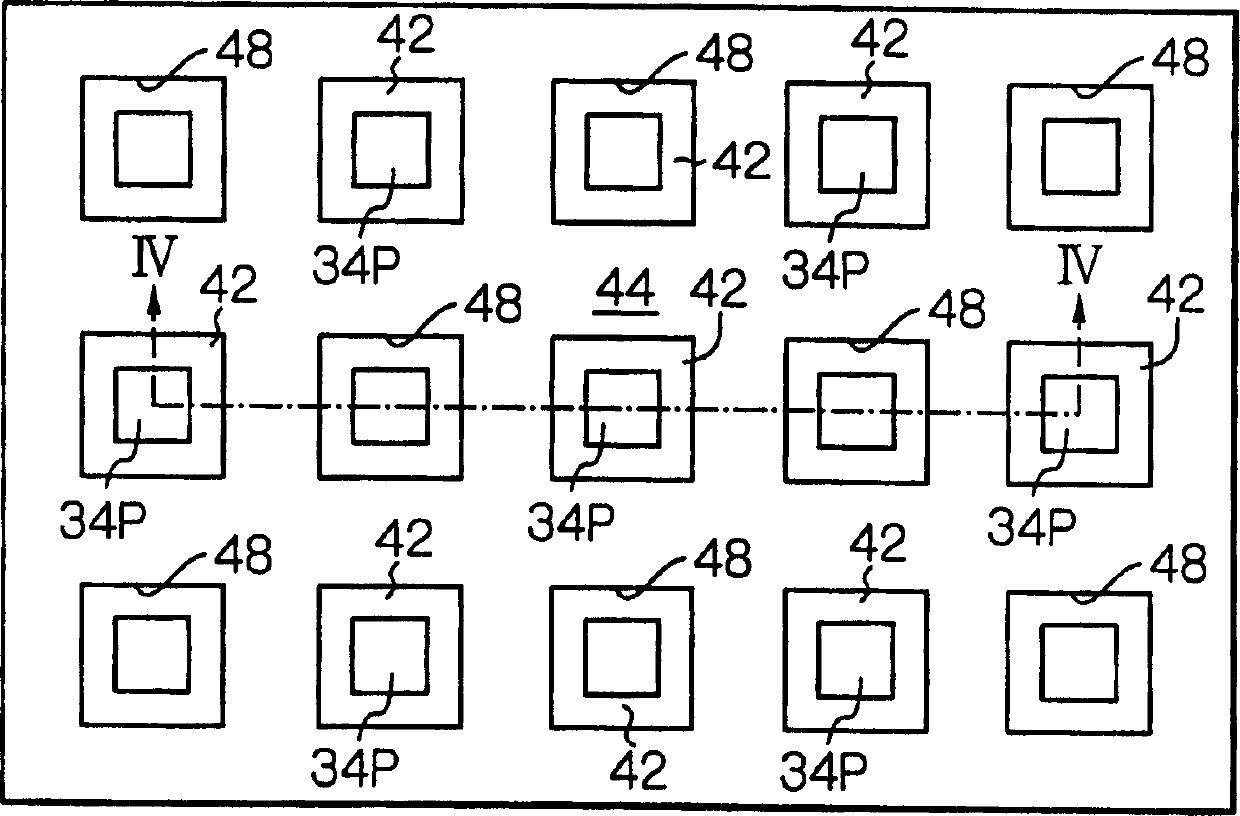

[0119] Referring to FIGS. 18A to 18D , the production method of the second embodiment for producing the vertical type power MOS device according to the present invention will be described below.

[0120] This production method includes first, second, third, fourth, fifth and sixth representative steps, which are substantially the same as those in the first production method mentioned as shown in FIGS. 11A to 11F . Note that in FIG. 18A , the same reference numerals as in FIG. 11F denote the same elements.

[0121] After completing the definition of the P-type low-density impurity implantation region 128L (FIG. 11F), a photoresist layer 146 is formed on the silicon dioxide layer 126, and the The photoresist layer 146 is patterned so that a portion of the P-type low-density impurity implantation region 128L is masked with the patterned photoresist layer 146, as shown in FIG. 18A. Note that in this figure, only two P-type low-density impurity implanted regions 128L are represent...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More