Semiconductor memory device and method for making same

A technology for storage devices and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, information storage, etc., and can solve the problems of reducing the number of storage units and increasing the loss of transistor area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0049] Hereinafter, embodiments of the present invention will be described in detail with reference to the drawings. In addition, throughout the drawings for describing the embodiments, the same members are given the same reference numerals in principle, and overlapping descriptions thereof will be omitted.

[0050] (Embodiment 1)

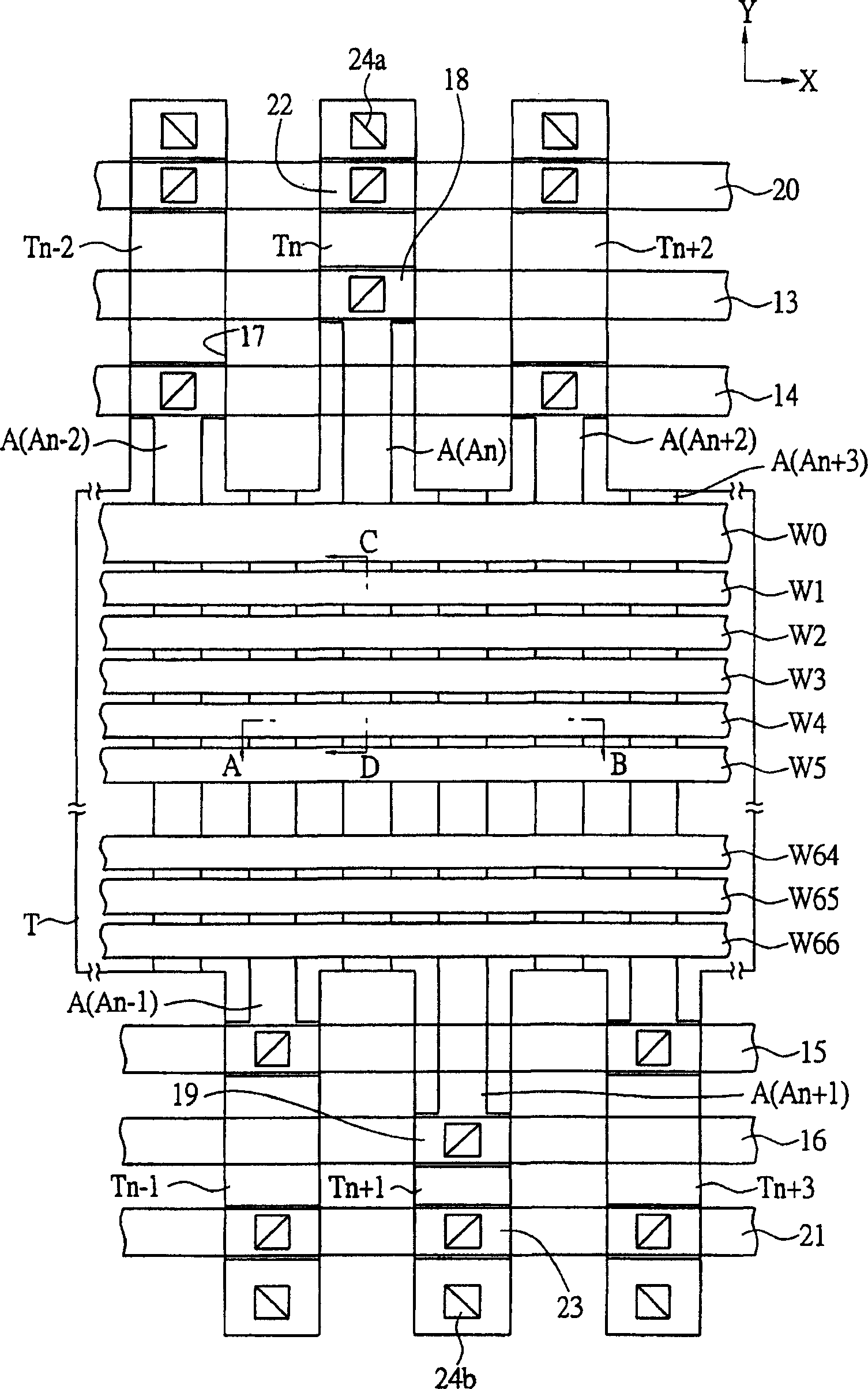

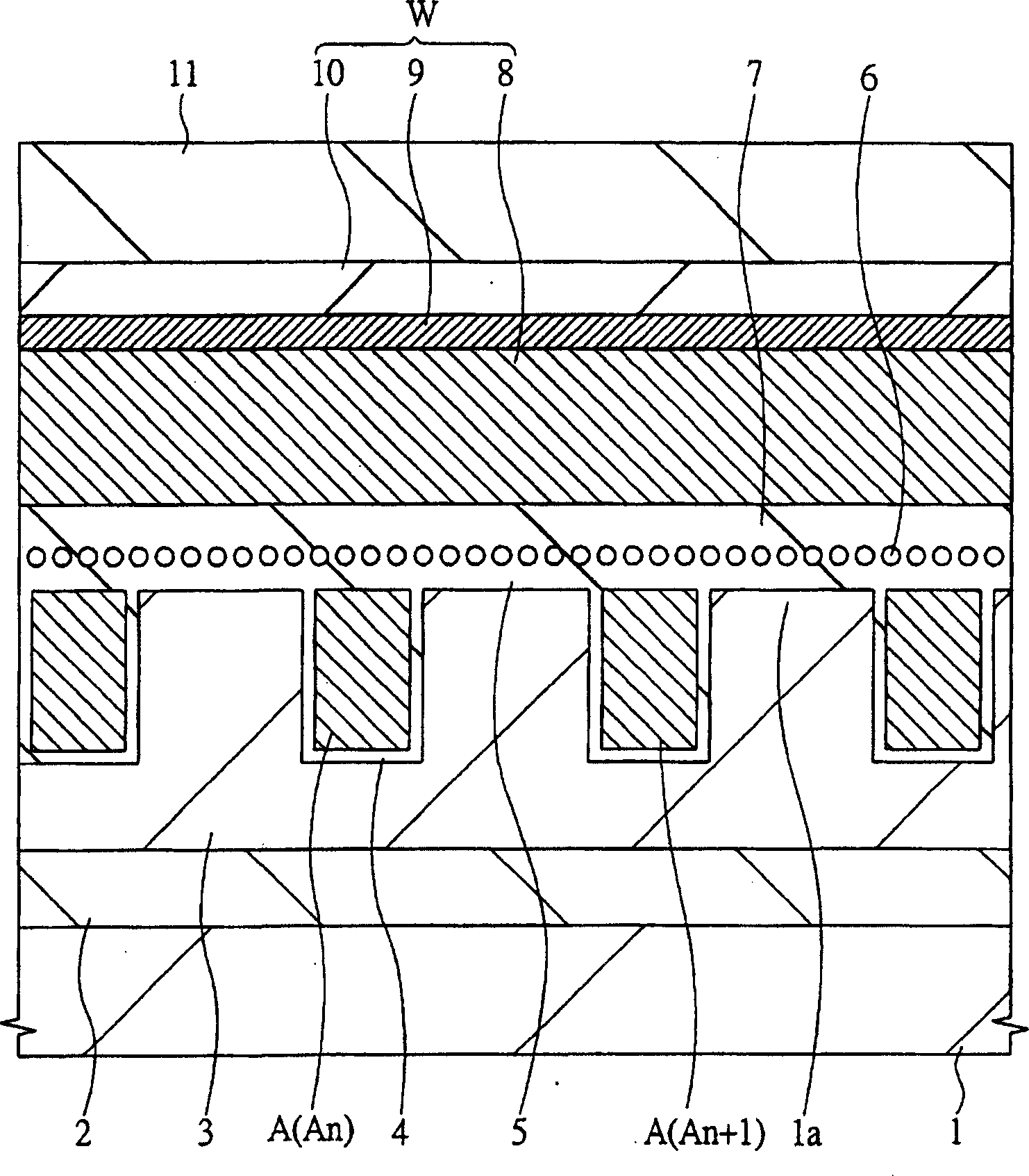

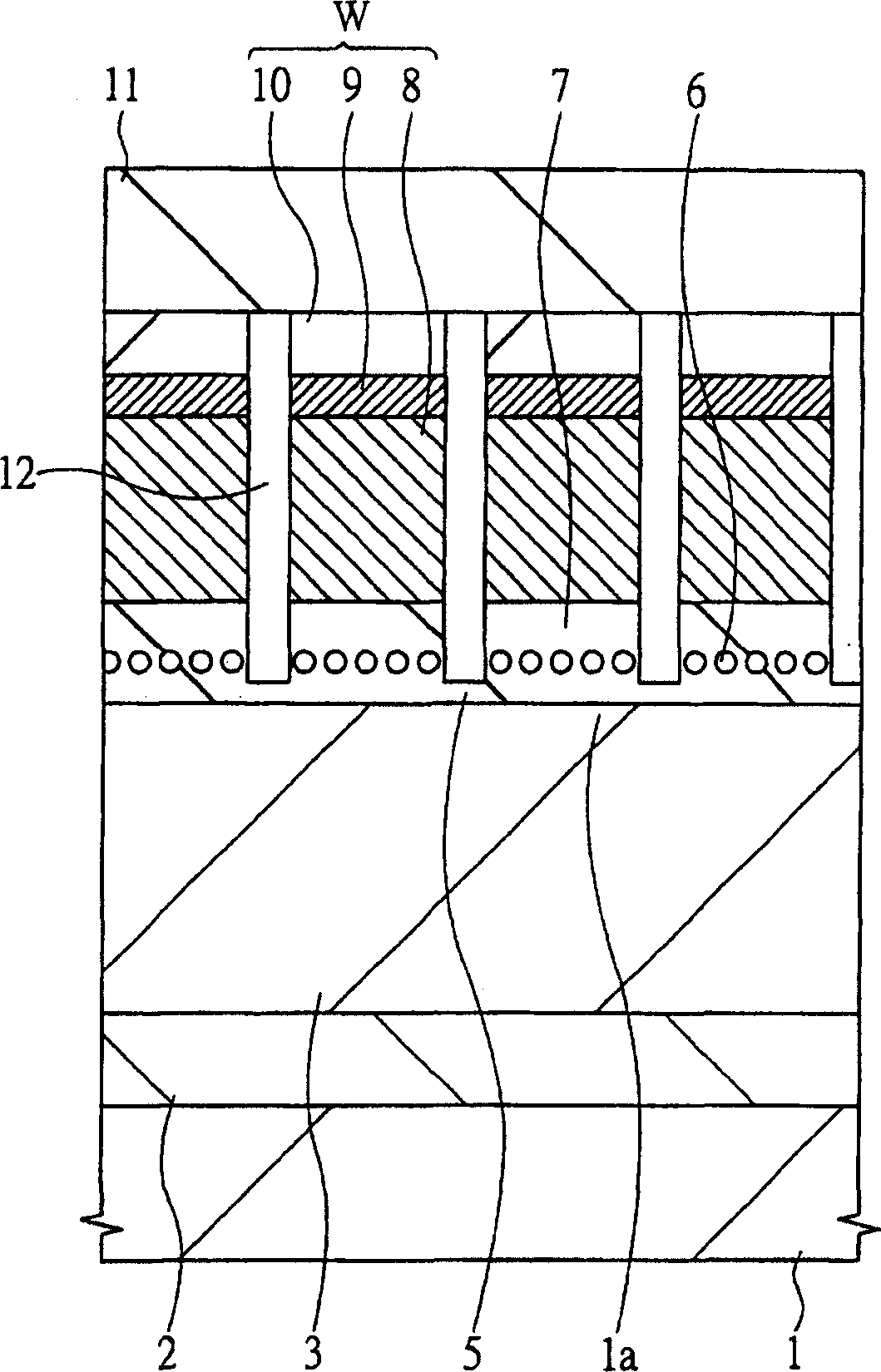

[0051] figure 1 is a schematic plan view showing a main part of a semiconductor substrate serving as a memory cell array of a flash memory according to this embodiment, figure 2 is along figure 1 The cross-sectional view of the semiconductor substrate of the A-B line (the cross-sectional direction of the auxiliary electrode), image 3 is along figure 1 The cross-sectional view of the semiconductor substrate of the C-D line (the cross-sectional direction of the word line), Figure 4 is an equivalent circuit diagram of the memory cell array. also, Figure 5 is the edge indicating the impurity concentration in each region of the memory cell ar...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More