Standard unit overall wiring method of multi-terminal network plug-in buffer optimizing delay

A technology of overall wiring and standard cells, applied in instruments, special data processing applications, electrical digital data processing, etc., can solve the problem that the algorithm cannot be directly applied to the multi-terminal wire network.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

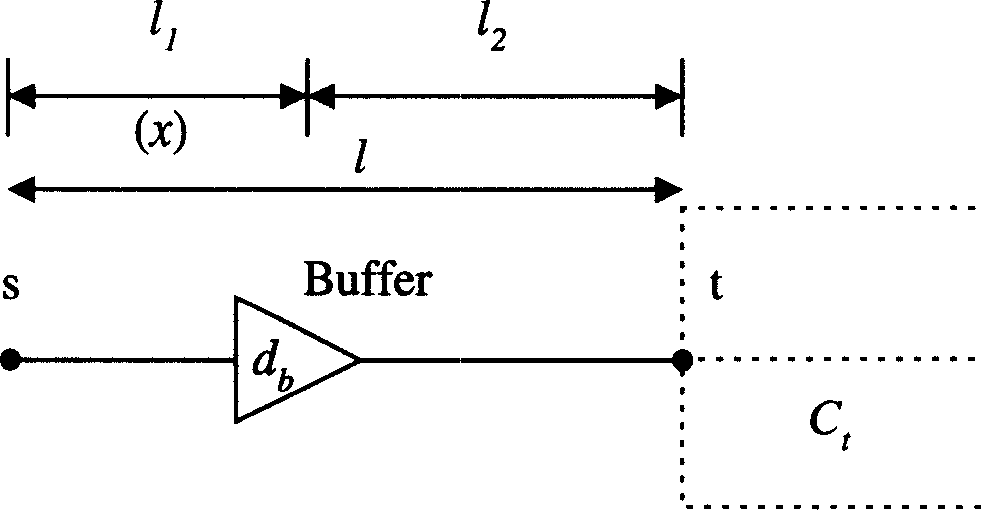

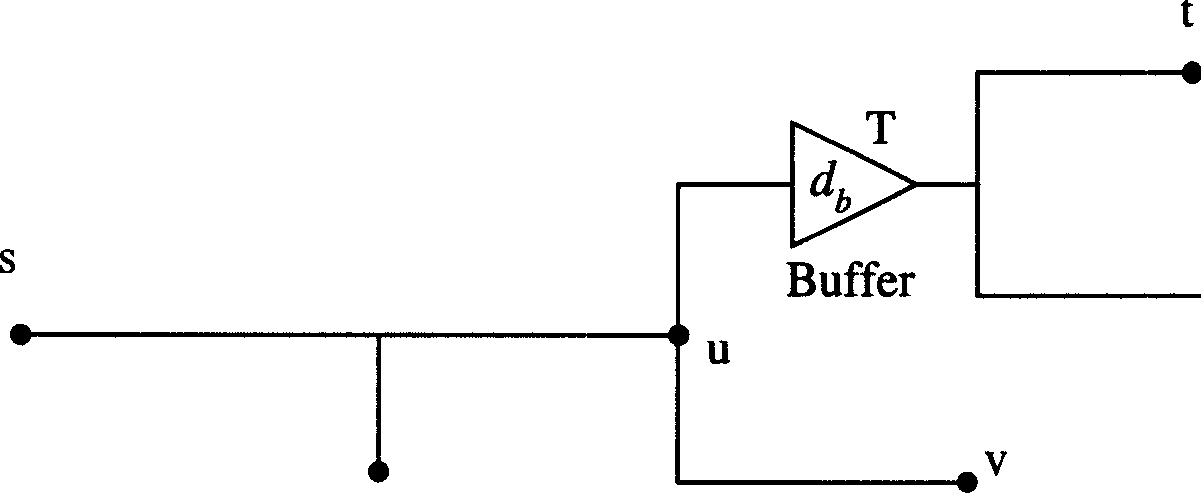

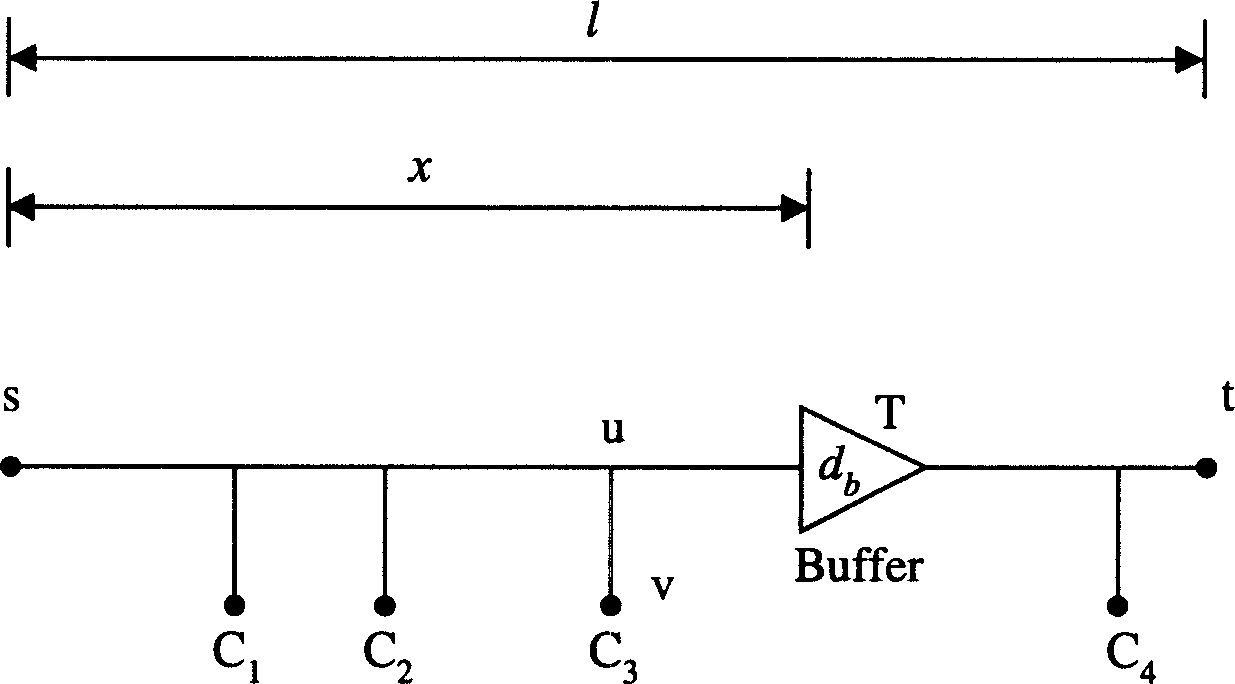

[0106] First, the optimal position for inserting a single buffer in the multi-terminal net to obtain the maximum delay improvement is deduced, and the formula for solving the optimal position is obtained. The derivation process includes two steps. The first step is to deduce the optimal position where the two-point line net is inserted into the buffer. In the second step, the optimal position for inserting the buffer of the multi-terminal net is derived.

[0107] The derivation process is based on the well-known "SAKURAI delay calculation formula", and a brief introduction to the "SAKURAI delay calculation formula" is given below.

[0108] The calculation formula of SAKURAI time delay regards the interconnection line as a transmission line with distributed resistance and capacitance, and the calculation formula is basically the same as the actual situation. The delay calculation formula is:

[0109] T DZ =βR s (c e +C z )+αr e c e +βr e C z

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More