Mutual compensating metals-oxides-semiconductor structure and its mfg. method

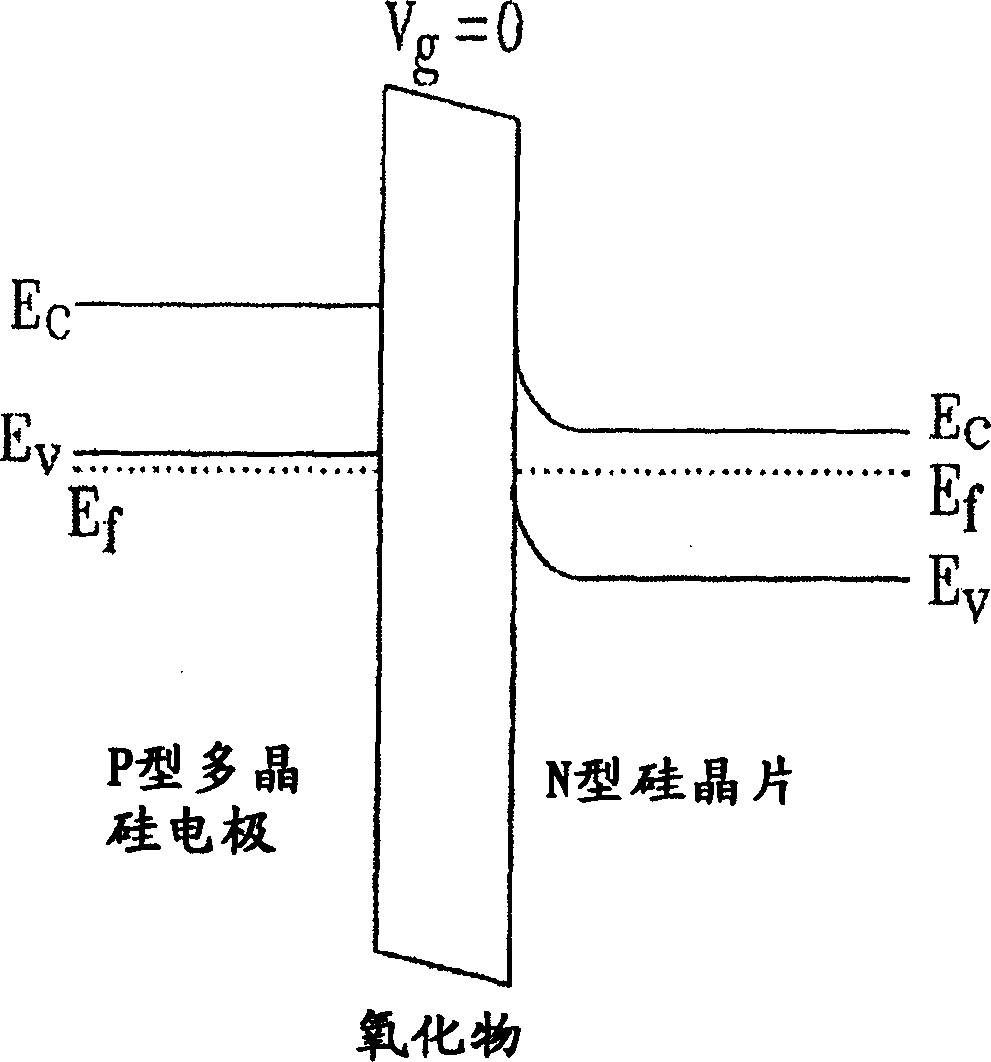

A complementary metal and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, transistors, etc., can solve problems such as threshold voltage and flat-band voltage change

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

example 1

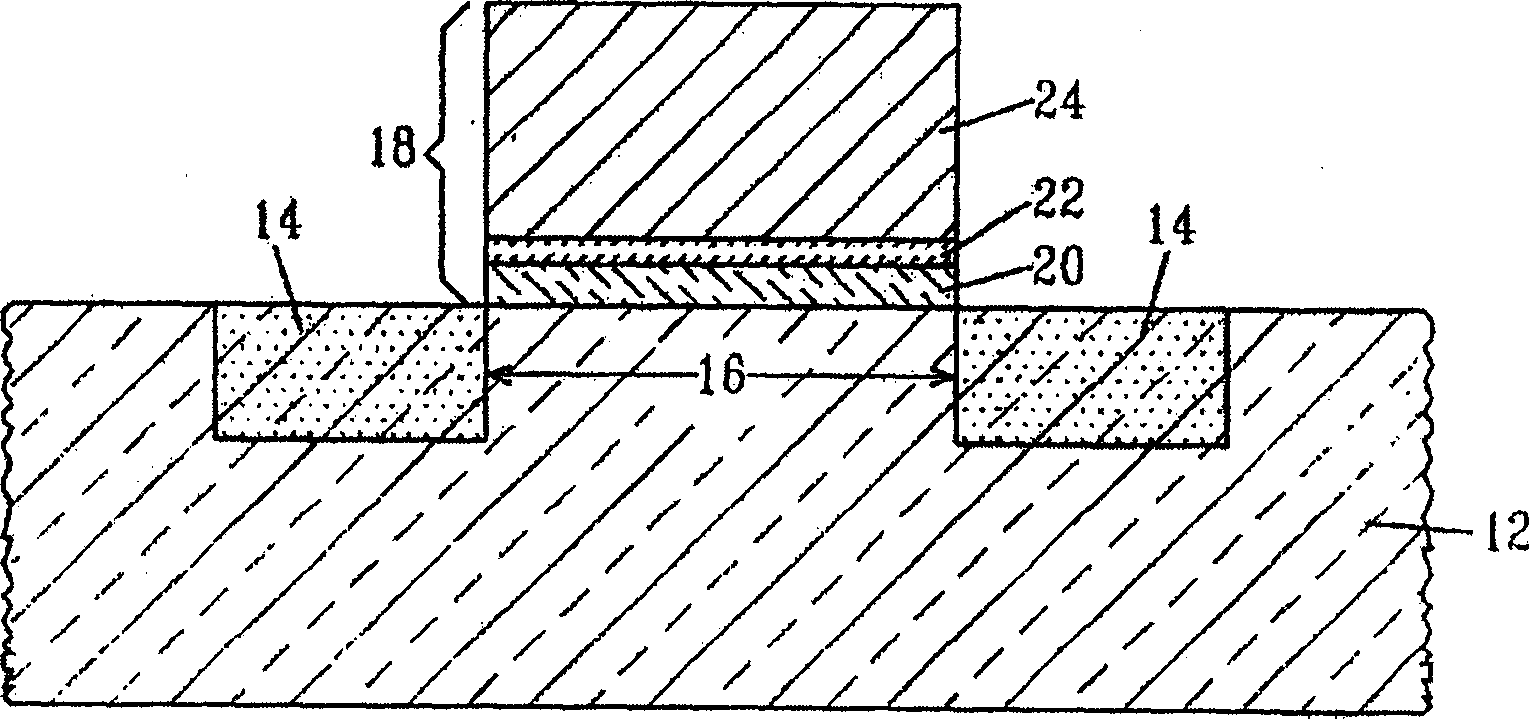

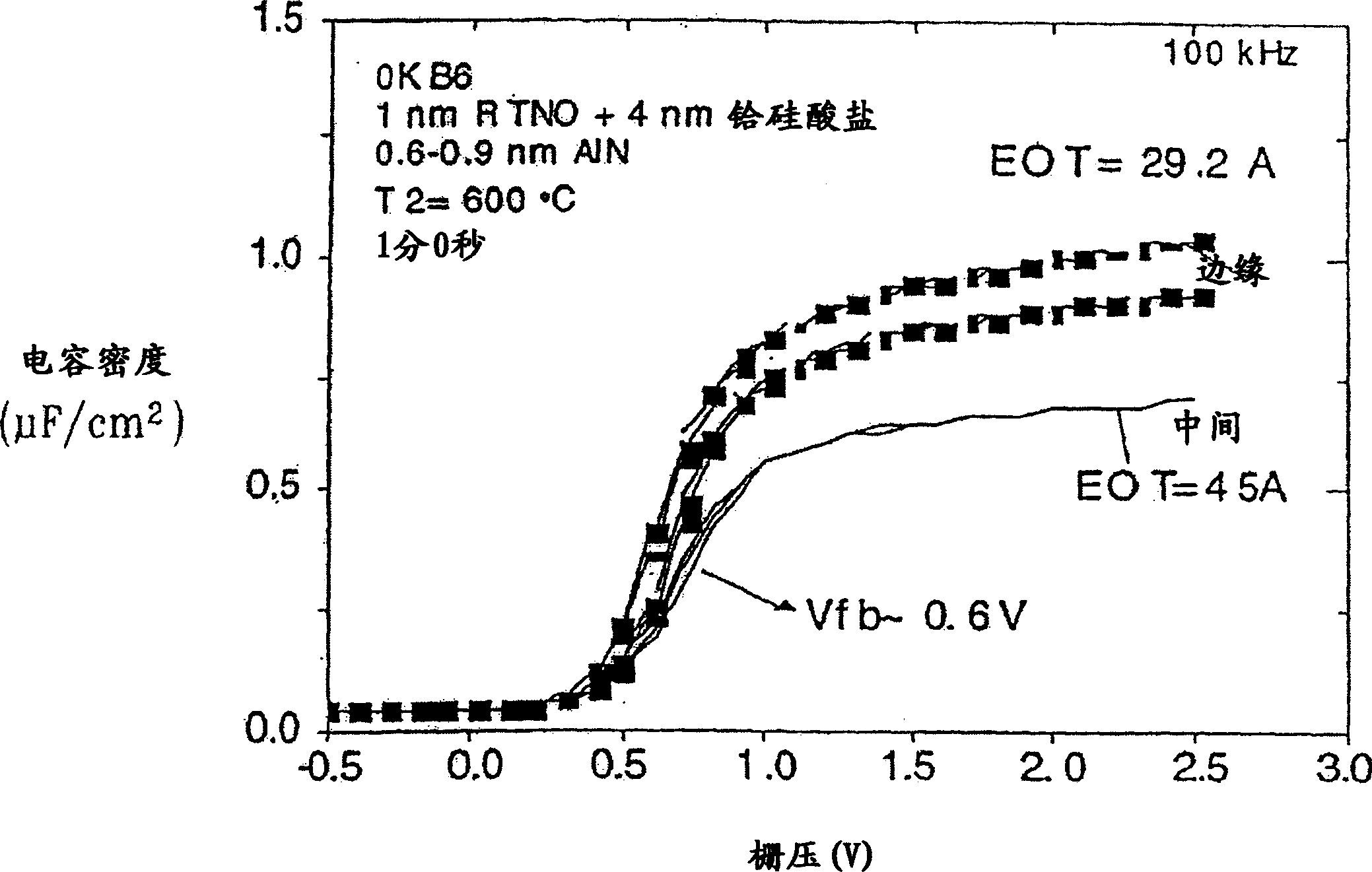

[0062] In this example, a Hf oxide or silicate layer is first grown on a silicon wafer prefabricated with a field oxide pattern. The Hf oxides and silicates are deposited by metalorganic chemical vapor deposition (MOCVD) and atomic layer chemical vapor deposition (ALCVD). The thickness of Hf oxide and silicate layer is about 2-4nm, and the composition of silicate is close to Hf x Si y o 4 , where y / (x+y) is about 0.2-0.3. These oxides are deposited on n-type silicon wafers covered with silicon oxide or silicon oxynitride with a thickness of 0.3-1.2 nm. The presence of this layer is completely optional.

[0063] After depositing Hf oxide and silicate, the wafer is loaded into an ultra-high vacuum deposition chamber to deposit aluminum nitride. Aluminum nitride was deposited by evaporating Al from a resistively heated standard Al jet furnace and using a nitrogen beam from a commercial radio frequency atomic nitrogen source. The temperature of the spray furnace during depos...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More