Method of enhancing clear field phase shift masks by adding parallel line to phase 0 region

A technology of area and phase, which is applied in the direction of circuit, electrical components, and patterned surface photolithography, can solve the problems of complex patterning of binary masks and limitations of manufacturing window technology, so as to reduce the influence of aberration and reduce the The effect of aberration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

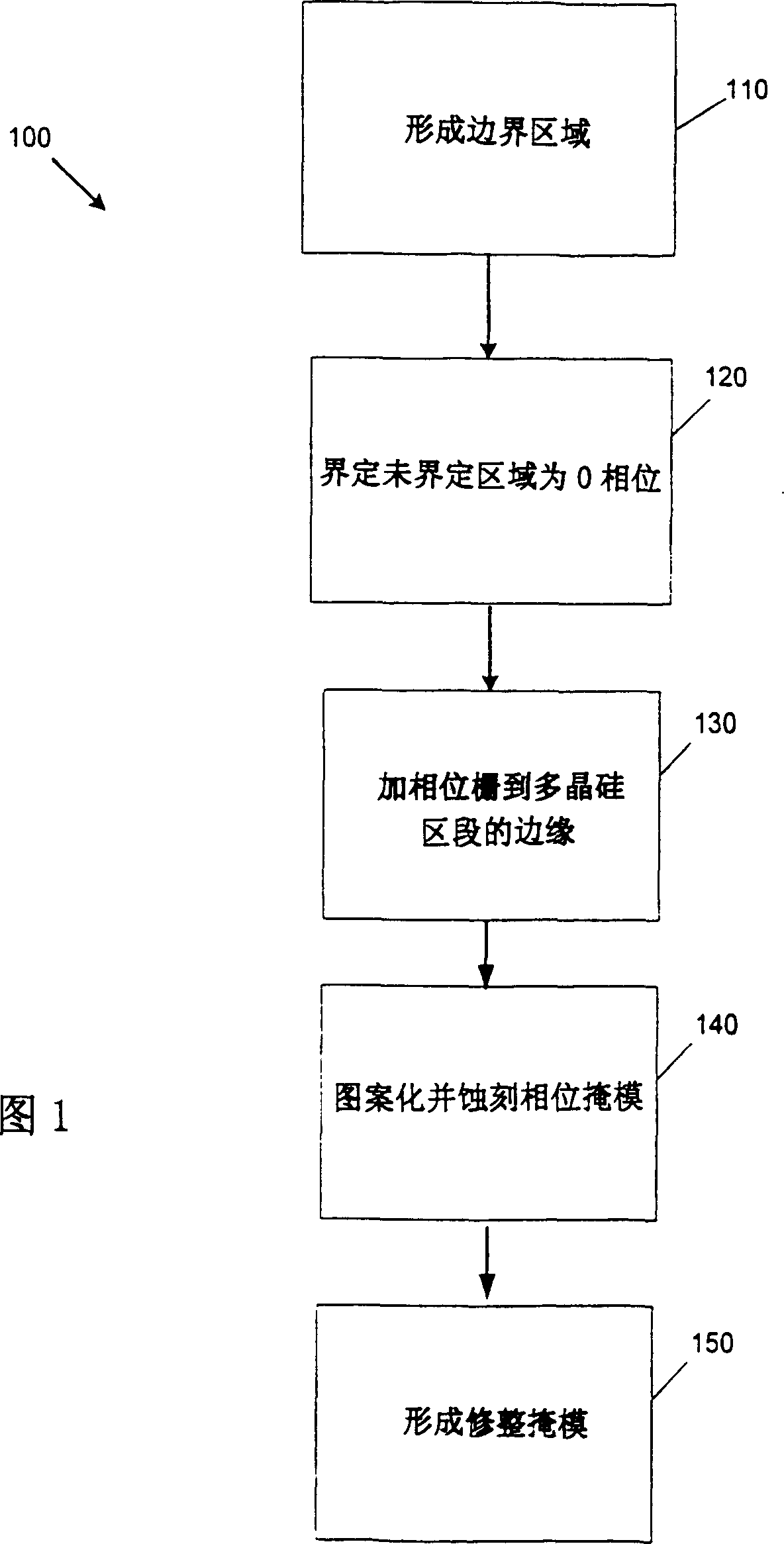

[0029] A flowchart 100 is shown in FIG. 1 to describe typical steps in the composition or design of a phase shift mask (PSM) and an electric field or trim mask. A set of pre-defined 0-phase or 180-phase boxes on the phase mask are used to identify a critical polysilicon region. The 0-phase or 180-phase cassettes can be generated by hand, using currently available software programs, or generating an optimal program to define the cassettes.

[0030] In step 110, a chromium border region is formed on the outside of the phase mask at the 180 phase cassette edge of the predefined 180 phase cassette that does not define a final polysilicon patterning. The chrome border area can be defined either by hand or using a computer software program. It is characterized in that the chromium border area allows easy inspection of the mask and easy patterning of the etch step that produces the mask. At step 120, all undefined areas (whether in the final pattern or 180 phase cassette or chrome ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More