Multi-gate dram with deep-trench capacitor and fabrication thereof

A dynamic random access, capacitor technology, applied in static memory, digital memory information, information storage and other directions, can solve the problem of electronic characteristics depending on size and other issues

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

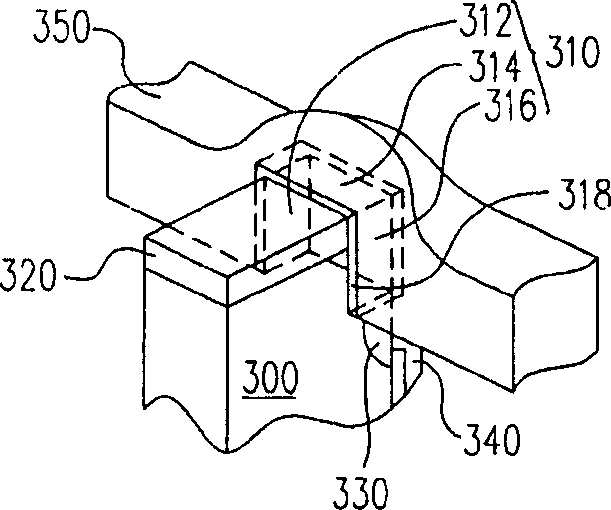

[0166] See image 3, according to the first embodiment, the DRAM cell includes a deep trench capacitor 340, a transistor such as a semiconductor columnar structure 300, a multi-gate structure 310, a gate dielectric layer 318, a first source / drain electrode region 320 and a second source / drain region 330 . The semiconductor pillar structure 300 is disposed beside the deep trench capacitor 340 and does not overlap with the deep trench capacitor 340 . The columnar structure 300 is, for example, a single crystal silicon columnar structure, which may be provided by a single crystal silicon substrate; or, the columnar structure 300 may also be made of other semiconductor materials.

[0167] The multi-gate structure 310 is, for example, a triple-gate structure, including a first gate 312, a second gate 314, and a third gate 316, respectively located on three sidewalls of the columnar structure 300, wherein the first sidewall faces the deep trench For the tank capacitor 340, the oth...

no. 2 example

[0170] see Figure 4 , the DRAM cell includes a deep trench capacitor 440, a transistor such as a semiconductor pillar structure 400, a multi-gate structure 410, a gate dielectric layer 418, a first source / drain region 420 and a second Source / drain regions 430 . The semiconductor columnar structure 400 is disposed beside the deep trench capacitor 440 and does not overlap with the deep trench capacitor 440 .

[0171] The multi-gate structure 410 is, for example, a triple-gate structure, which is composed of a first gate 412, a second gate 414, and a third gate 416, which are respectively arranged on three sidewalls of the columnar structure 400, and the first sidewall faces deep trench capacitor 440, while the other two sidewalls are located next to the first sidewall. The multi-gate structure 410 is only formed on three sidewalls not covering the top portion of the pillar structure 400 , and the multi-gate structure 410 may be a part of the word line 450 . The top surface o...

no. 3 example

[0174] See Figure 5 , a dynamic random access memory cell comprising a deep trench capacitor 540, a vertical transistor such as a semiconductor pillar structure 500, a multi-gate structure 510, a gate dielectric layer 518, a first source / drain region 520 and a second Two source / drain regions 530 . The semiconductor pillar structure 500 is disposed beside the deep trench capacitor 540 and does not overlap with the deep trench capacitor 540 . The multi-gate structure 510 is, for example, a gate surrounding the sidewall of the columnar structure 500, and the columnar structure 500 may have a sufficiently small width, preferably smaller than the feature size, such as between 200 angstroms and 600 angstroms. When applied to a dynamic random access memory device, the phenomenon of complete depletion can be generated in the channel area, so the performance of the device can be significantly improved. The multi-gate structure 510 is, for example, a part of the word line 550. The to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More