Interspace technical method for implementing copper connecting lines in semiconductor device

A process method and semiconductor technology, applied in the fields of semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve the problems of slow circuit running speed, large parasitic capacitance between copper connections, affecting circuit running speed, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

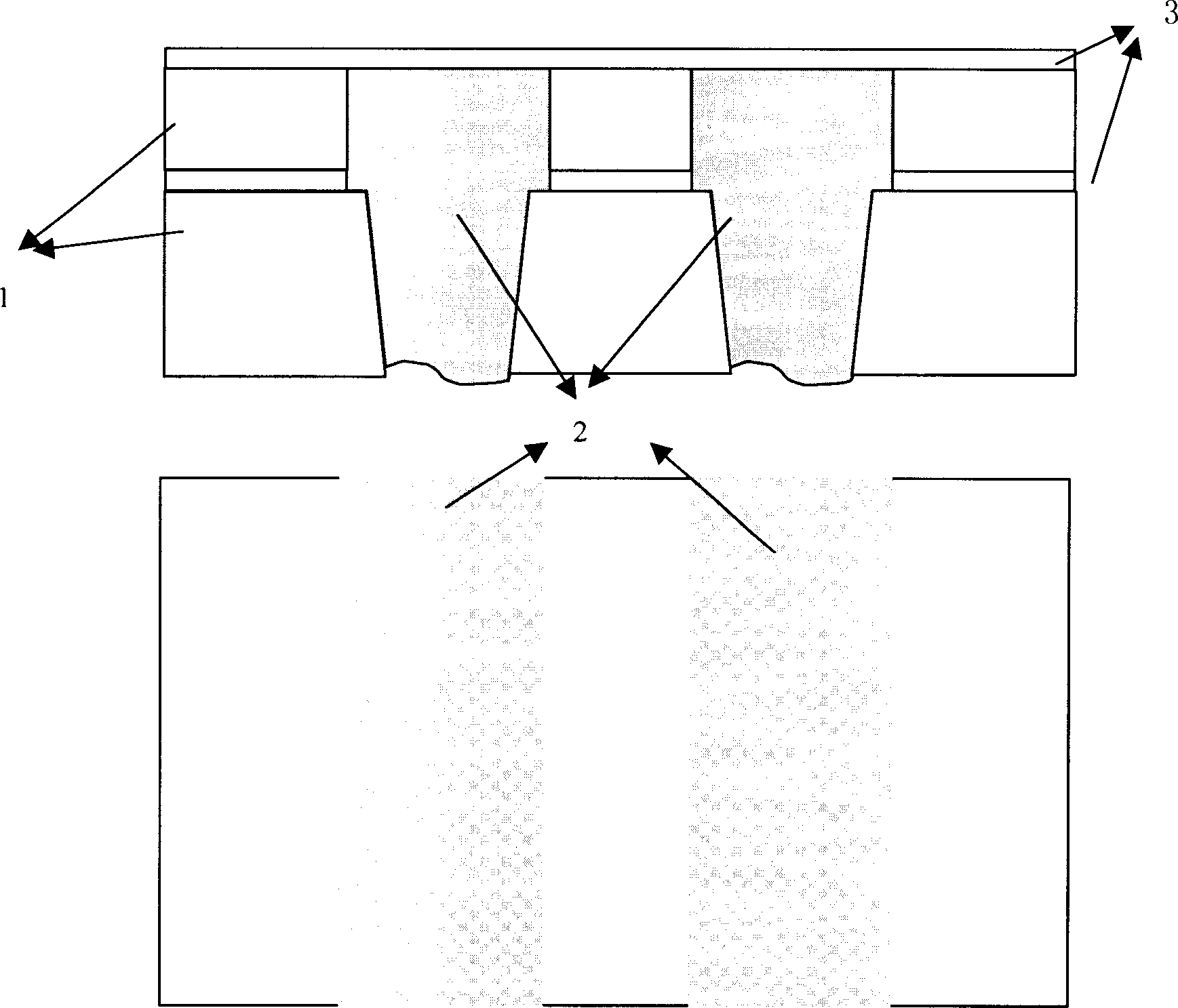

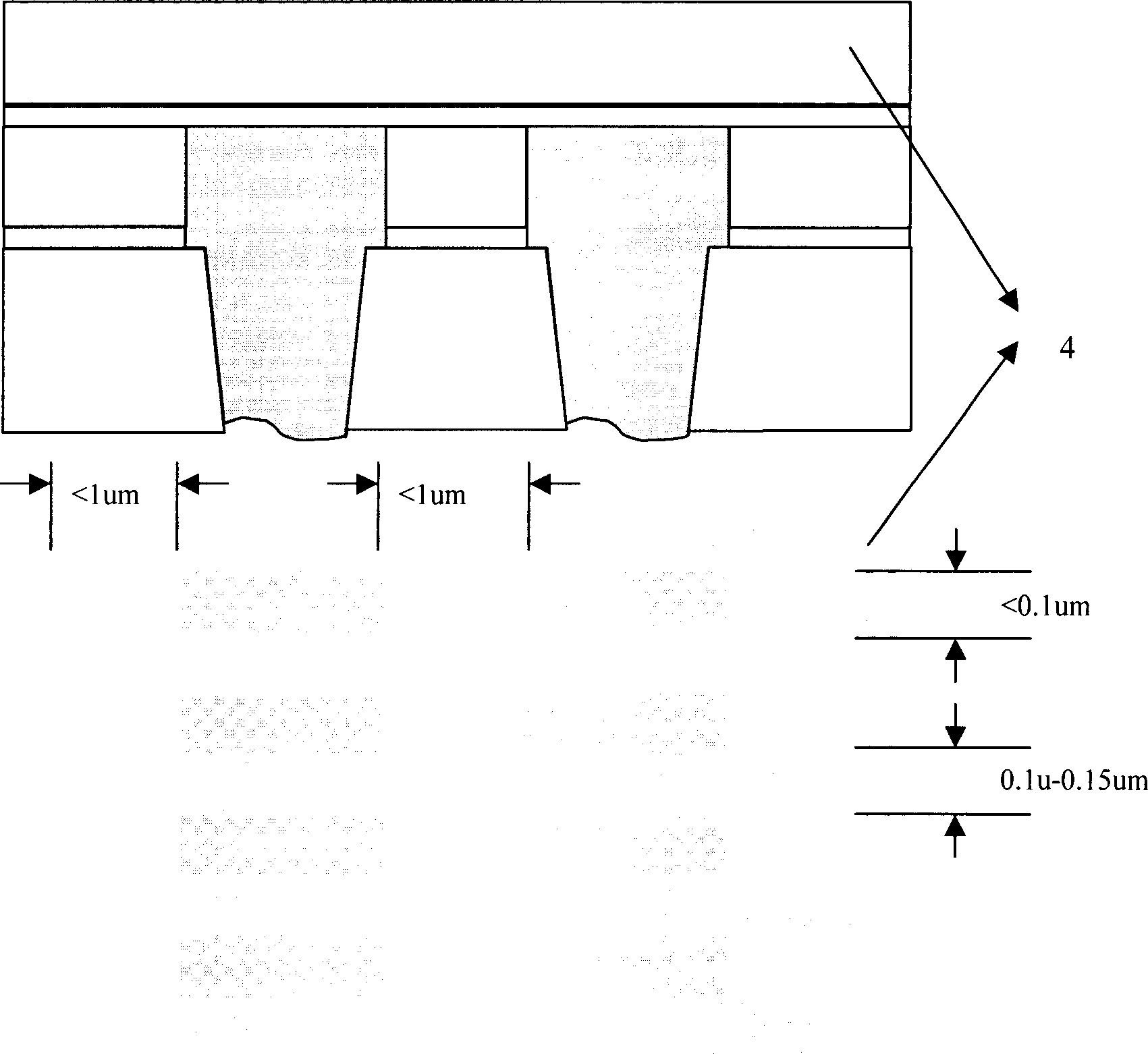

[0012] The process method of implementing copper wiring in semiconductor devices of the present invention is that the last process of making one layer of through holes and copper wiring is copper CMP, and thereafter, a layer of SiN (silicon nitride) is grown. Coat the photoresist on the chip, and do a photolithography with a photolithography plate made by the following method. The photolithography board can be produced according to the pattern of the lower layer copper wire, or can be manually drawn by the layout designer according to the actual situation. The pattern of the photolithography plate requires many small slits along the adjacent copper wires with a spacing of less than 1um and perpendicular to the direction of the copper wires. The size of the slits is less than 0.1um, and the distance between the slits is 0.1-0.15um.

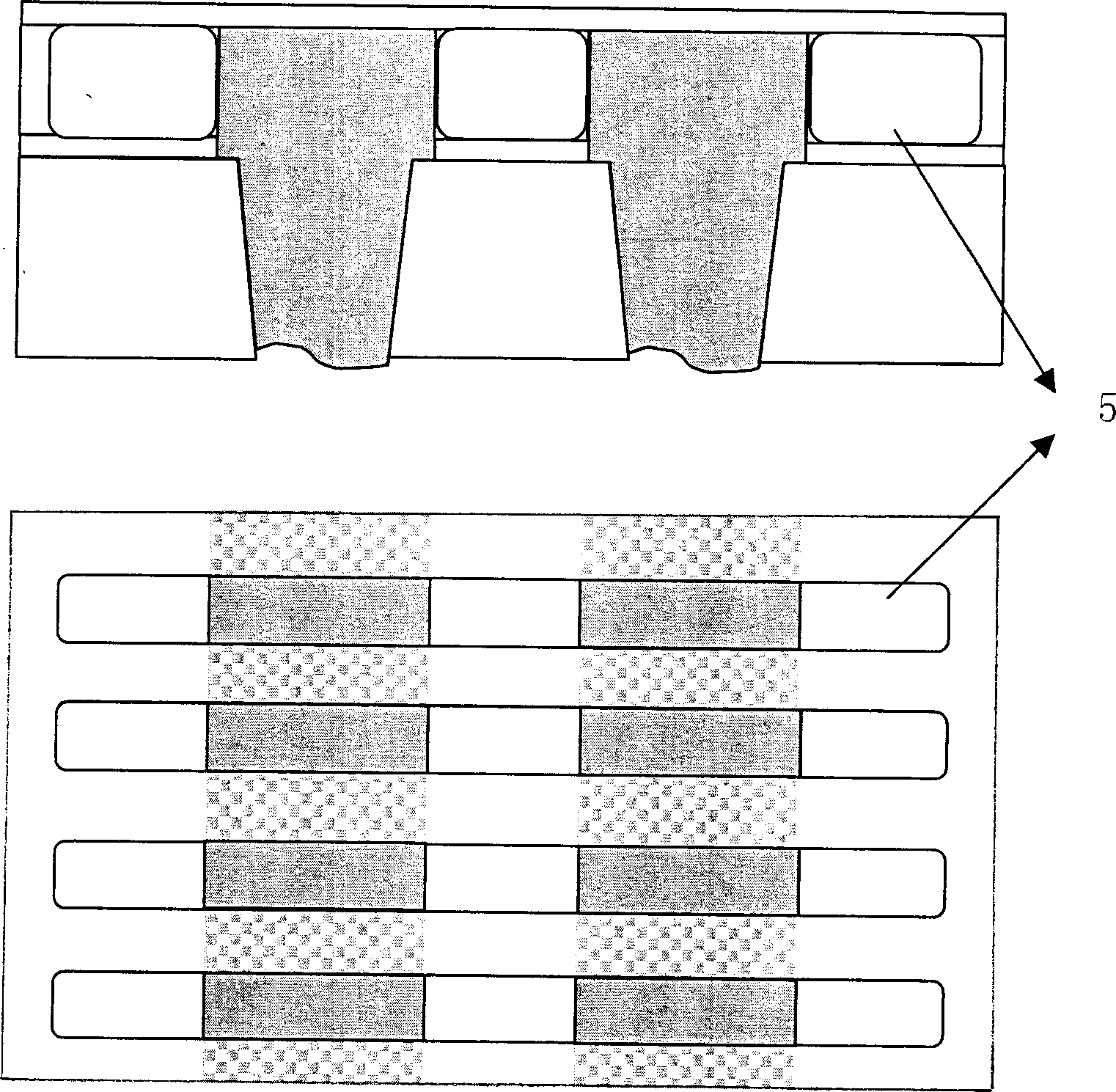

[0013] After this photolithography, apply a dry etching process to etch off the upper layer of SiN and strip off the photoresist. Then use the is...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More