Method for eliminating graphic defects of semiconductor wafer edge region

A semiconductor and edge area technology, which is applied in the field of eliminating defect patterns in the edge area of semiconductor wafers, can solve problems such as easy peeling, reduced manufacturing pass rate, short circuit of qualified patterns, etc., to achieve the effect of improving product pass rate and reducing time extension

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

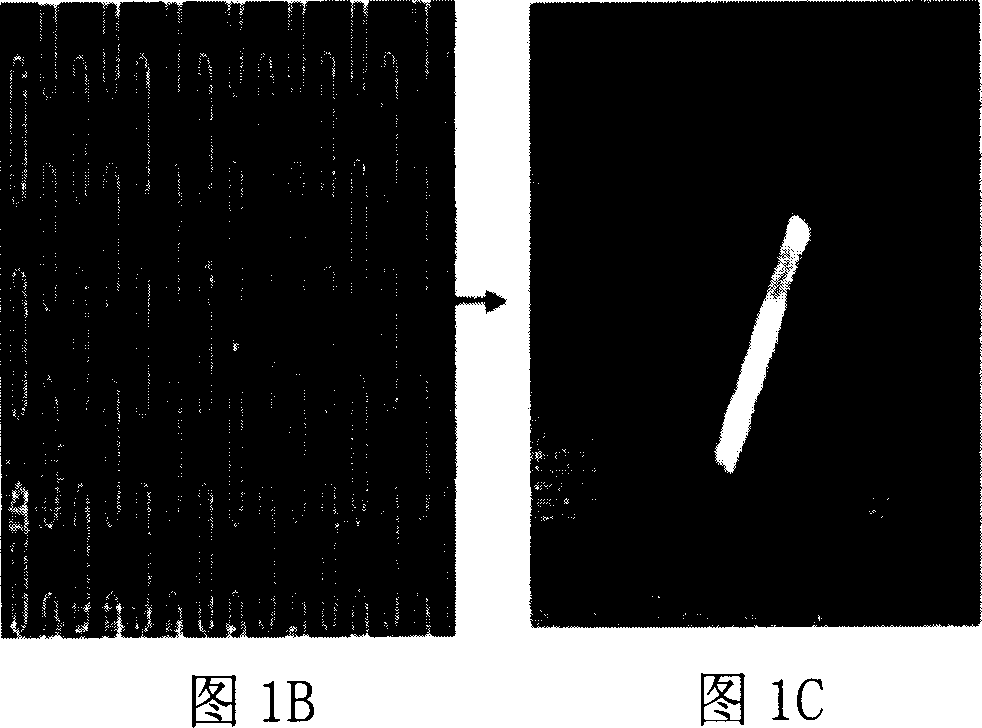

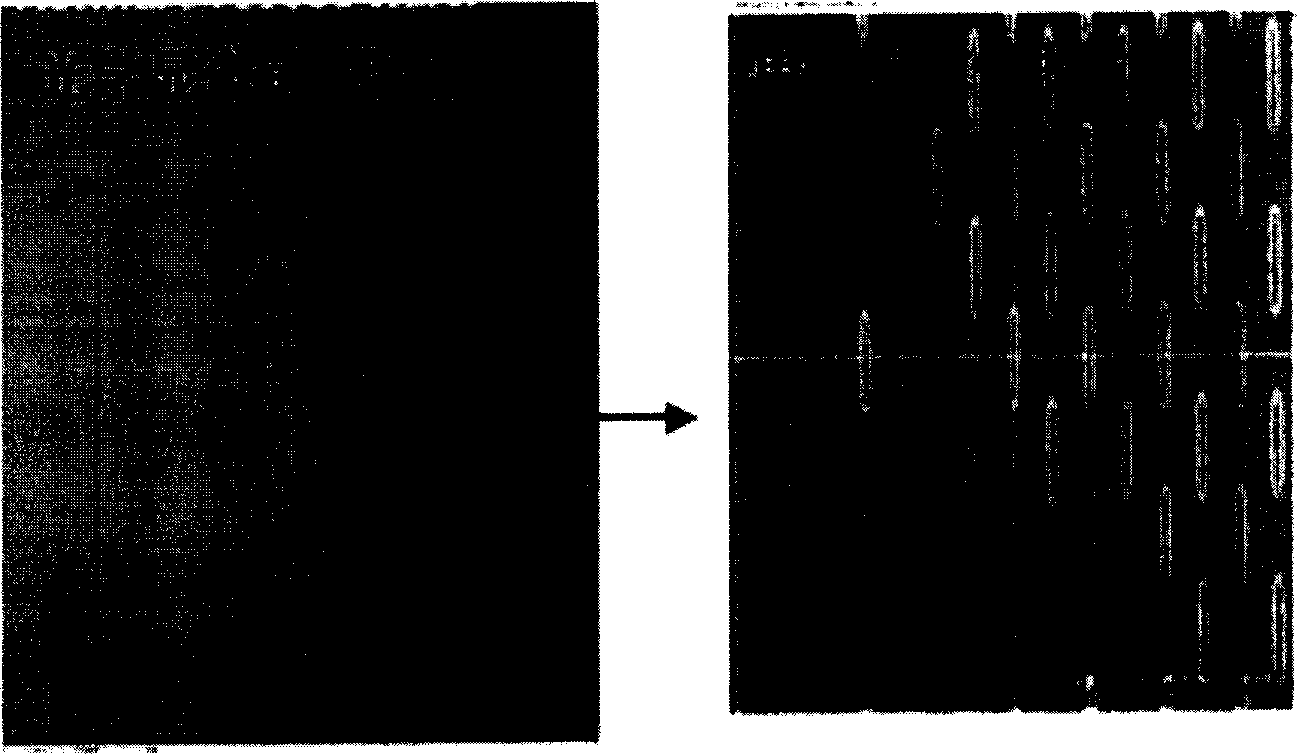

[0031] Taking the active area (Active Area) pattern of a 0.20 μm dynamic random access memory (DRAM) as an example, the method for eliminating pattern defects in the edge area of a semiconductor wafer of the present invention is described.

[0032] The method for eliminating pattern defects in the peripheral regions of semiconductor wafers of the present invention comprises the following process steps:

[0033] 1. Coating photoresist (PR) on the surface of the semiconductor wafer;

[0034] 2. Exposure to photoresist;

[0035] 3. Development;

[0036] 4. Clean the edge area of the semiconductor wafer with a solvent;

[0037] 5. Check;

[0038] 6. Corrosion.

[0039] The new process flow is to add a solvent cleaning step (4) after the step (3) of photoresist development and patterning to remove the abnormal photoresist shrinkage and deformation pattern on the edge of the semiconductor wafer.

[0040] New process flow: coating photoresist→exposing photoresist→developing→...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More