Method for eliminating dc bias for receiver and signal process module

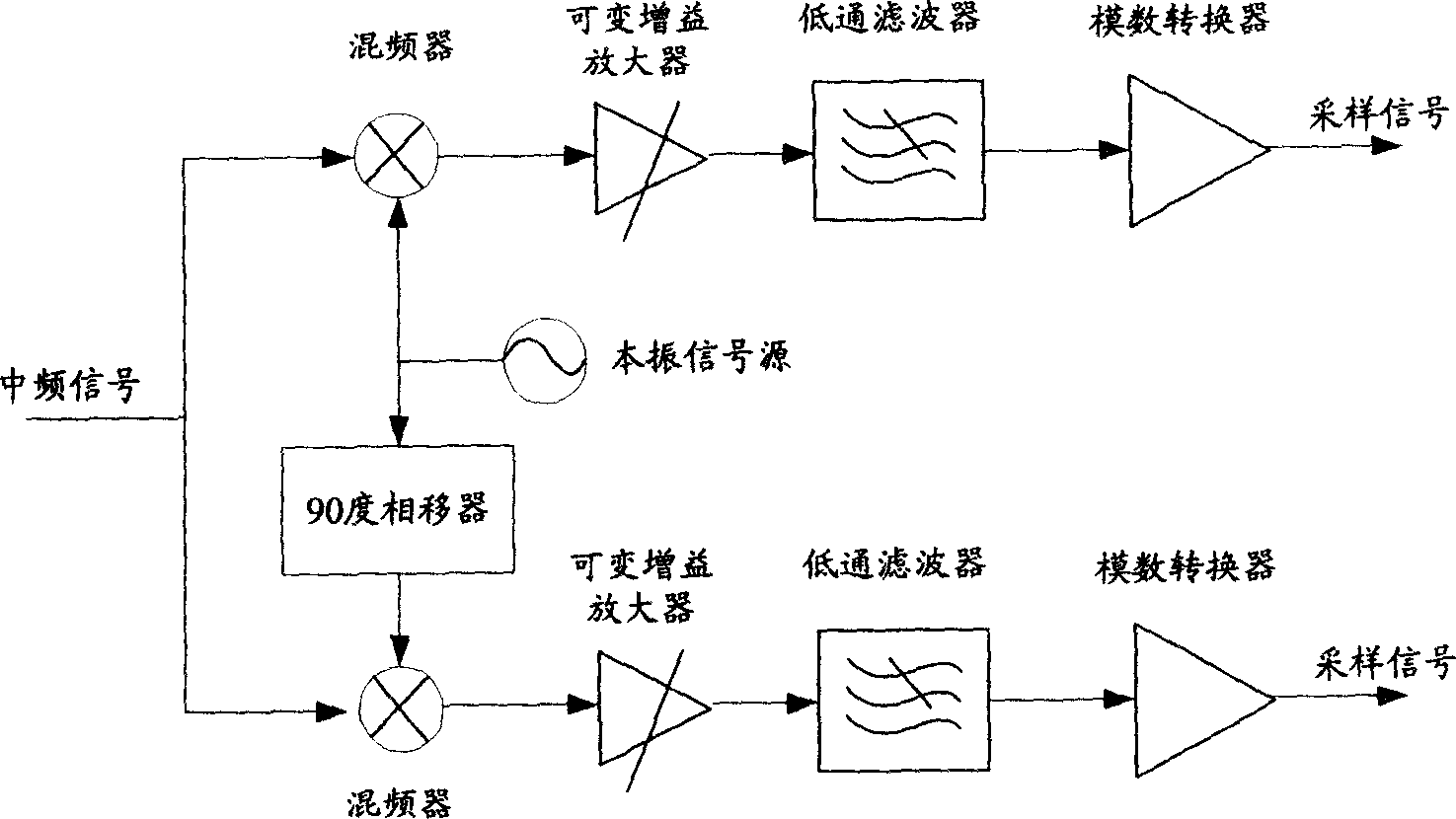

A signal processing module and DC bias technology, applied in the field of receivers, can solve the problem of not being able to simply and accurately eliminate the DC bias of the signal processing module, and achieve the effects of low implementation cost, simple algorithm structure and high computational efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

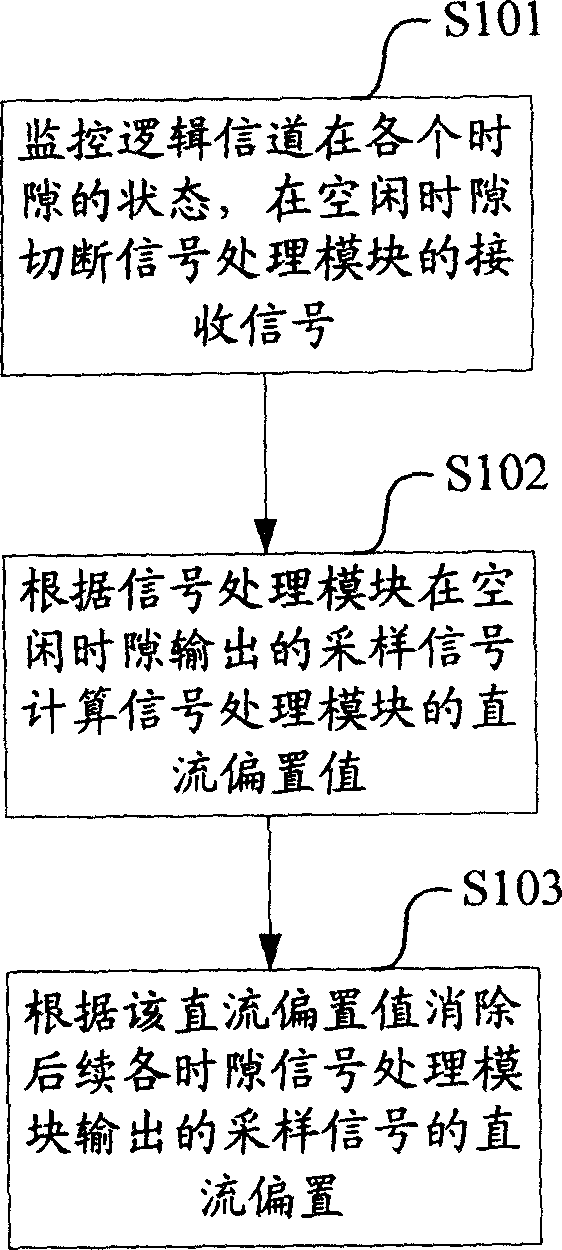

[0040] The core idea of the present invention is that the method for eliminating the DC bias of the signal processing module in the receiver is as follows: figure 2 shown, including the following steps:

[0041] Step S101, monitoring the state of the logical channel in each time slot, and cutting off the received signal of the signal processing module in an idle time slot;

[0042] Step S102, calculating the DC bias value of the signal processing module according to the sampling signal output by the signal processing module in the idle time slot;

[0043] Step S103, eliminating the DC offset of the sampling signals output by the signal processing modules of subsequent time slots according to the DC offset value.

[0044] The present invention will be further described below in conjunction with the embodiments and the accompanying drawings.

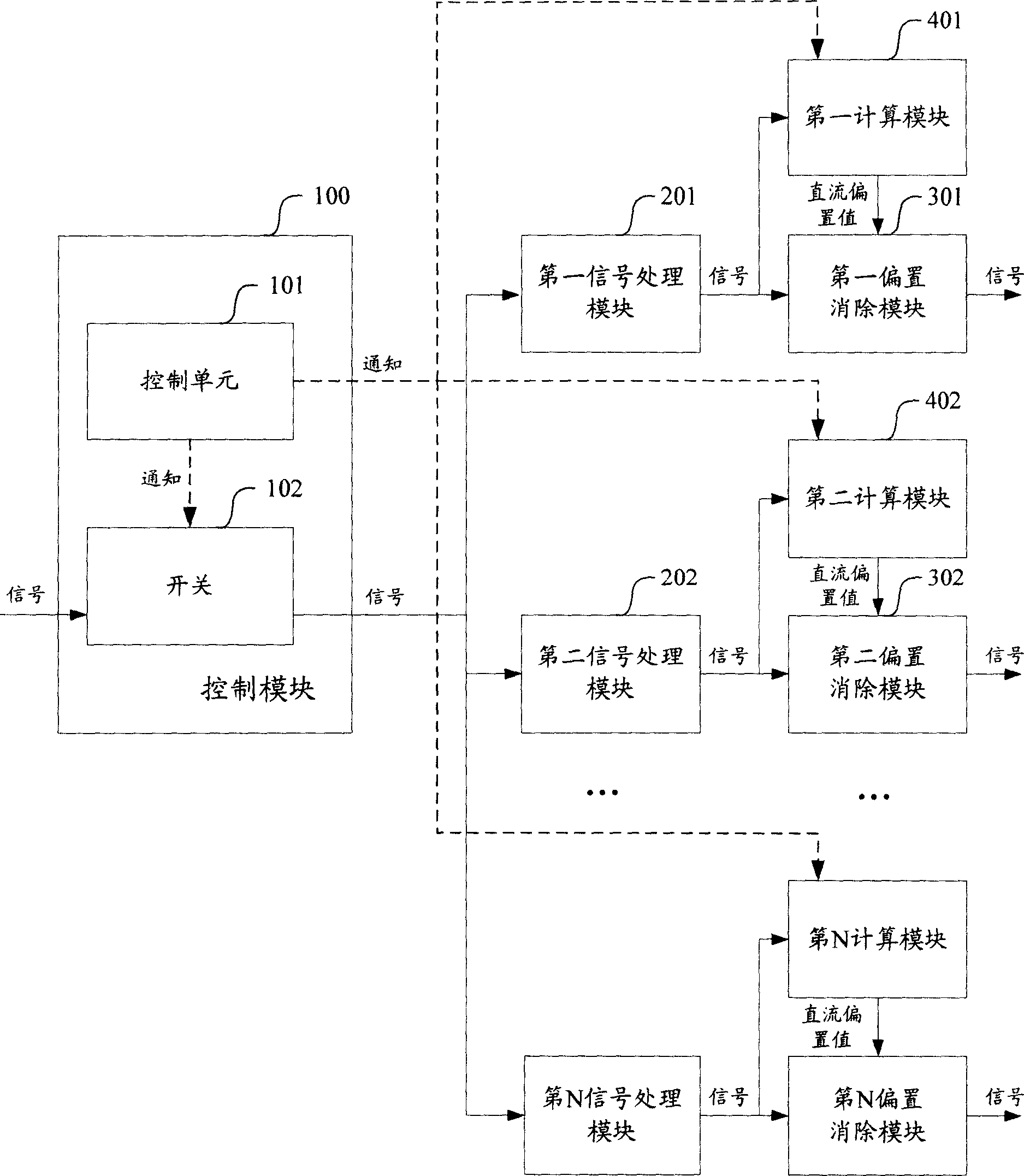

[0045]The connection relationship between the signal processing module in the receiver of this embodiment and the control module 100...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More