Method for improving voltage distribution of component threshold value

A threshold voltage distribution and device technology, applied in semiconductor/solid-state device manufacturing, circuits, electrical components, etc., can solve the problems of threshold voltage distribution device characteristic drift, poor device stability, etc., to reduce LDD atomic diffusion, reduce leakage current, Effect of Uniform Threshold Voltage Distribution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

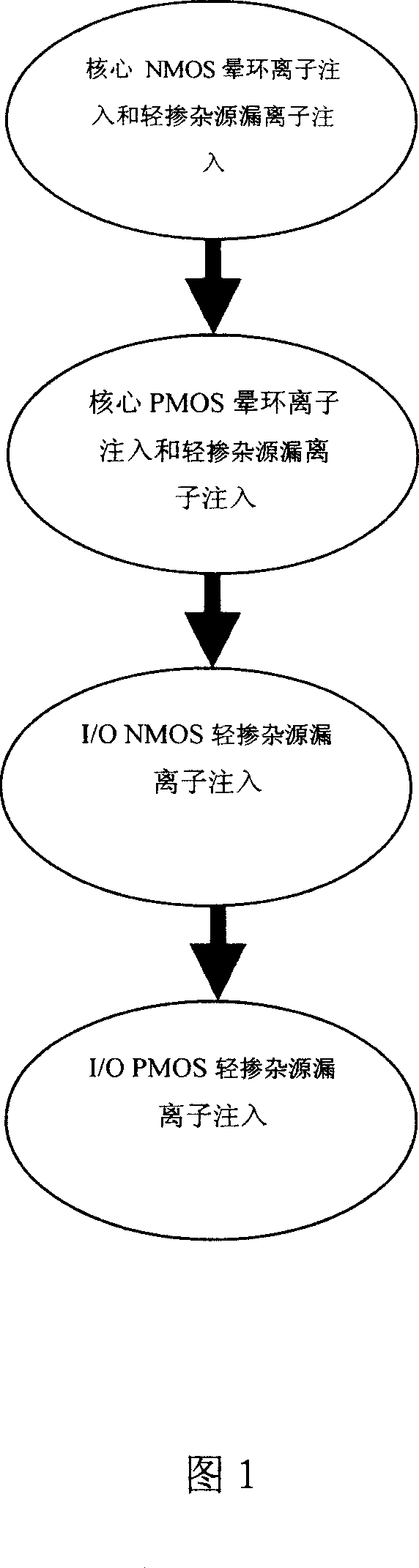

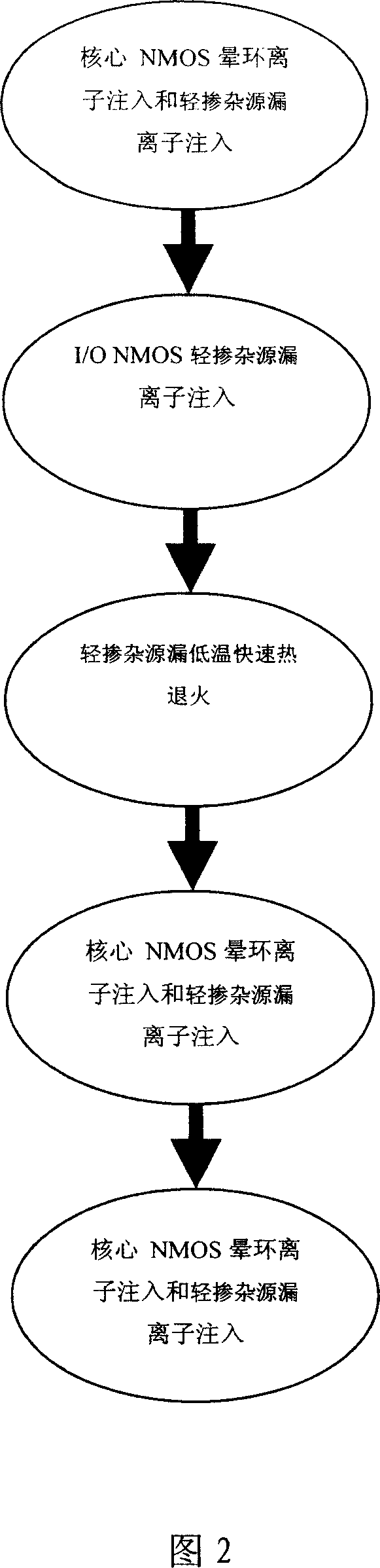

[0013] As shown in Figure 2, a kind of method step of improving device threshold voltage distribution of the present invention is: at first, carry out core NMOS halo ion implantation and LDD ion implantation; Second step, I / O NMOS LDD ion implantation; Third step, LDD low temperature rapid thermal annealing; the fourth step, core PMOS halo ion implantation and LDD ion implantation; fifth step, I / O PMOS LDD ion implantation. The conditions of the LDD low-temperature rapid thermal annealing in the third step may be that the temperature is 950° C., and the low-temperature rapid thermal annealing time is 10 seconds.

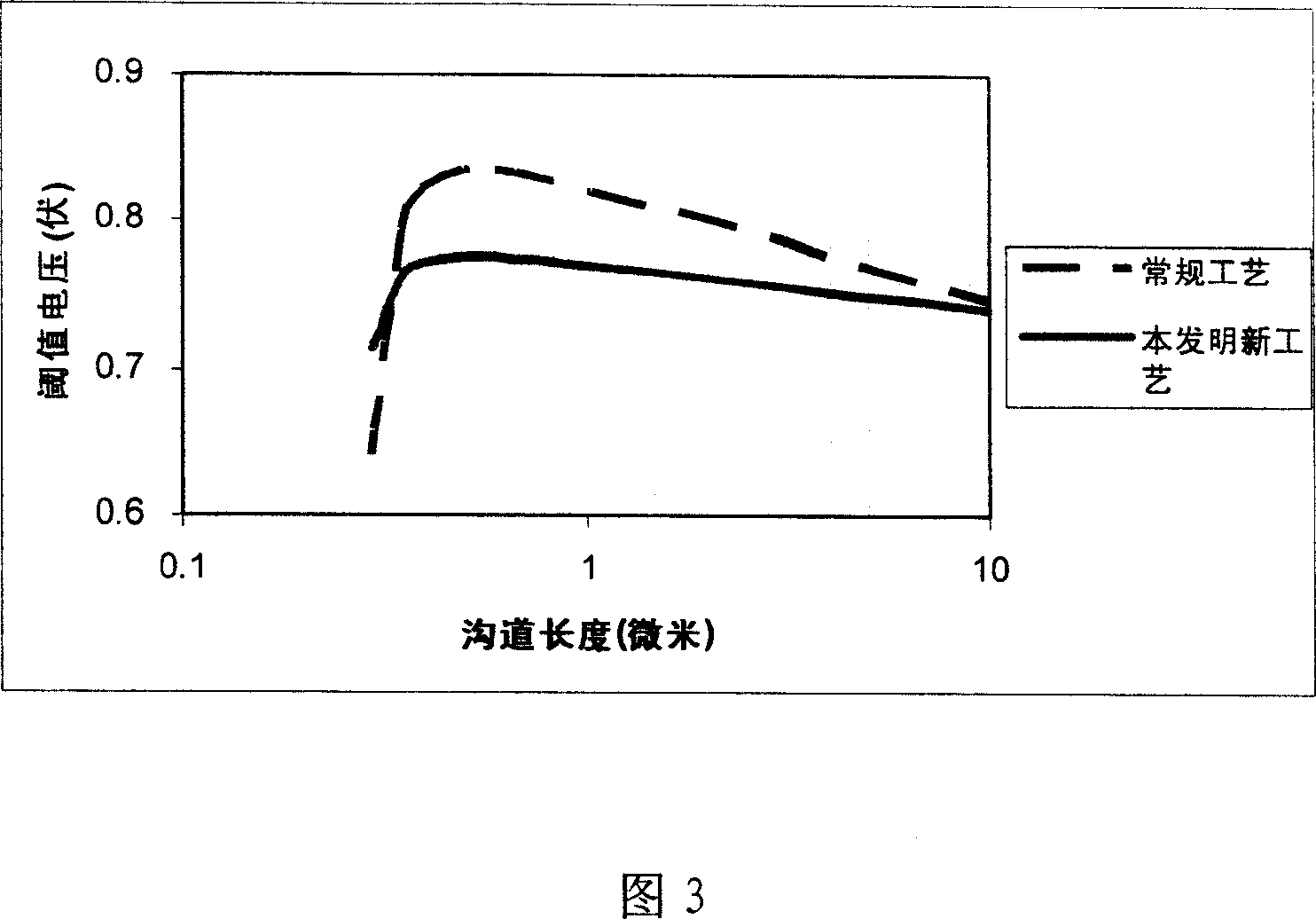

[0014] The invention discloses a method for improving the threshold voltage distribution of devices, which adopts low-temperature rapid thermal annealing after I / O NMOS LDD ion implantation to eliminate lattice defects, eliminate interstitial atoms and vacancies, and reduce boron and phosphorus atoms caused by lattice defects The enhanced diffusion can effectively re...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More