Patents

Literature

40results about How to "Improved Threshold Voltage Distribution" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

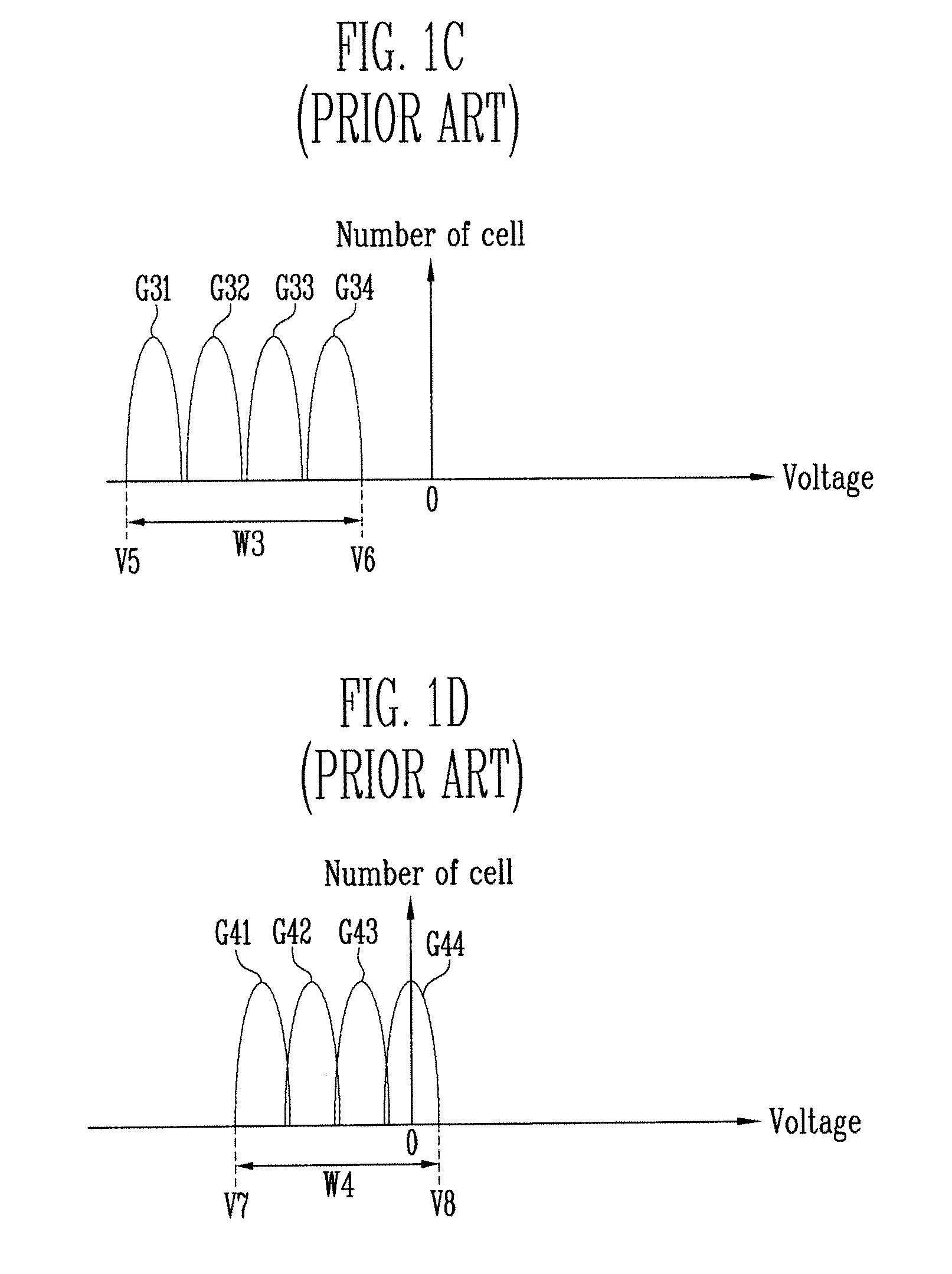

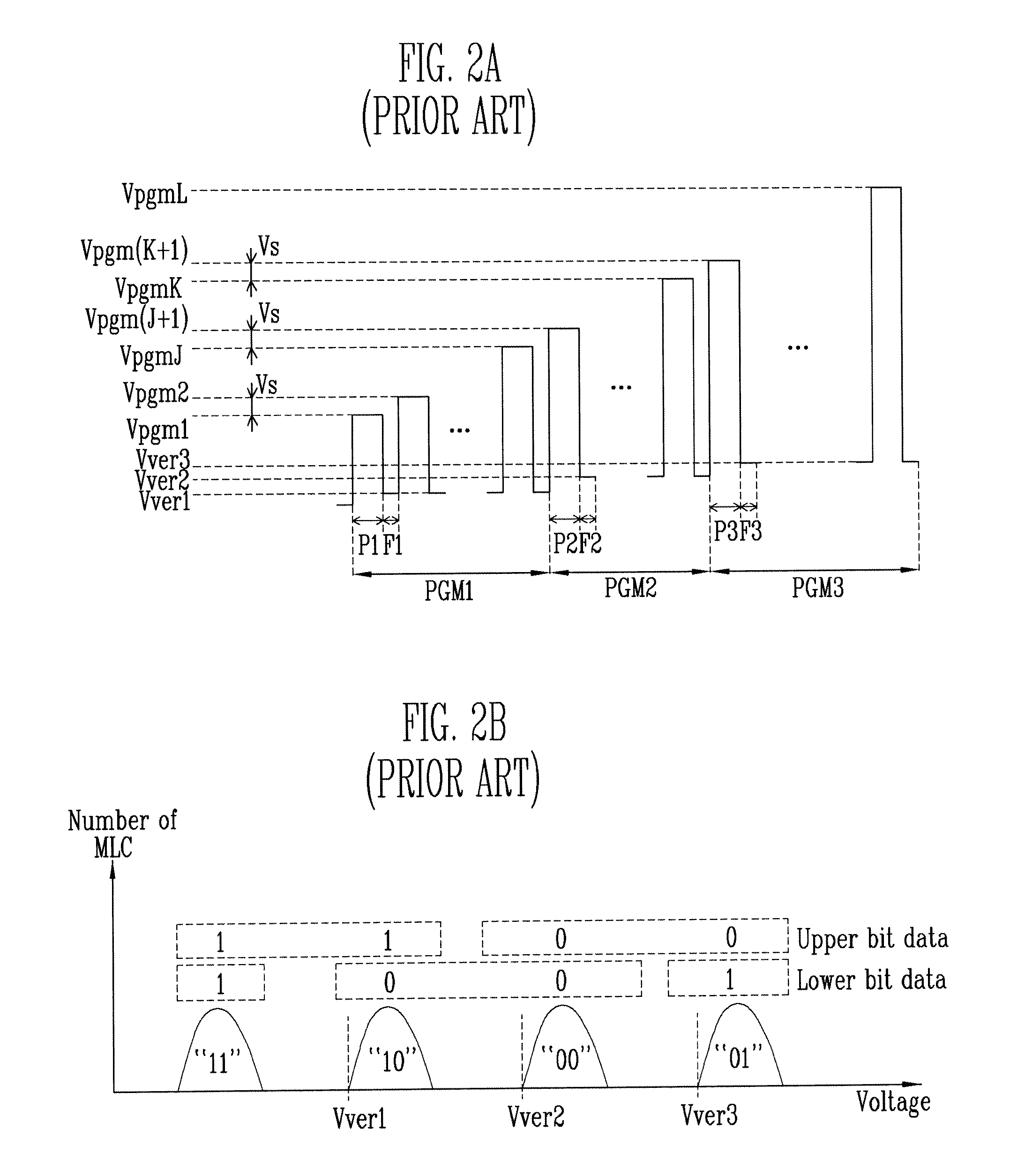

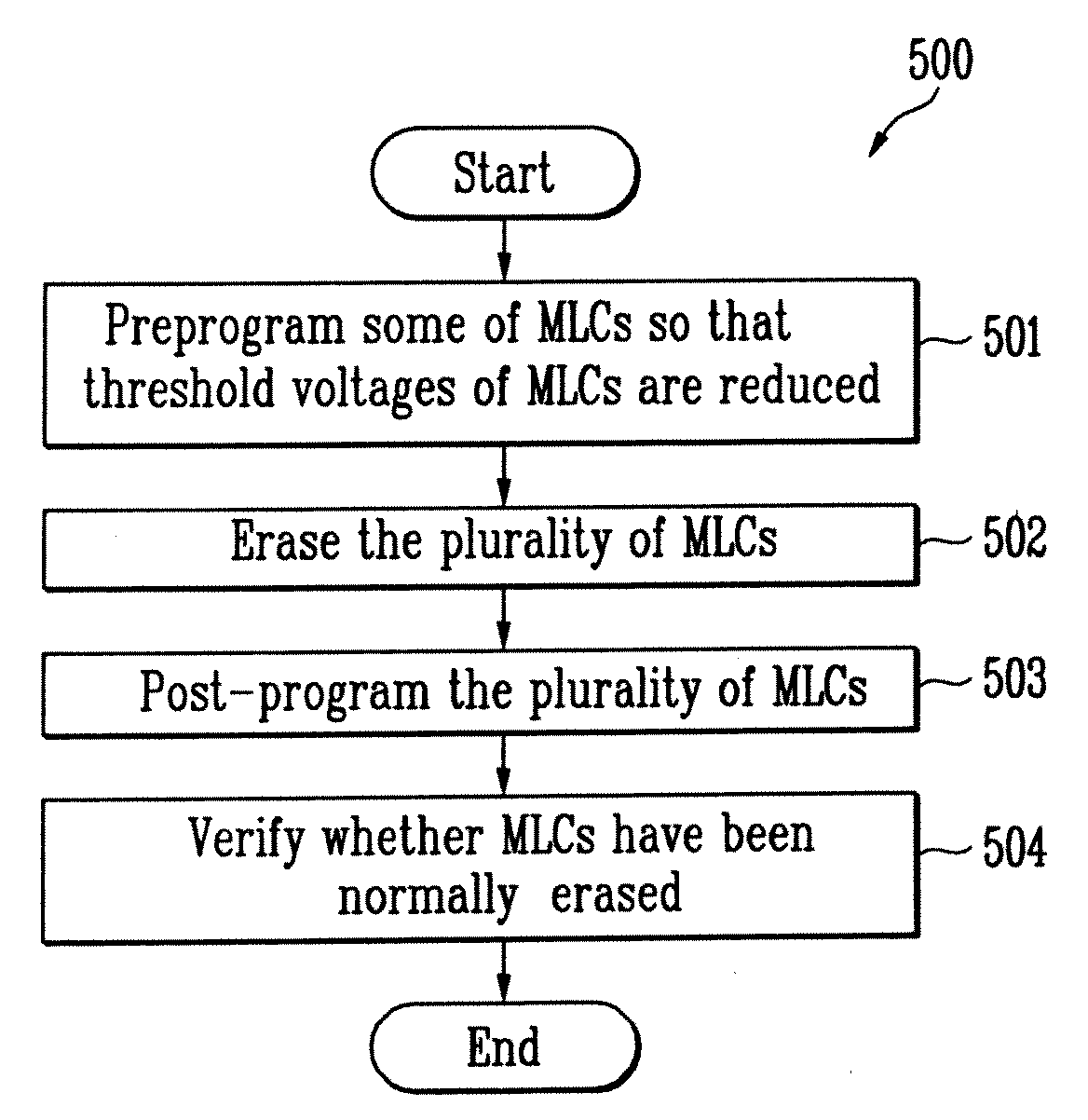

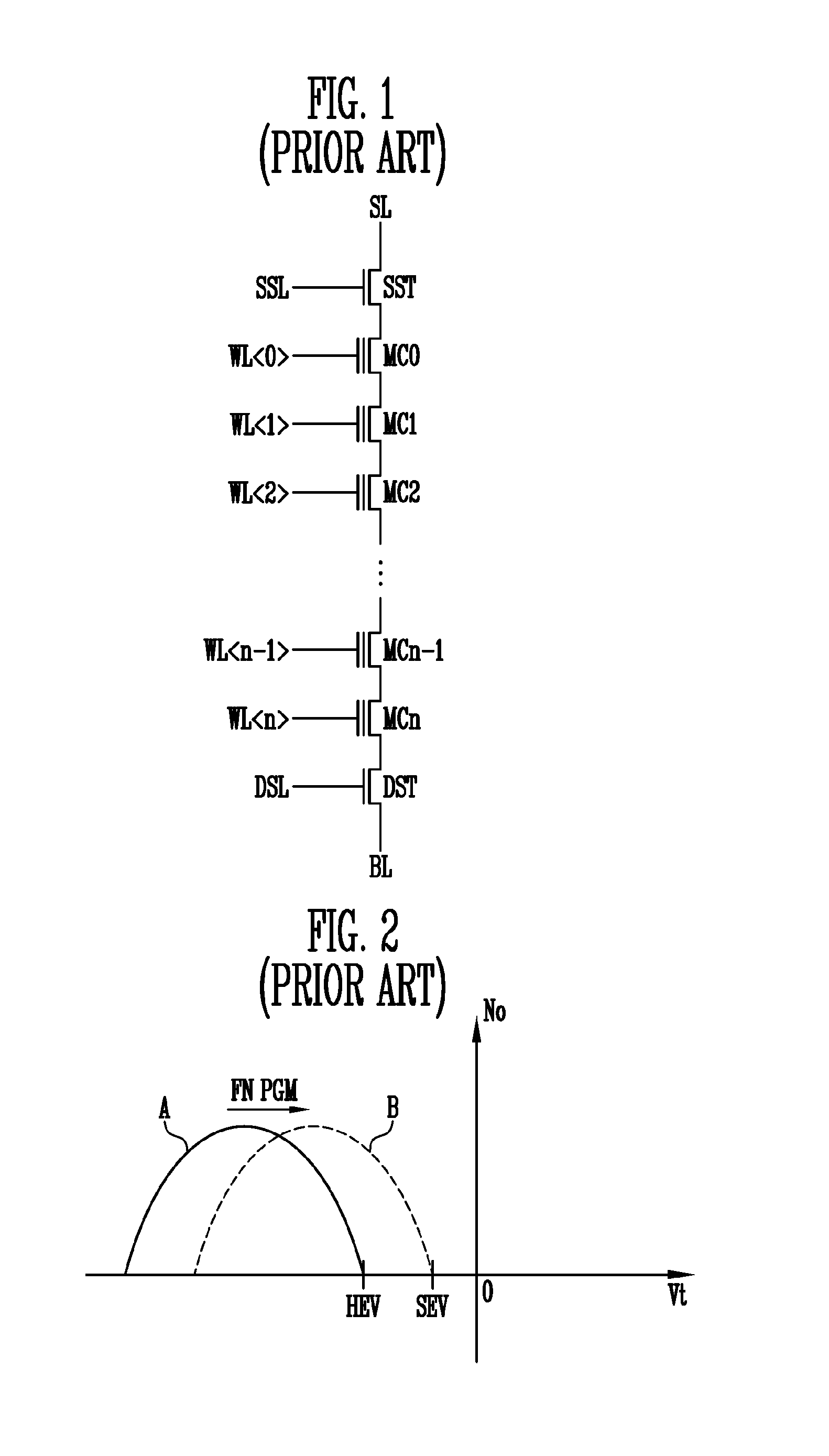

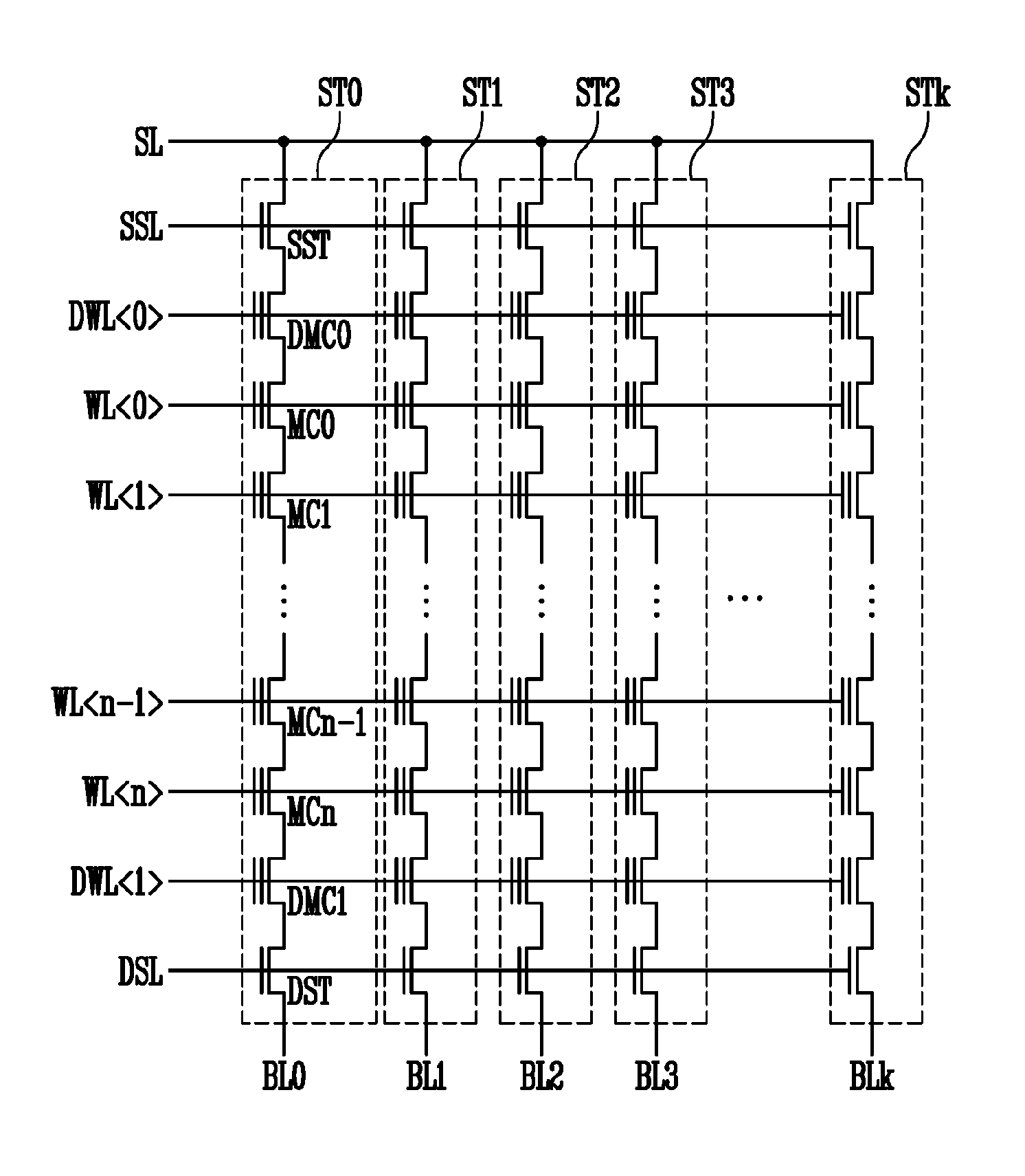

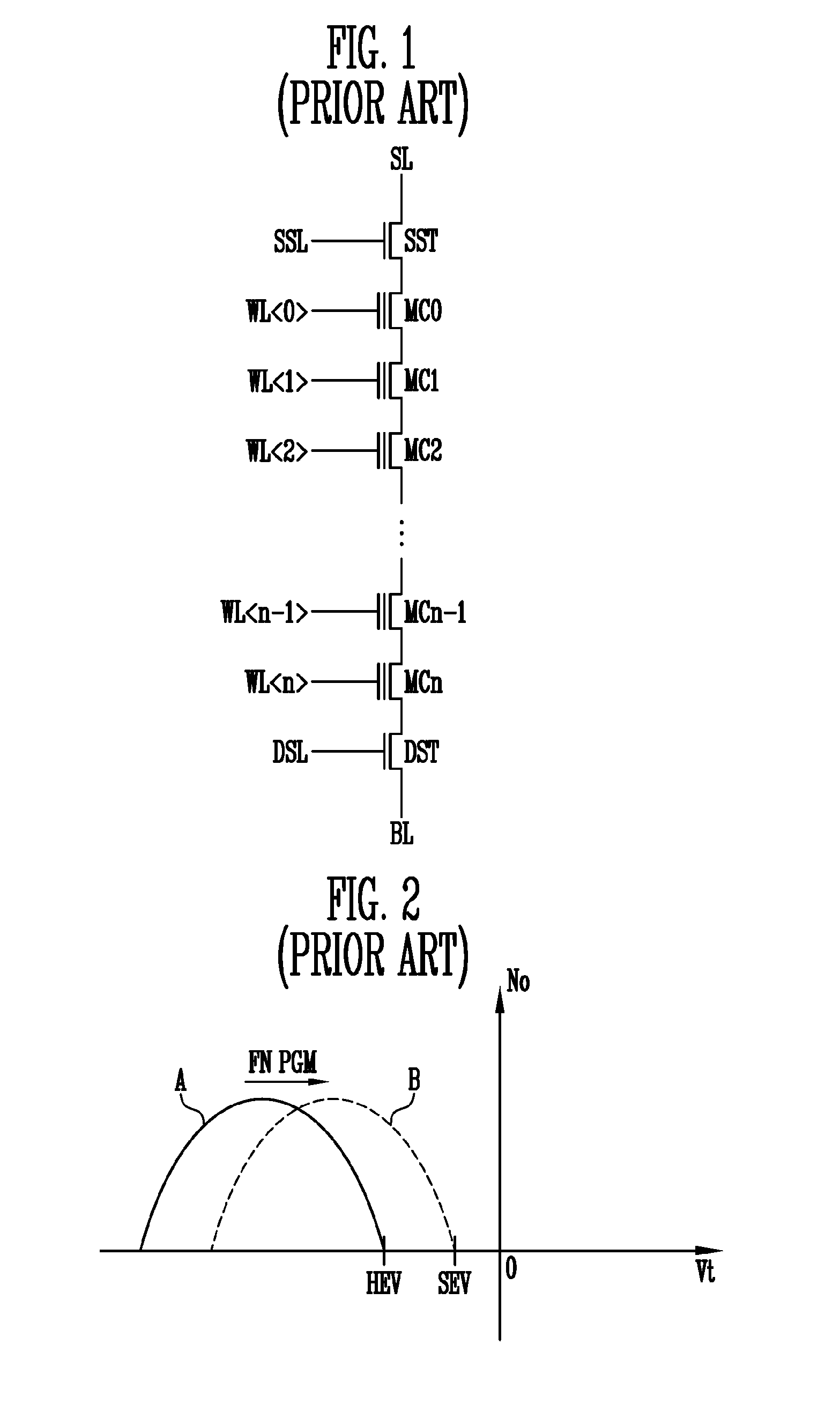

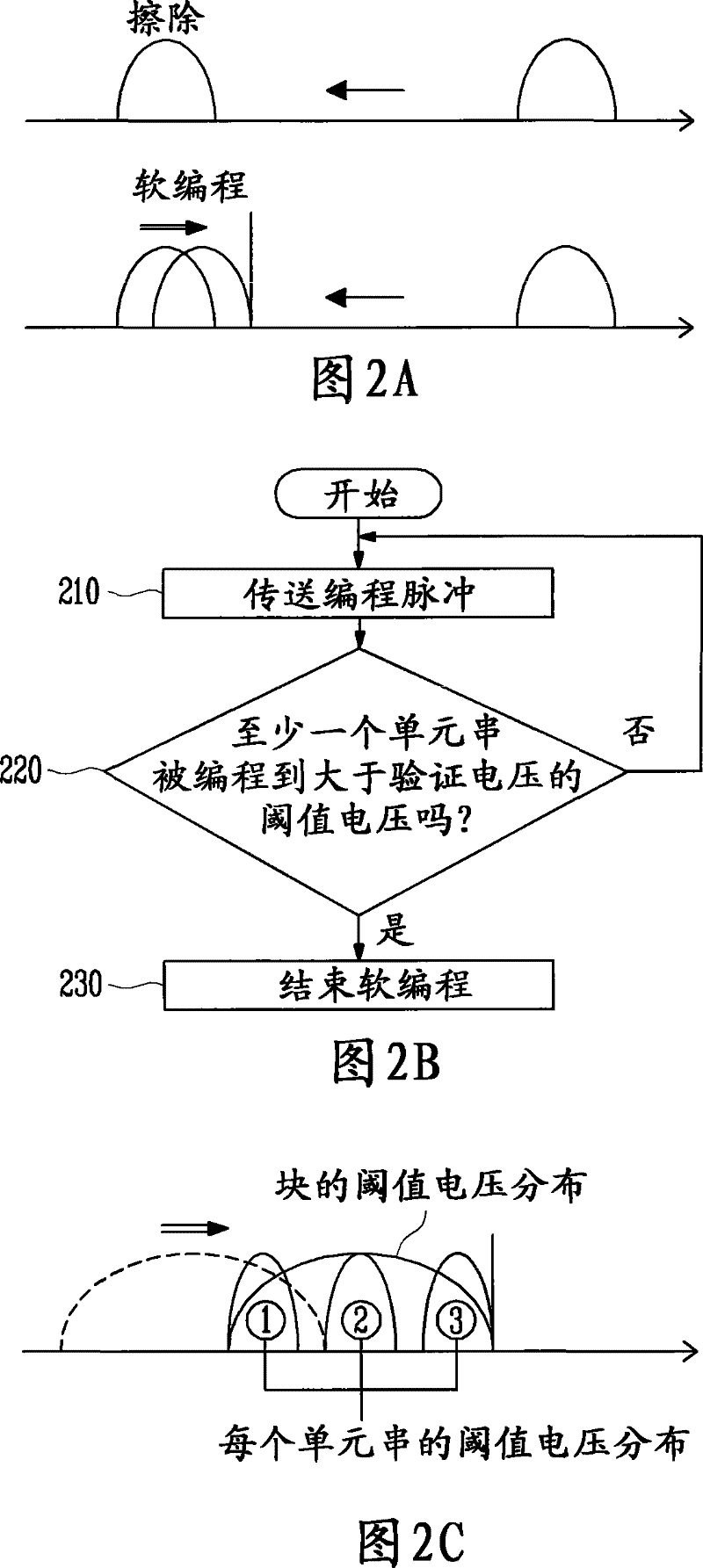

Erase and Program Method of Flash Memory Device for Increasing Program Speed of Flash Memory Device

ActiveUS20070058446A1Fail occurrence ratioImproved Threshold Voltage DistributionRead-only memoriesDigital storageVoltage rangeThreshold voltage

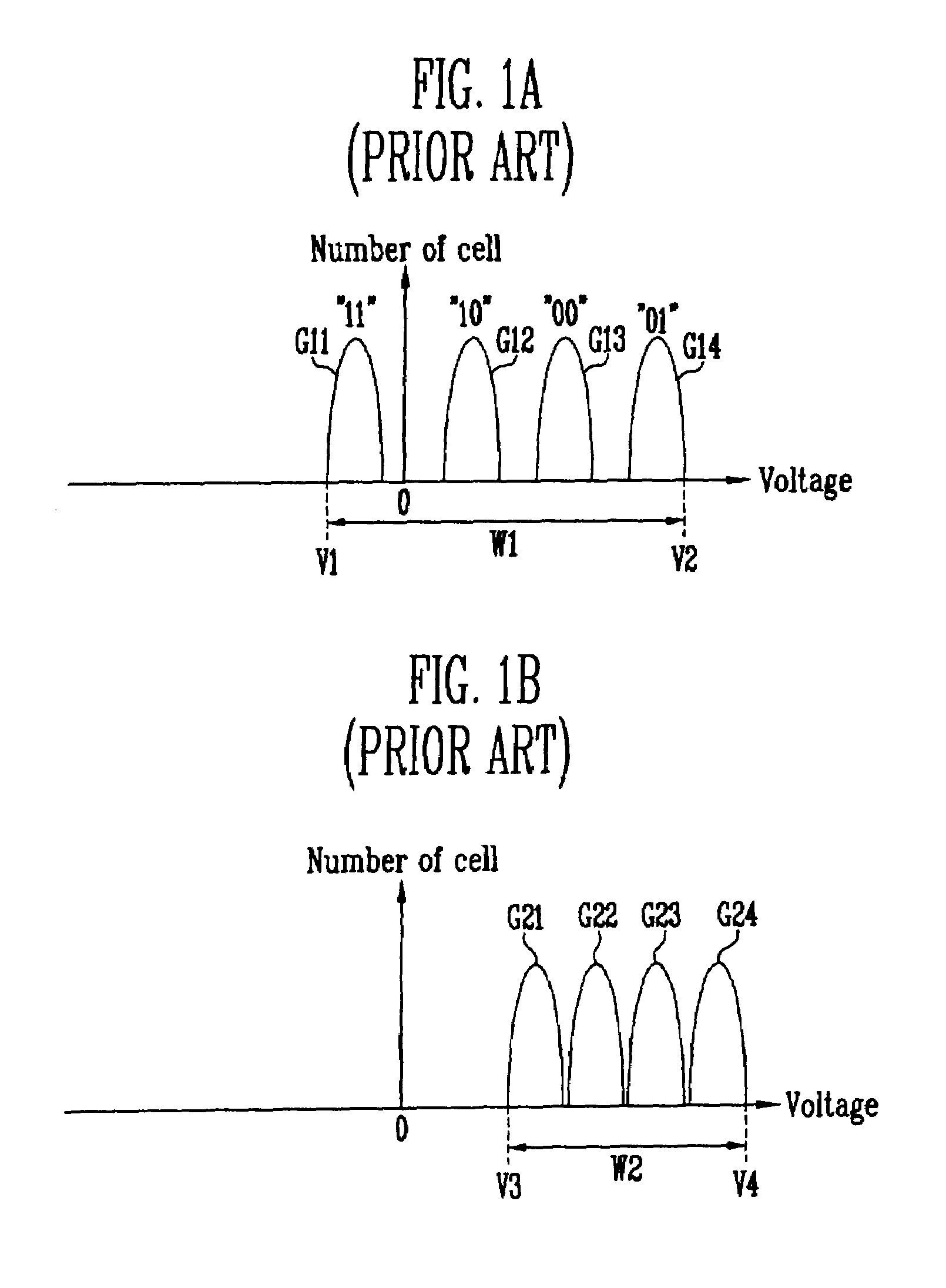

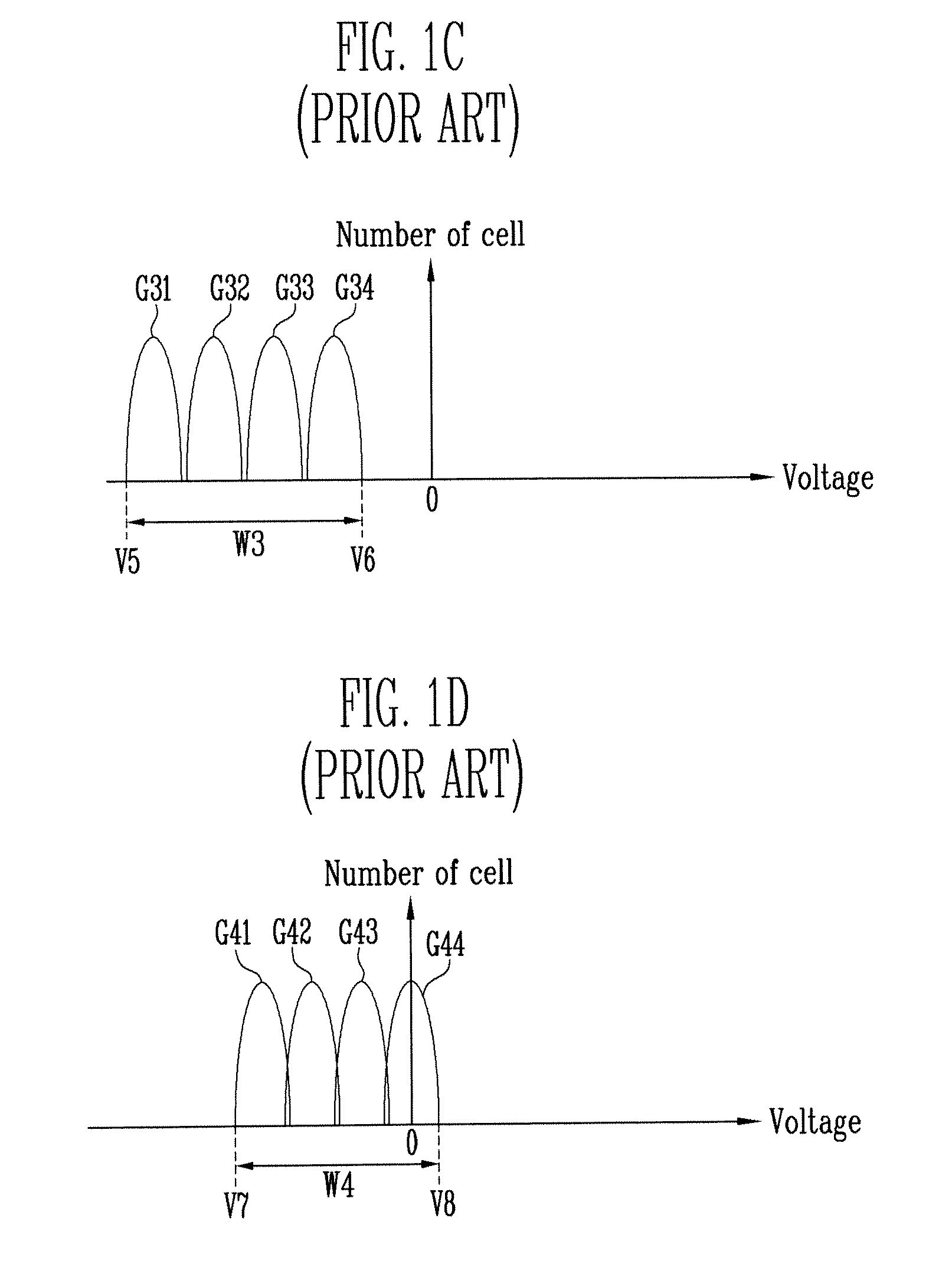

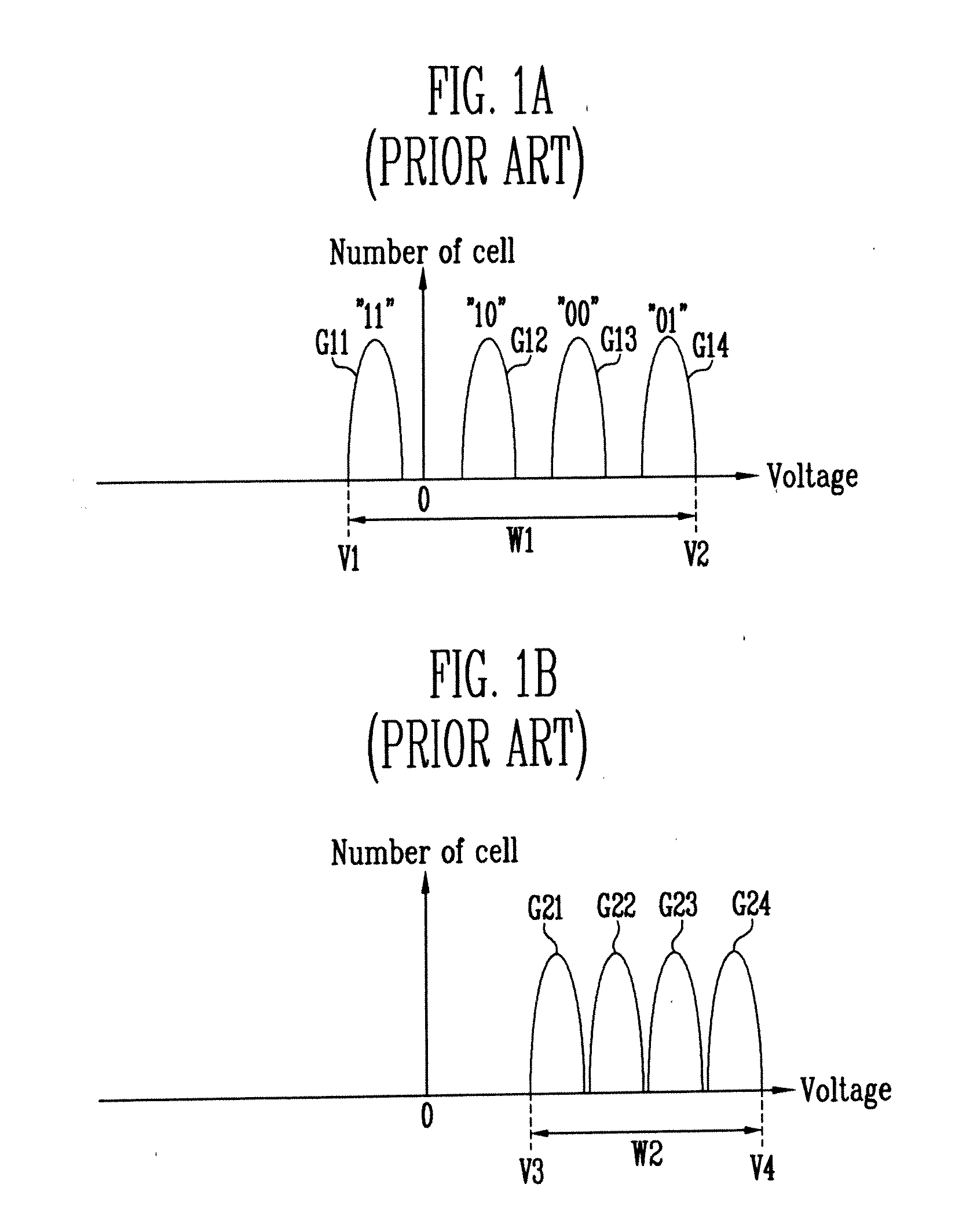

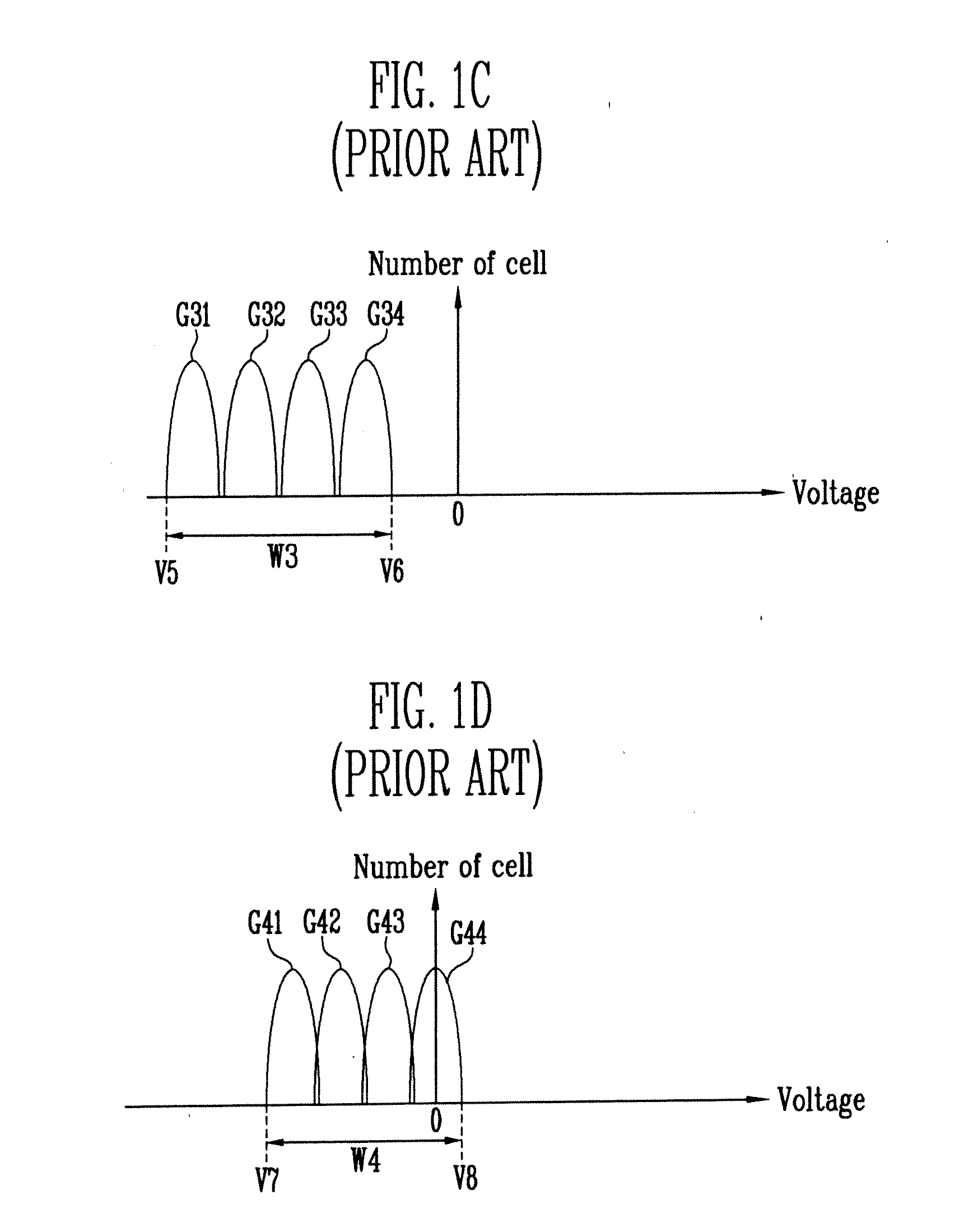

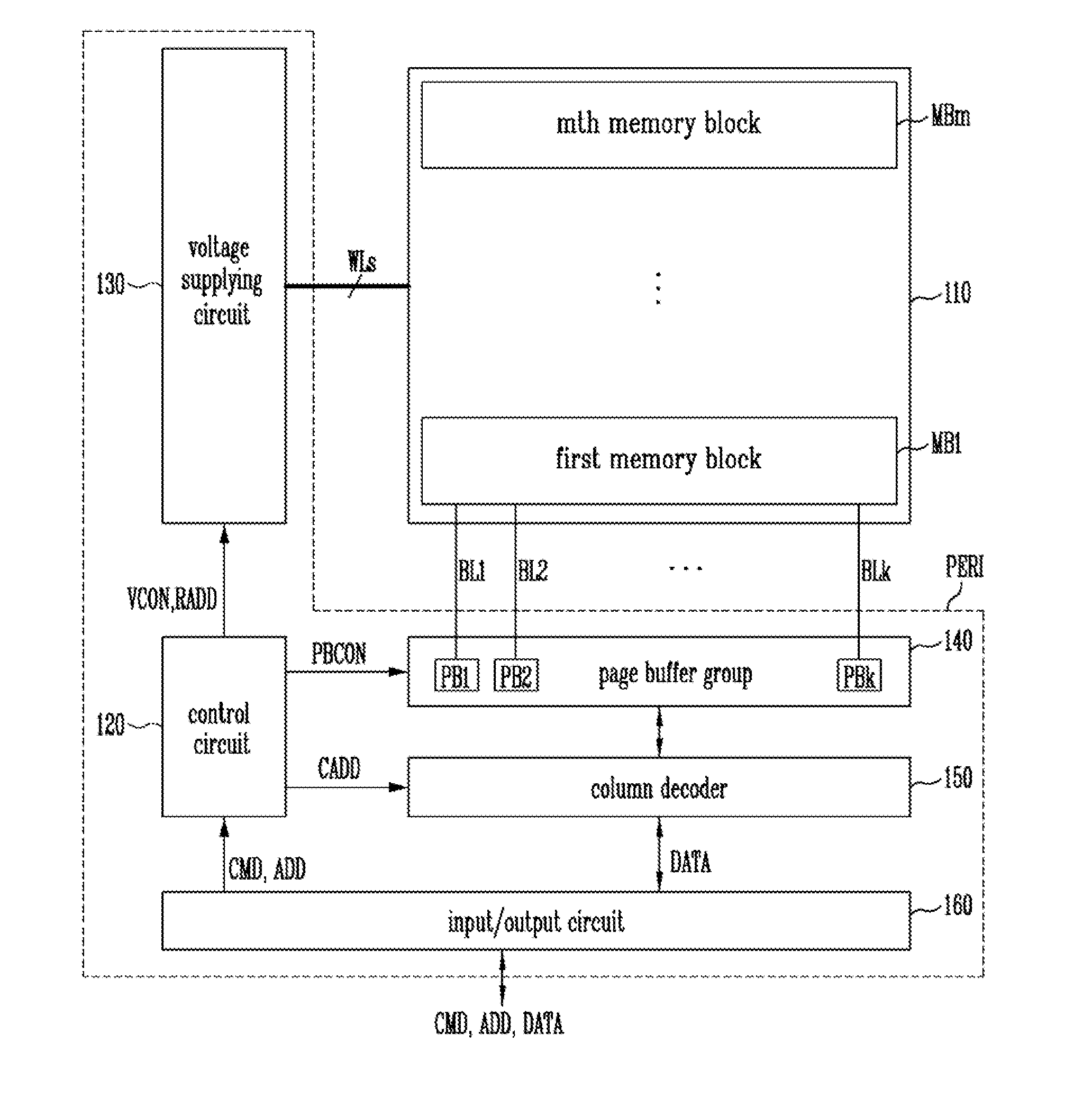

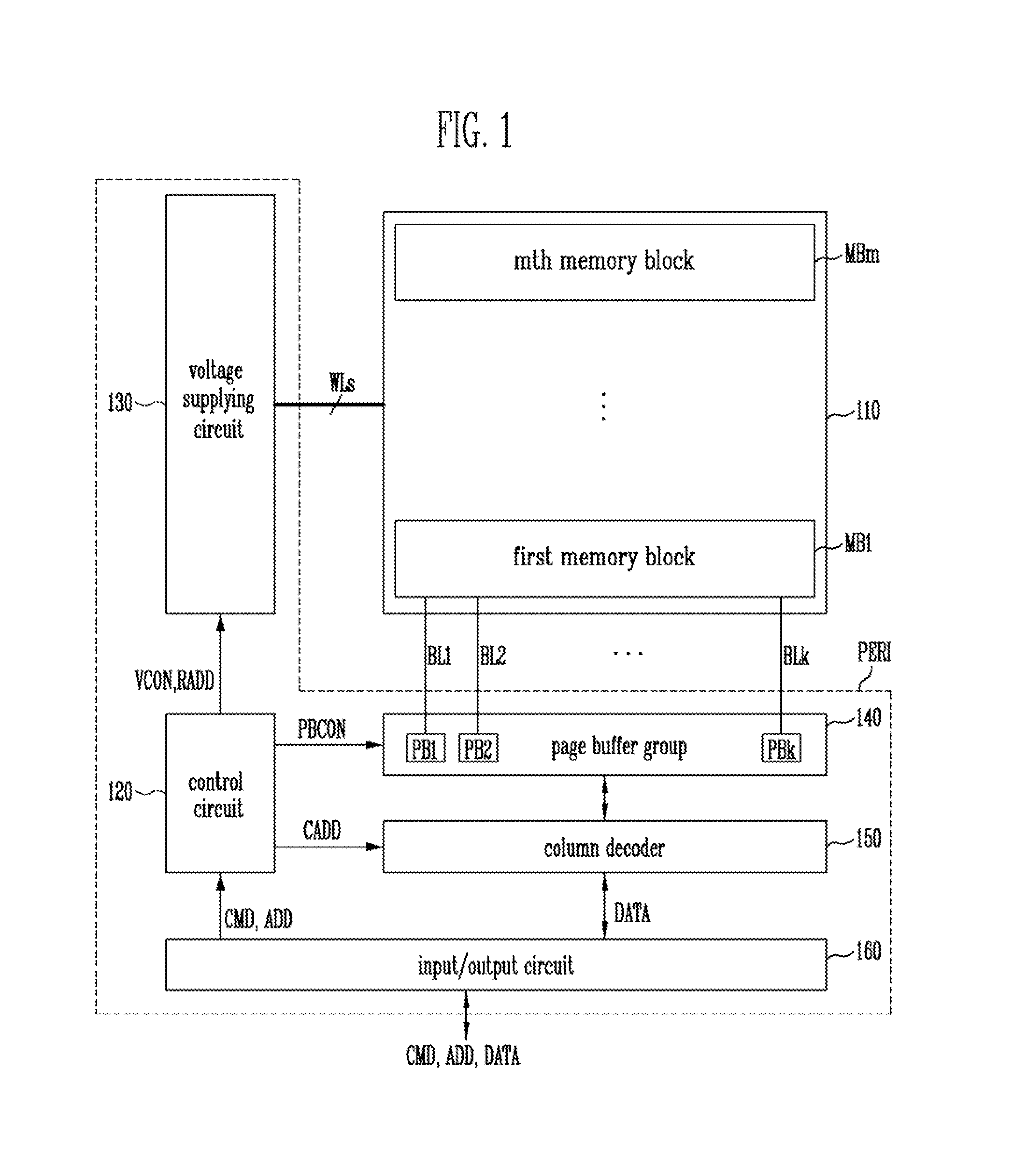

The present invention relates to erase and program methods of a flash memory device including MLCs for increasing the program speed. In the erase method according to the present invention, MLCs are pre-programmed so that a voltage range in which threshold voltages of MLCs are distributed can be reduced. Therefore, a fail occurrence ratio can be reduced when erasing MLCs, the threshold voltage distribution of MLCs can be improved and an overall program time can be shortened in a subsequent program operation.

Owner:SK HYNIX INC

Erase and program method of flash memory device for increasing program speed of flash memory device

ActiveUS7539057B2Improved Threshold Voltage DistributionFail occurrence ratioRead-only memoriesDigital storageVoltage rangeComputer science

Erase and program methods of a flash memory device including MLCs for increasing the program speed are described. In the erase method, MLCs are pre-programmed so that a voltage range in which threshold voltages of MLCs are distributed can be reduced. Therefore, a fail occurrence ratio can be reduced when erasing MLCs, the threshold voltage distribution of MLCs can be improved and an overall program time can be shortened in a subsequent program operation.

Owner:SK HYNIX INC

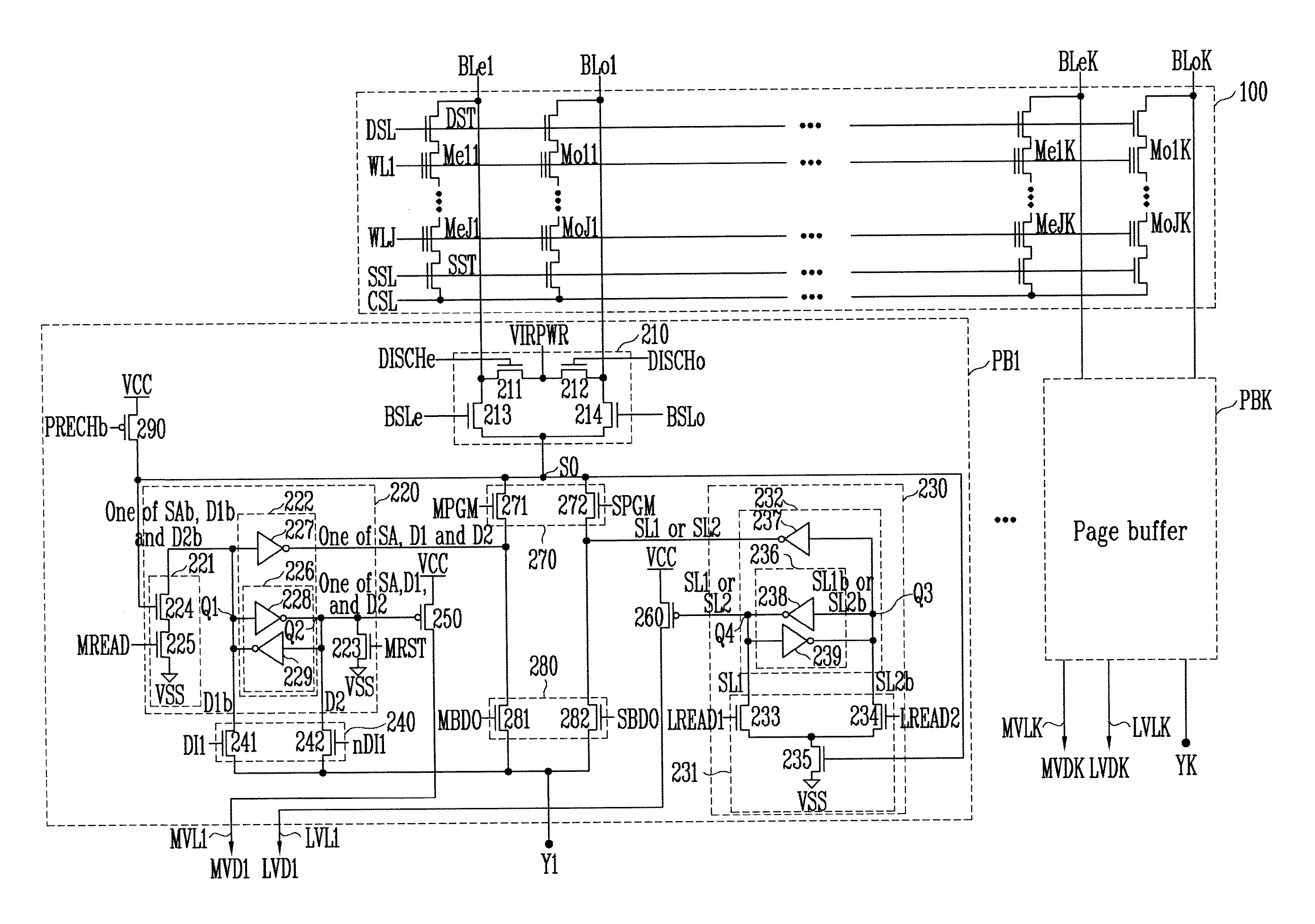

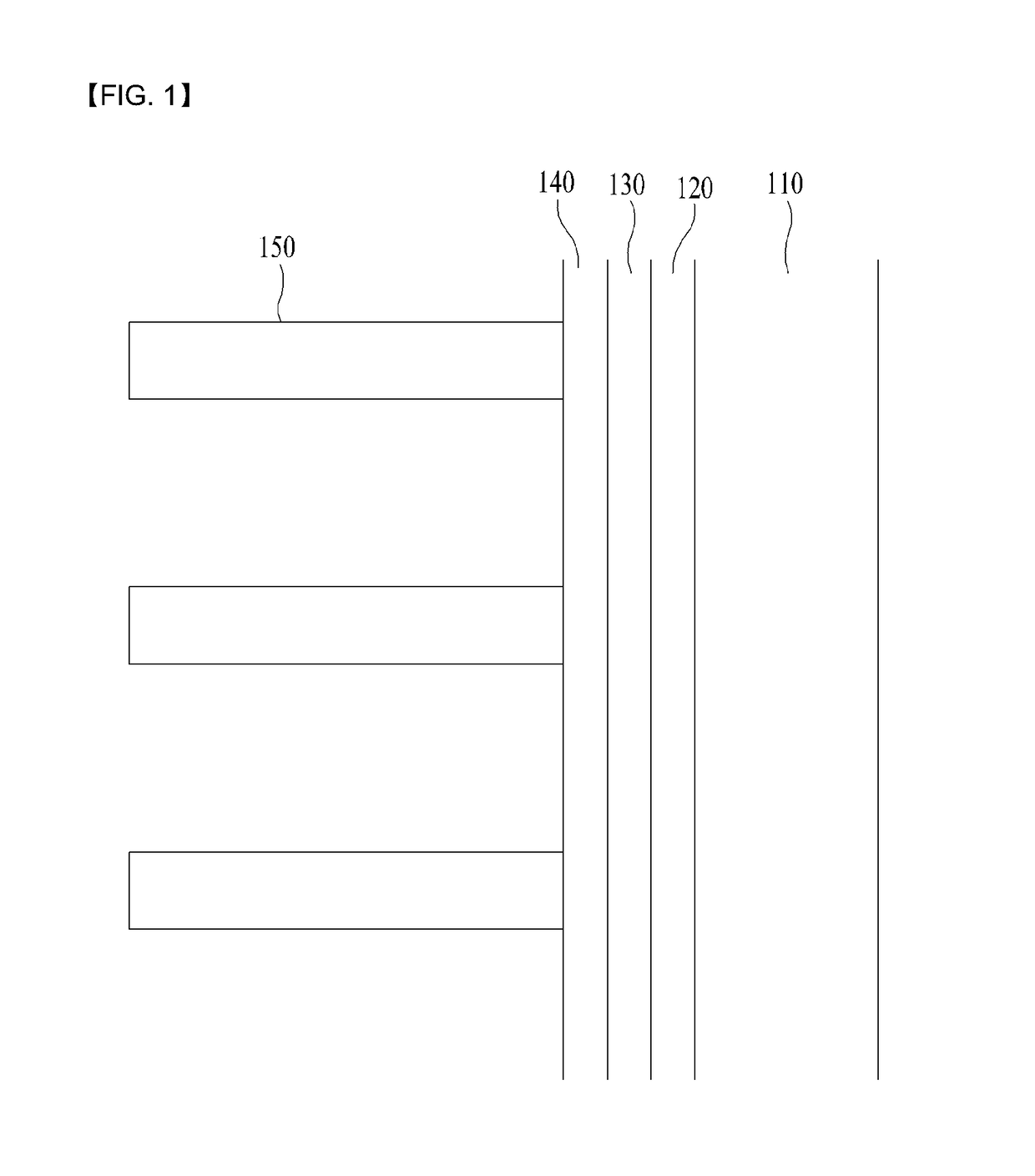

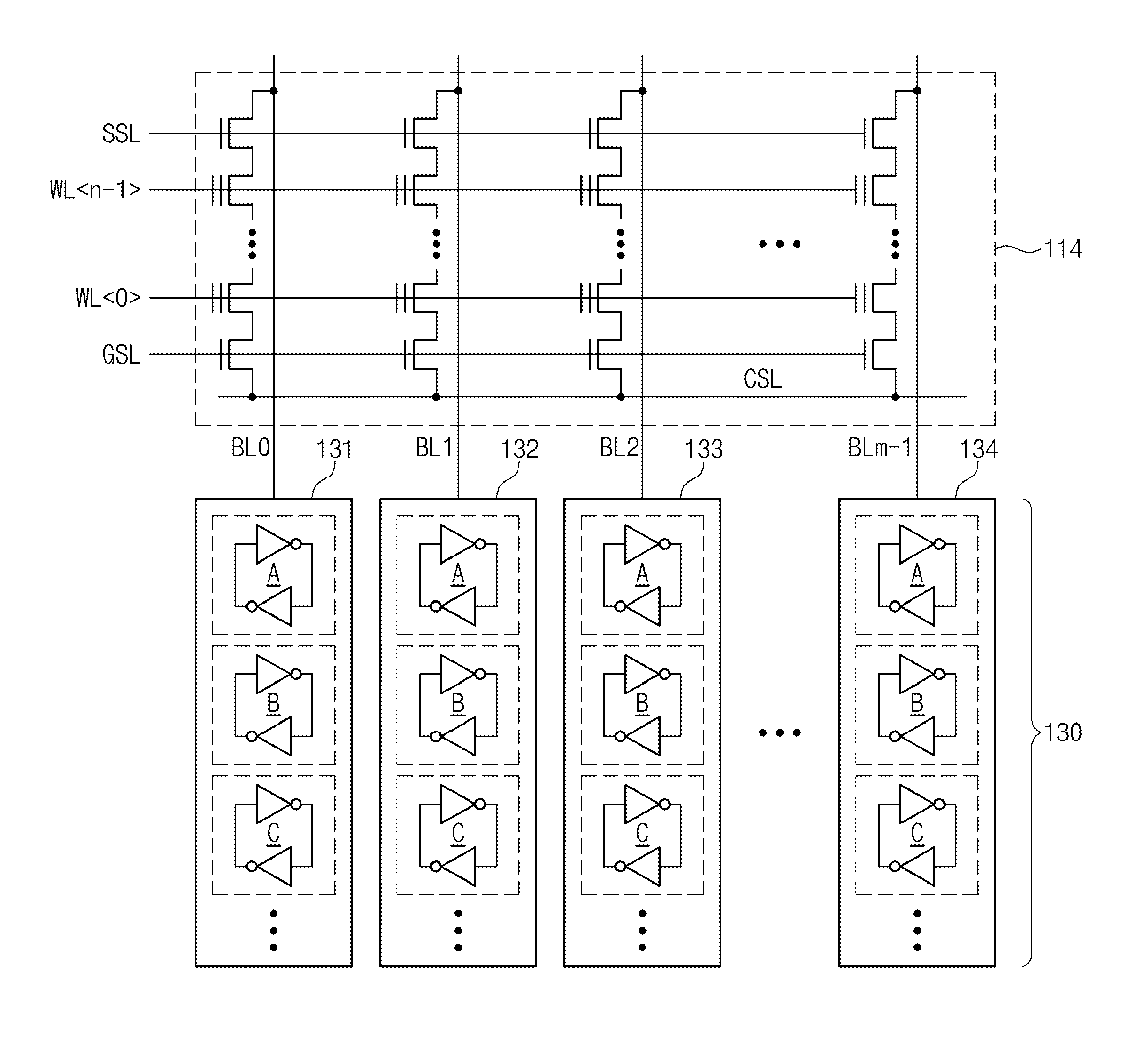

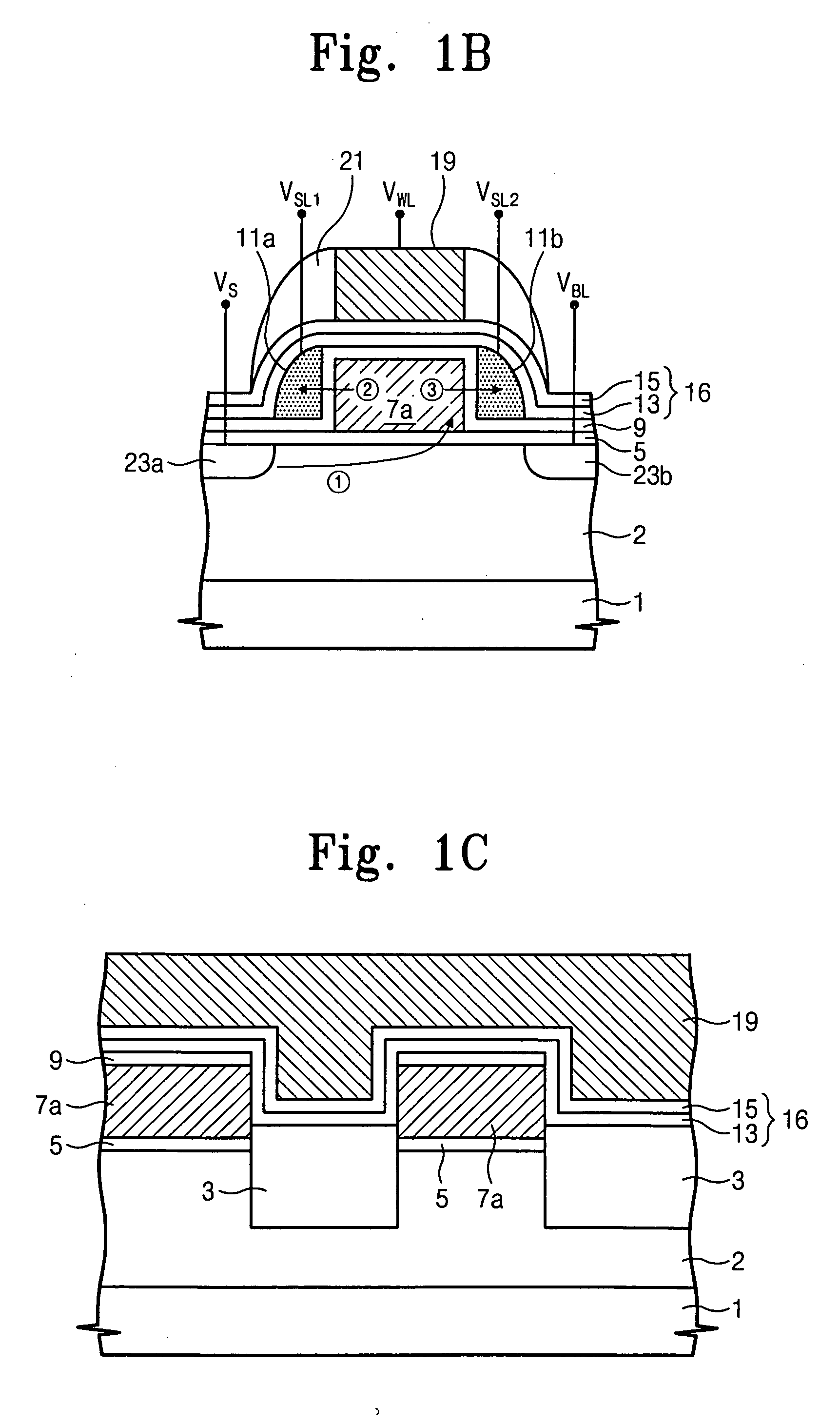

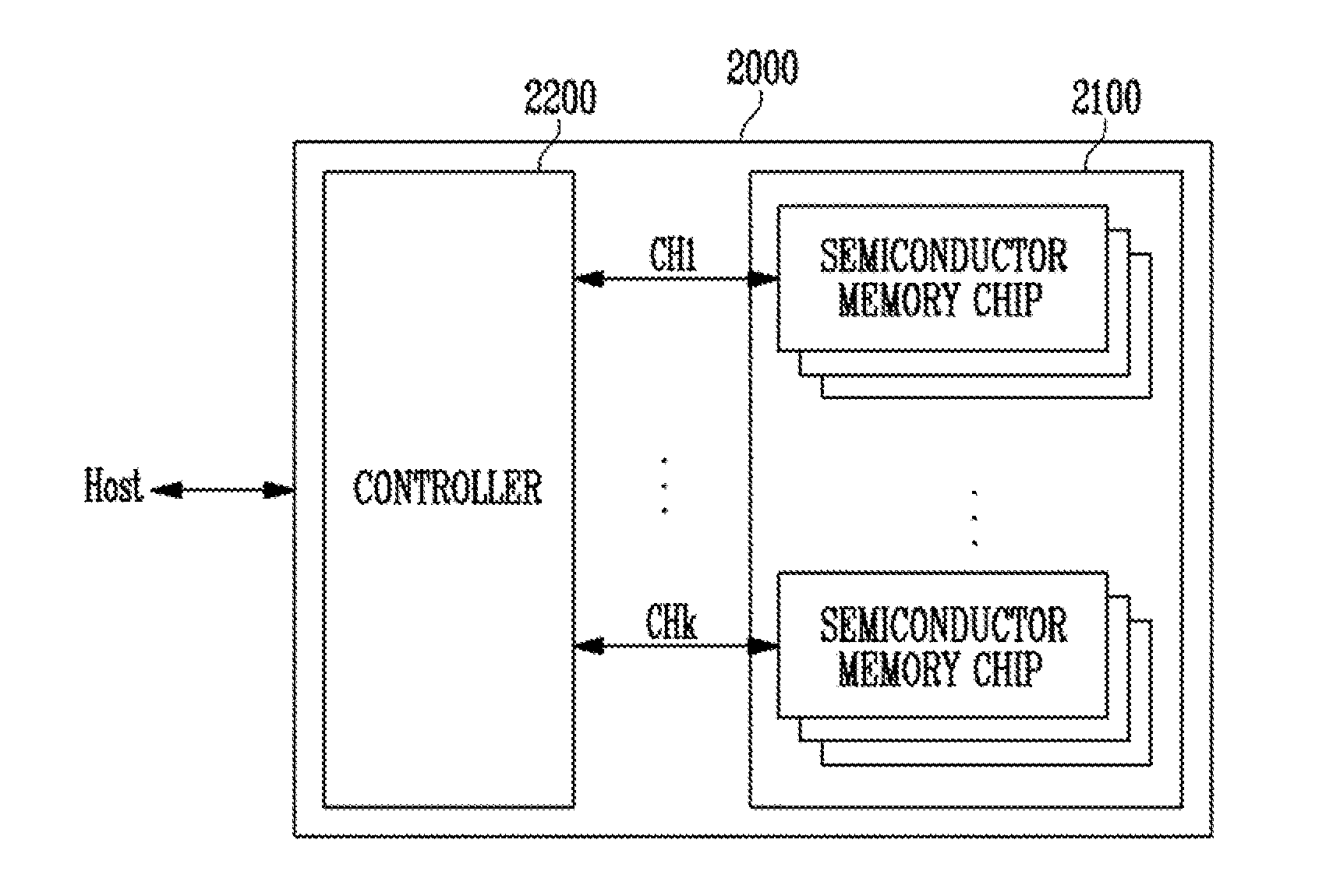

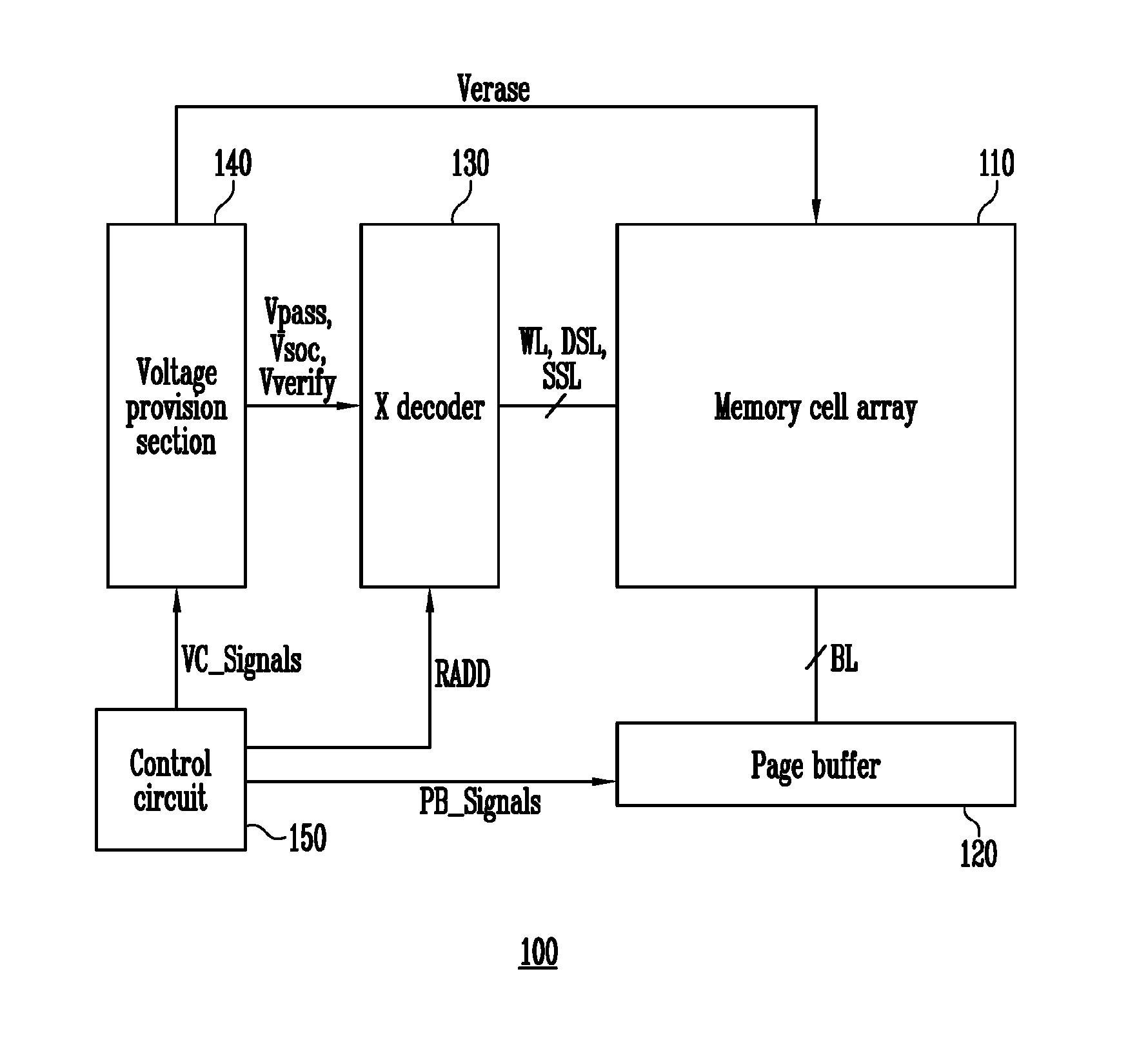

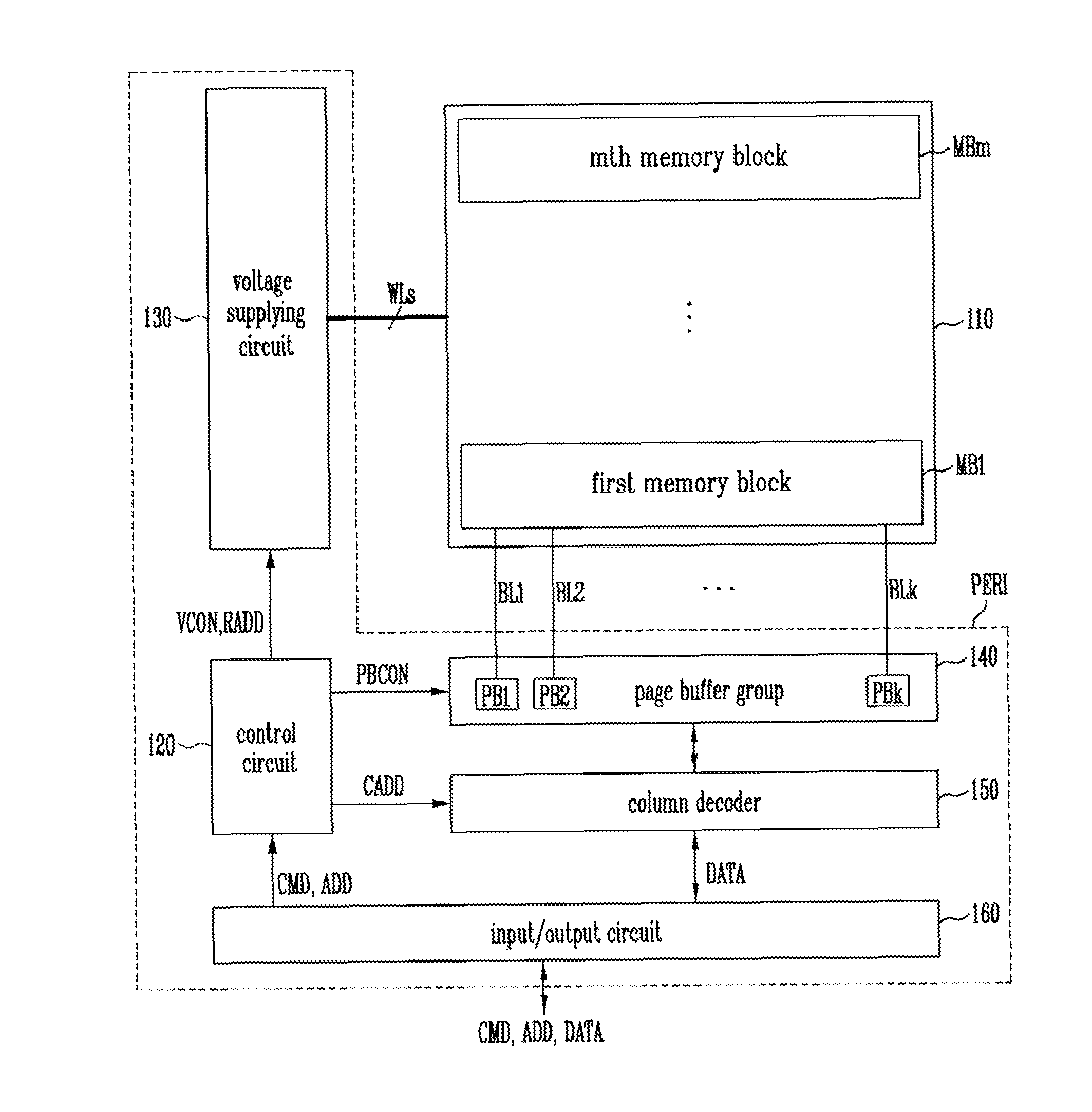

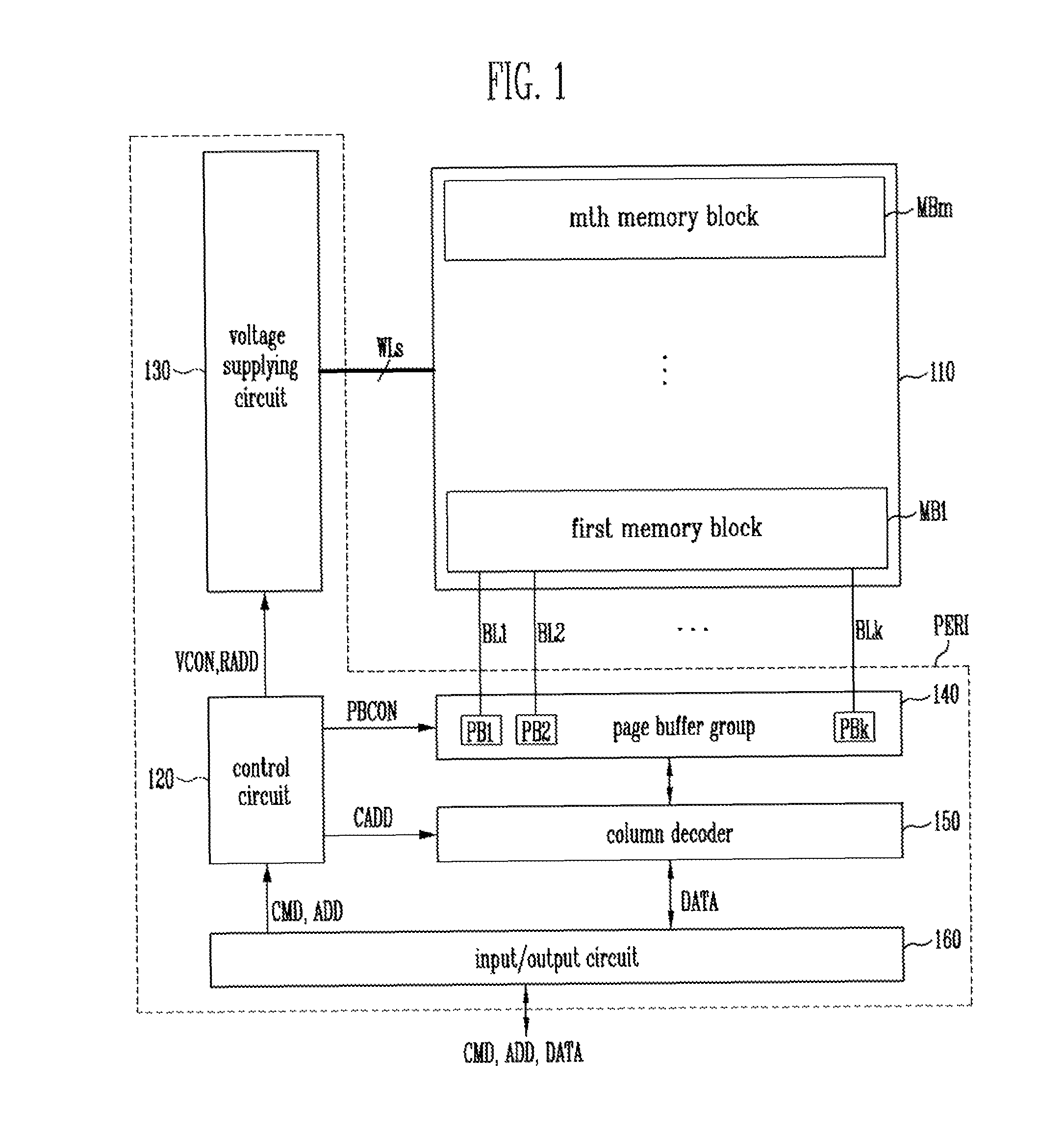

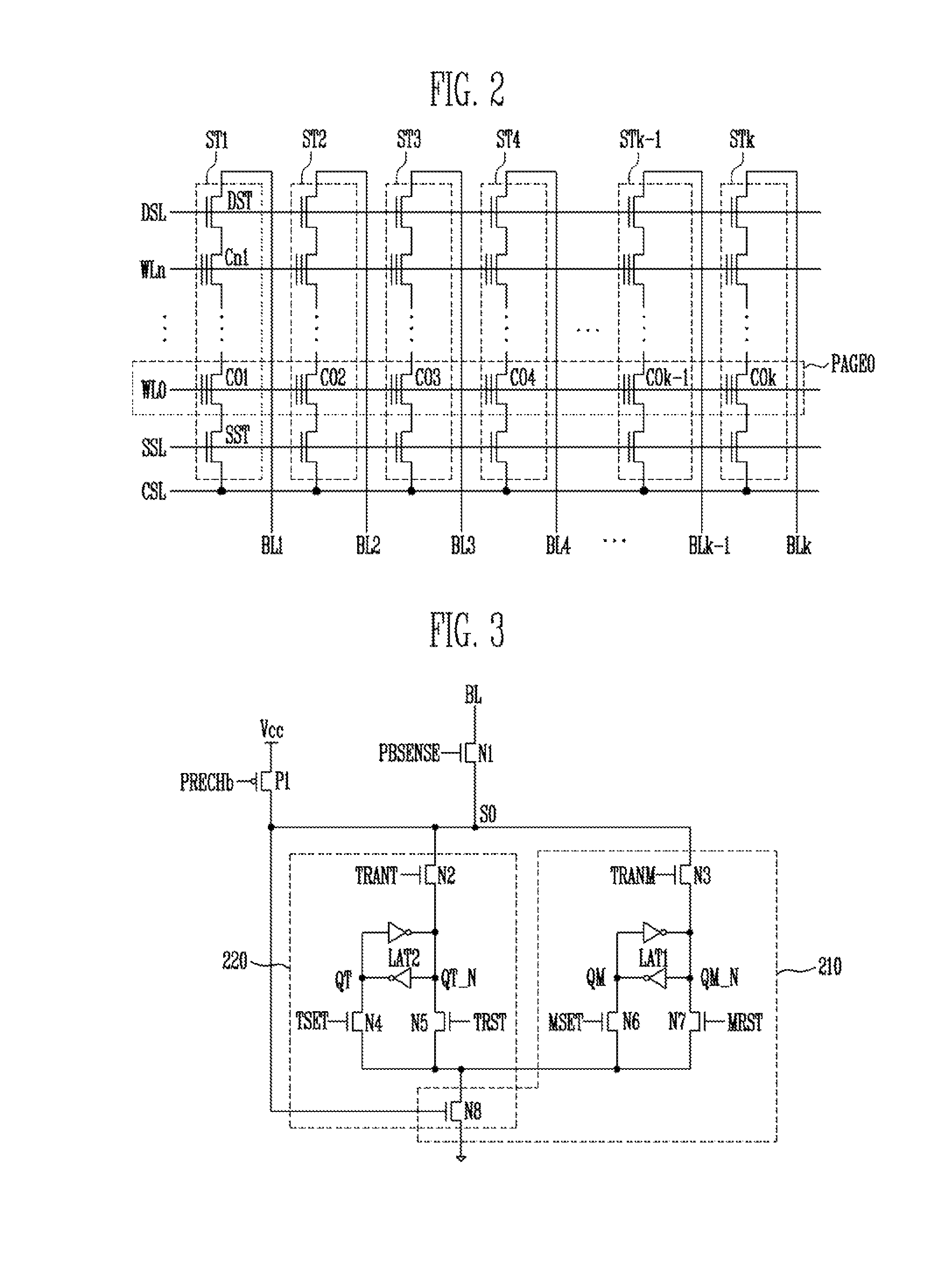

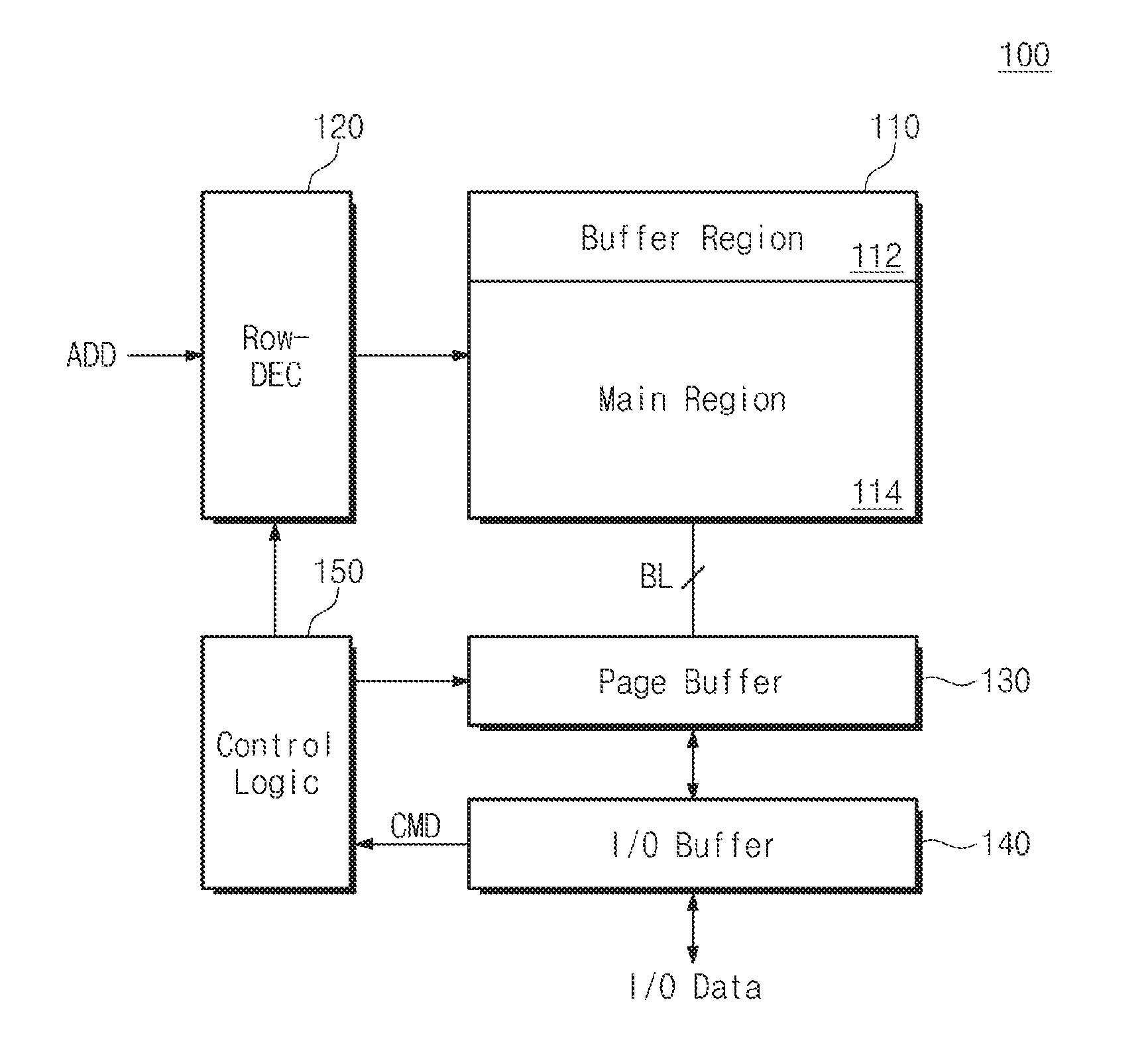

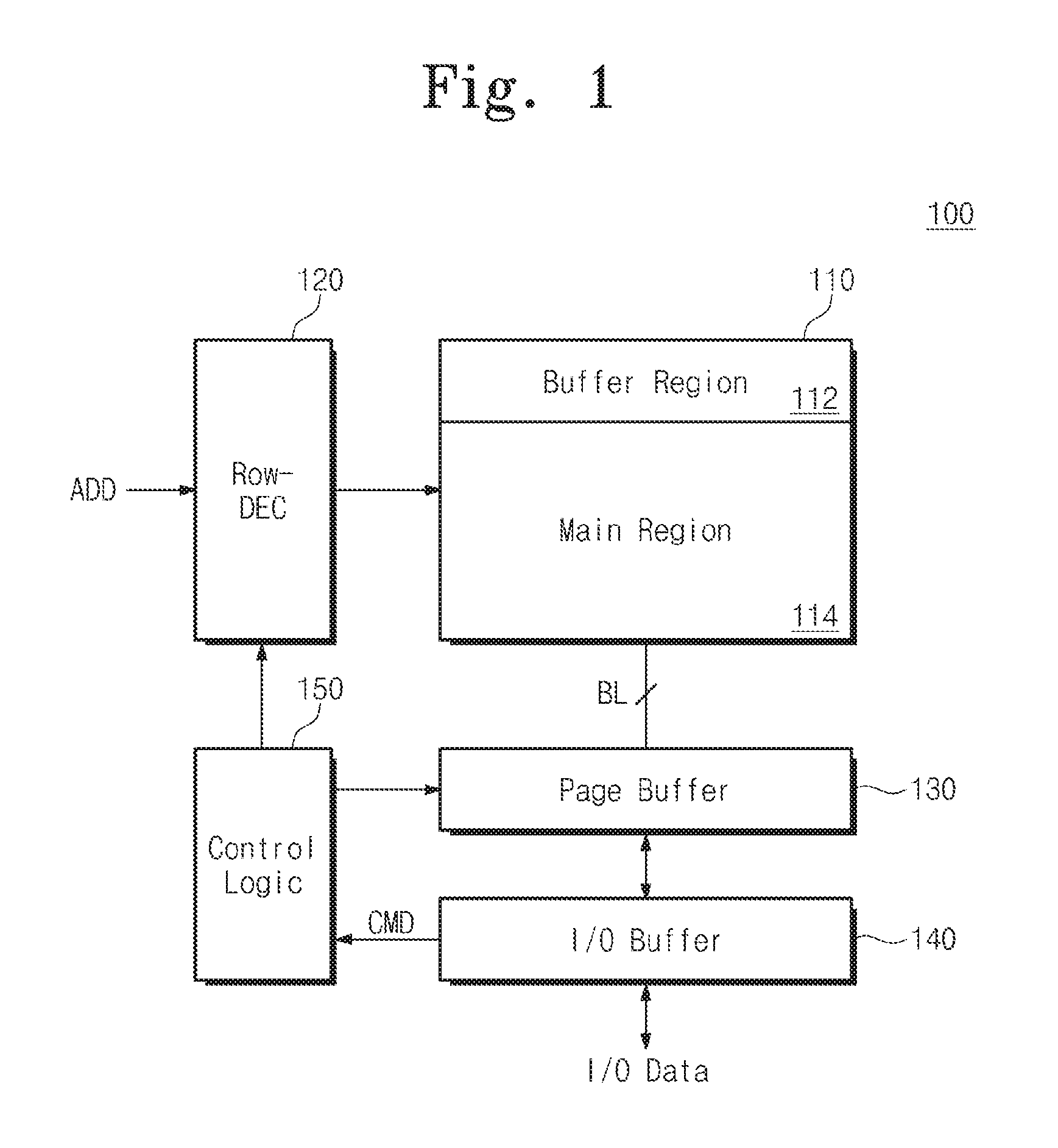

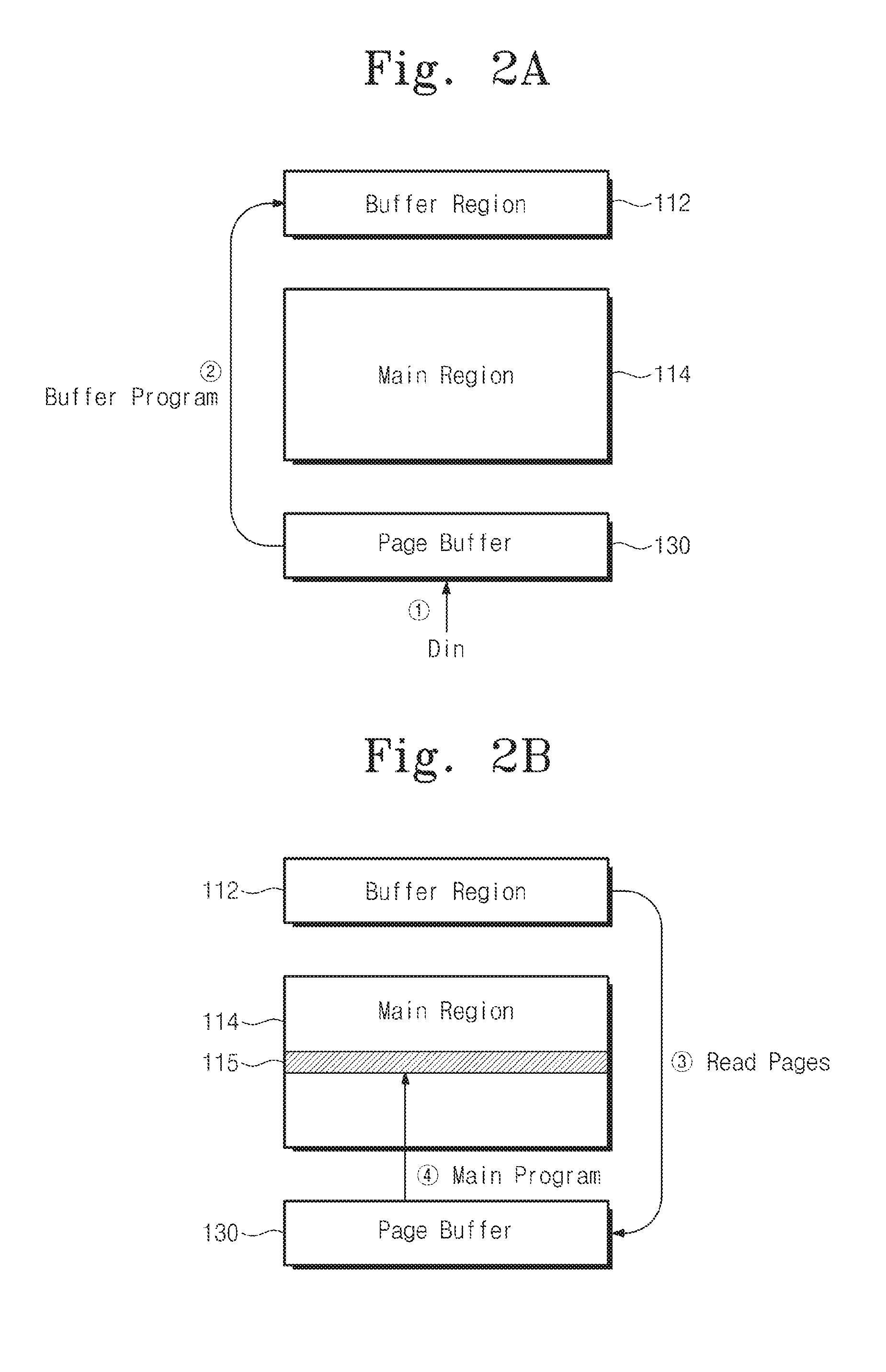

Nonvolatile memory and related reprogramming method

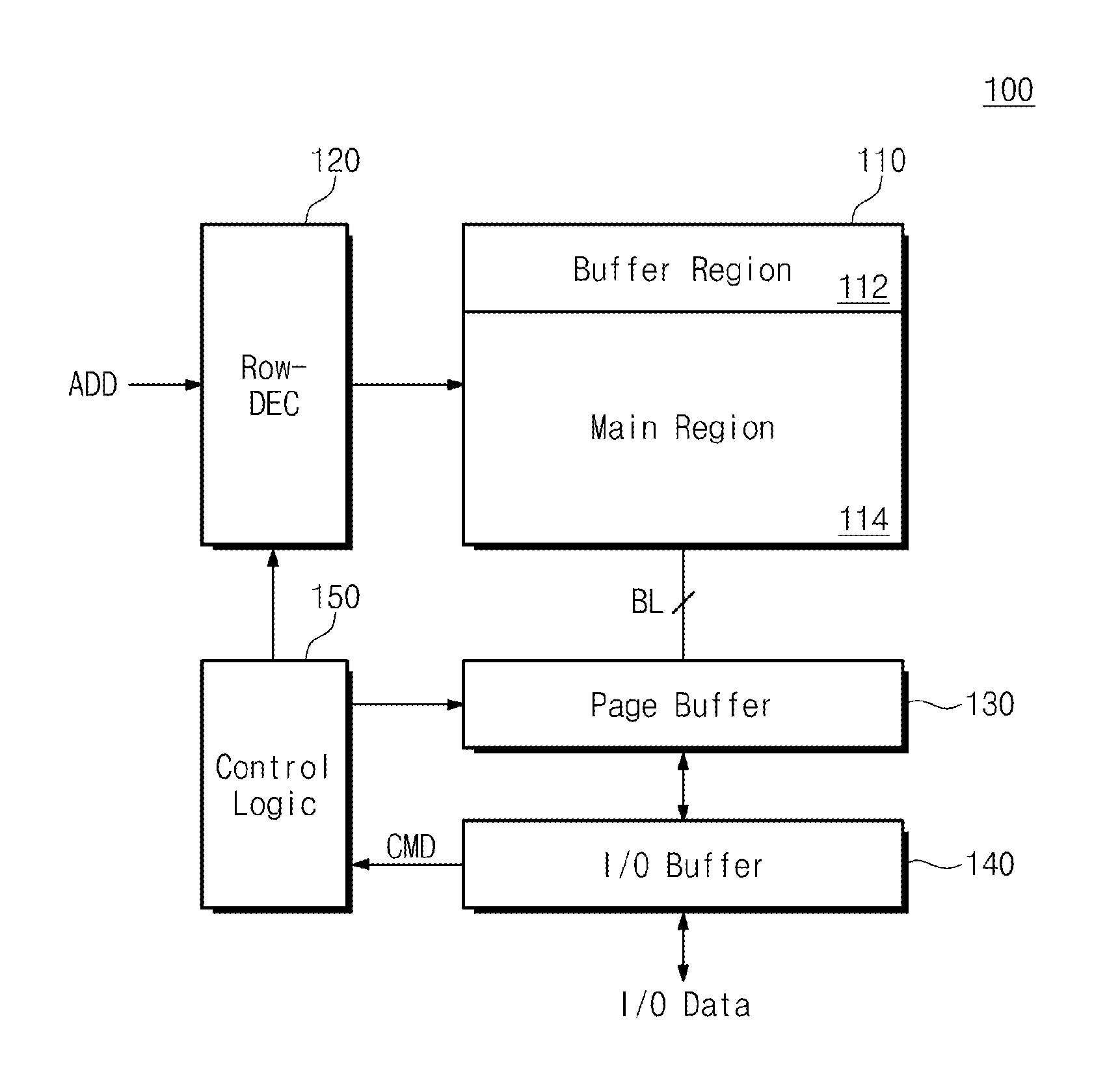

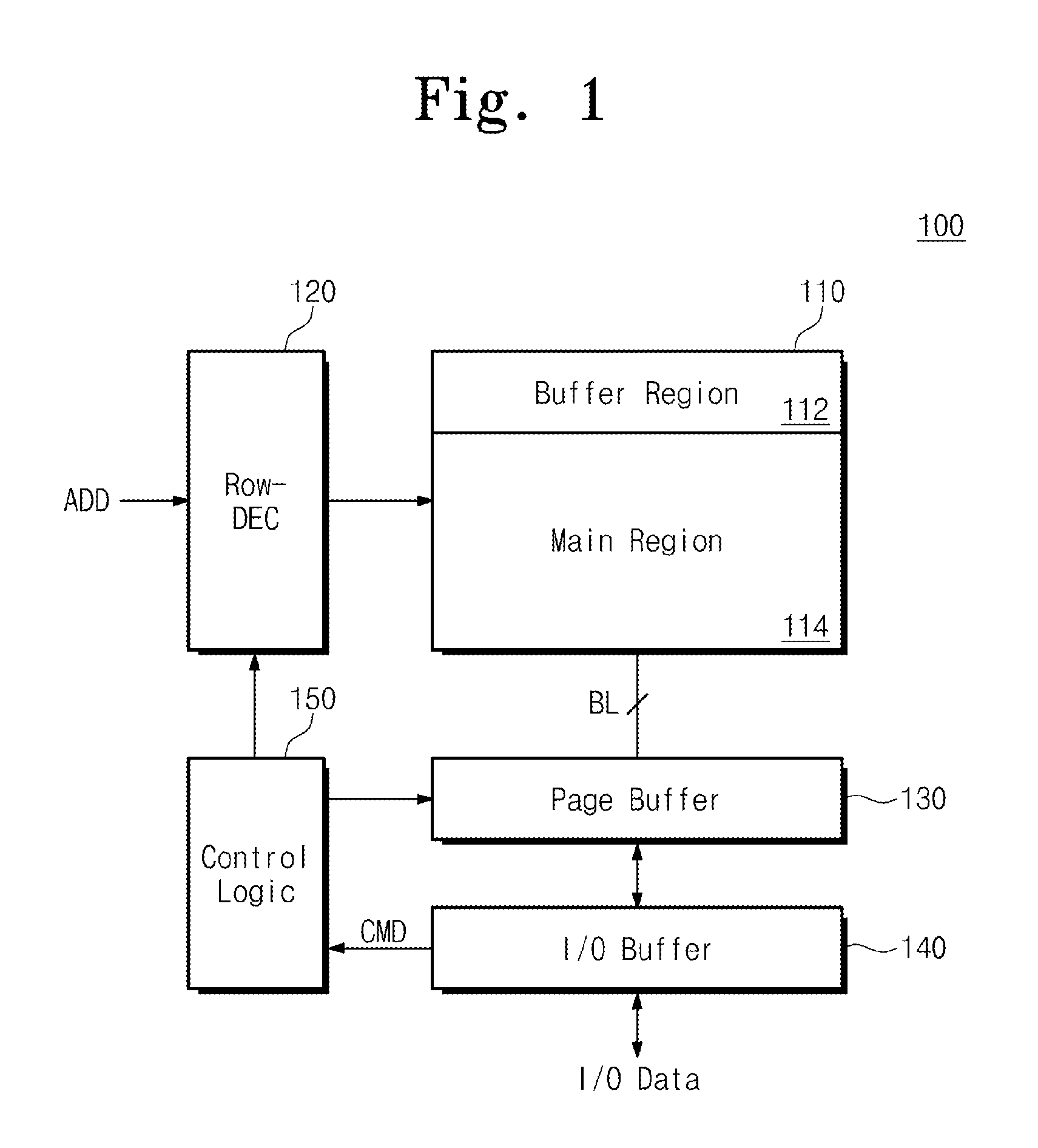

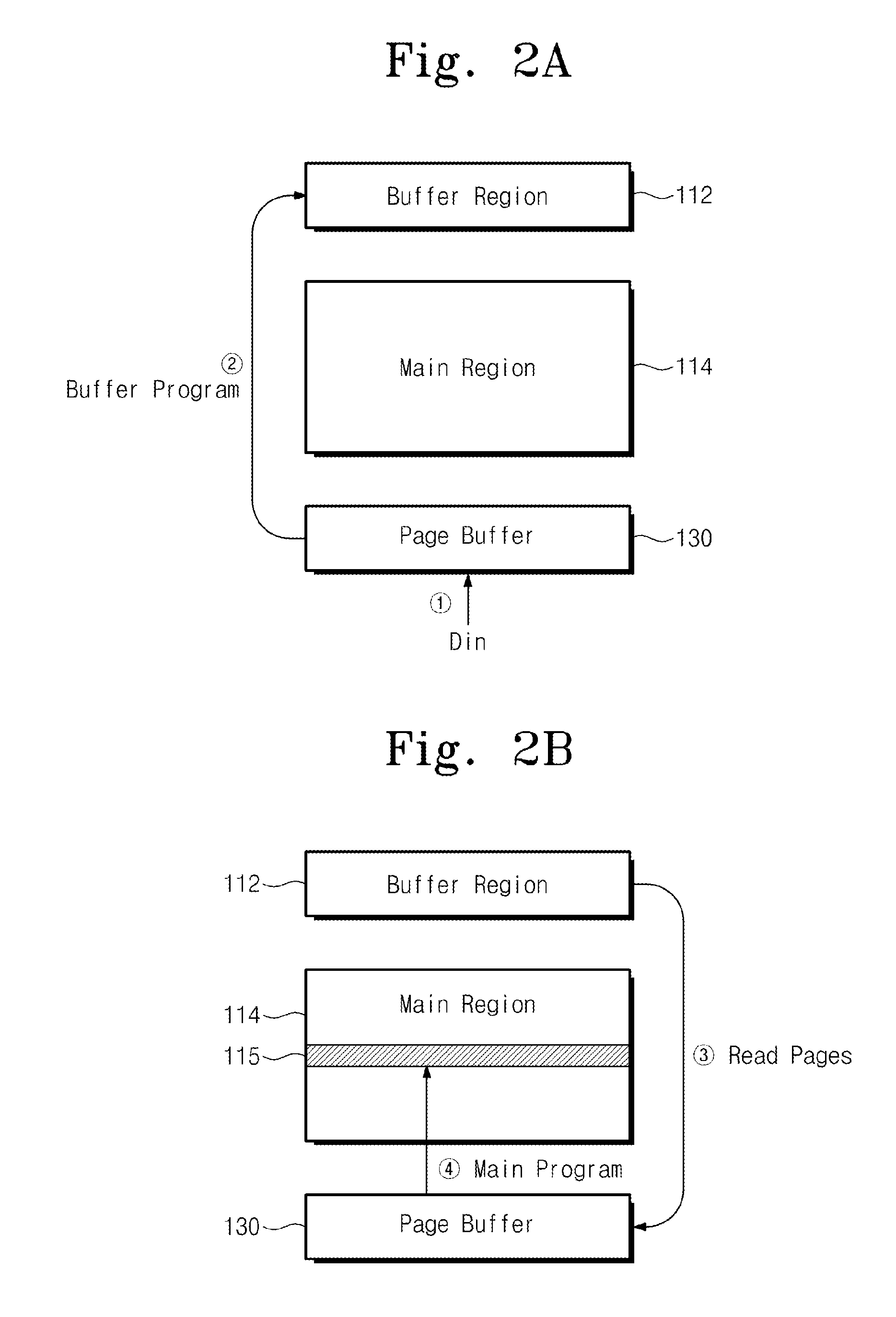

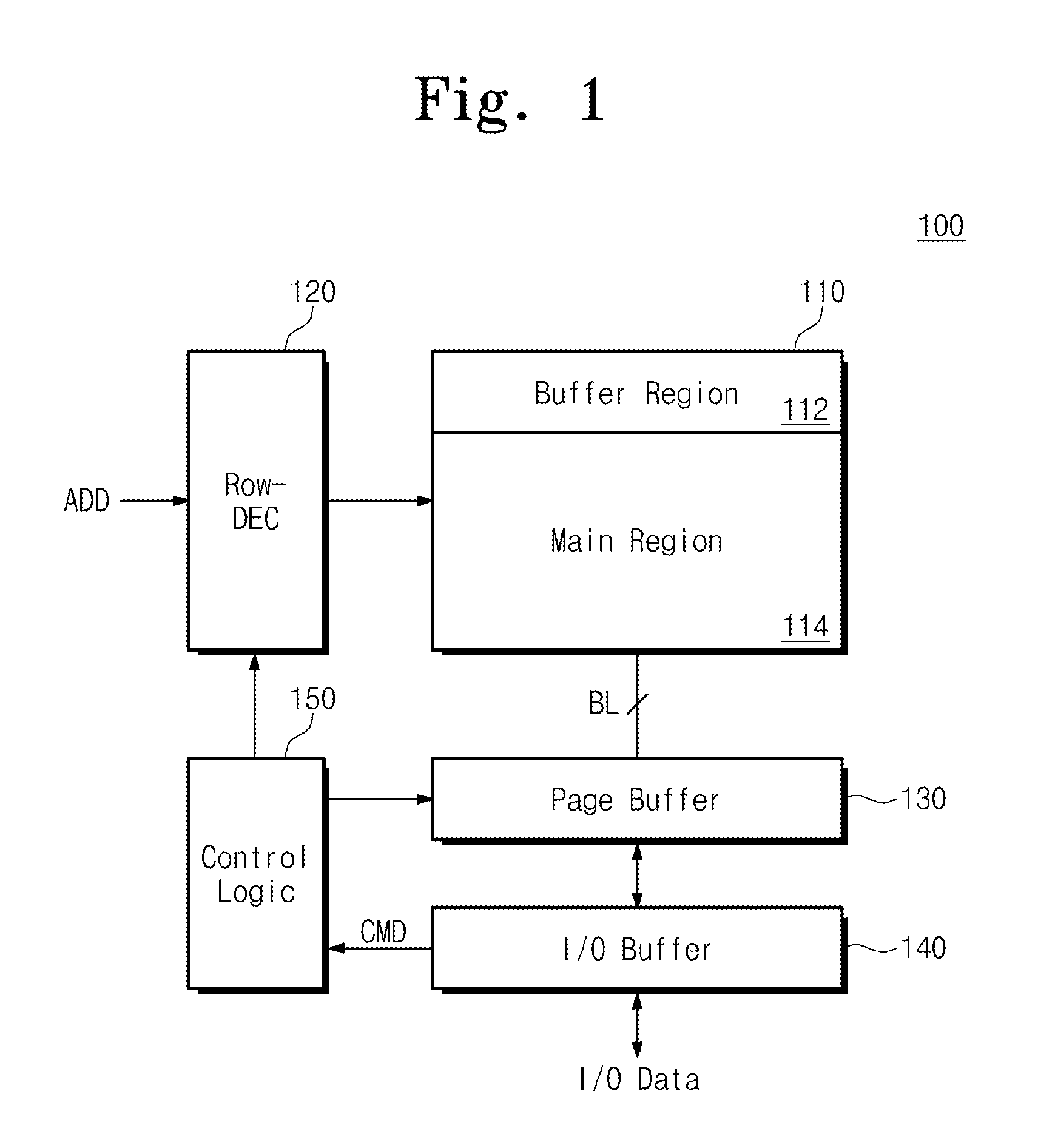

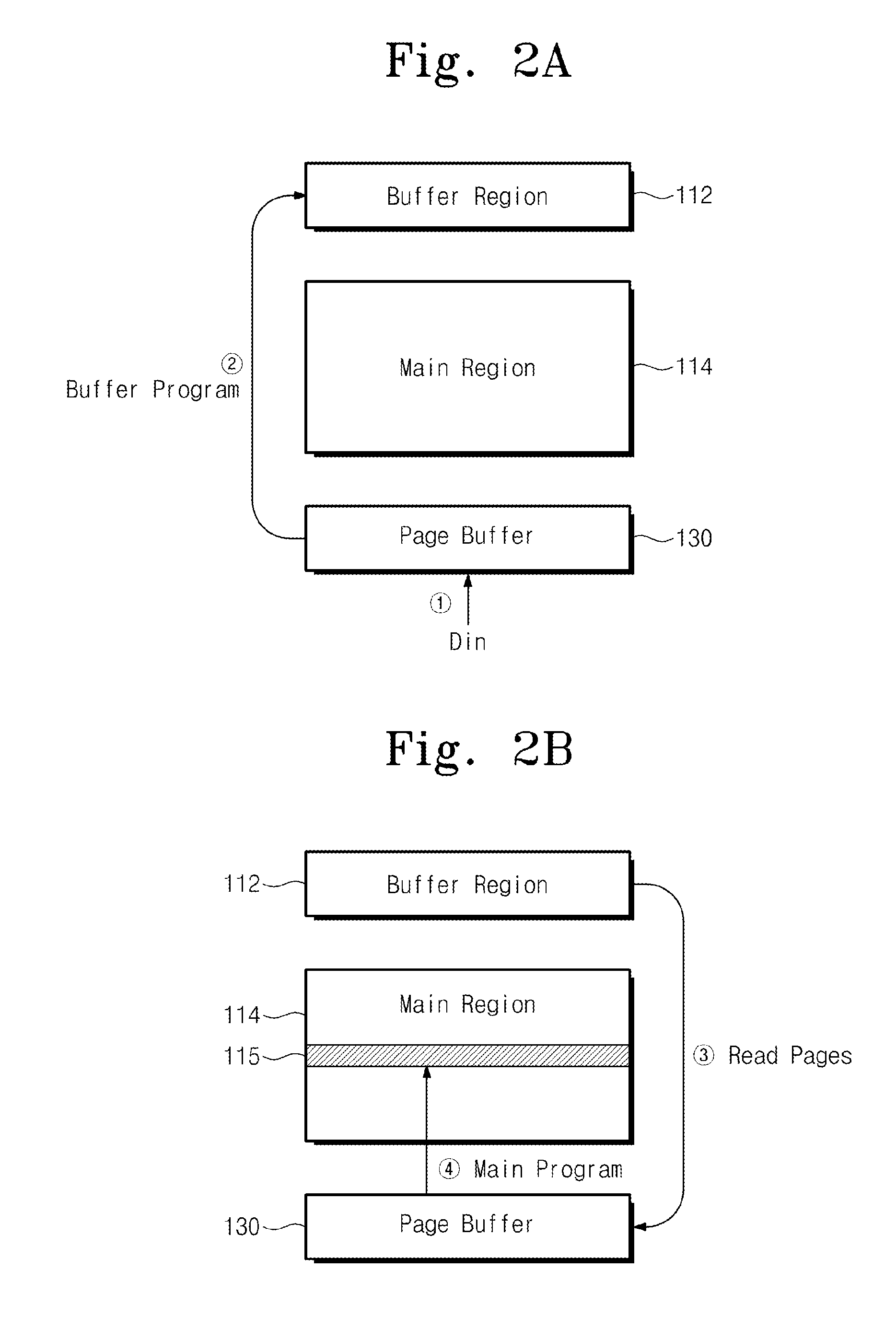

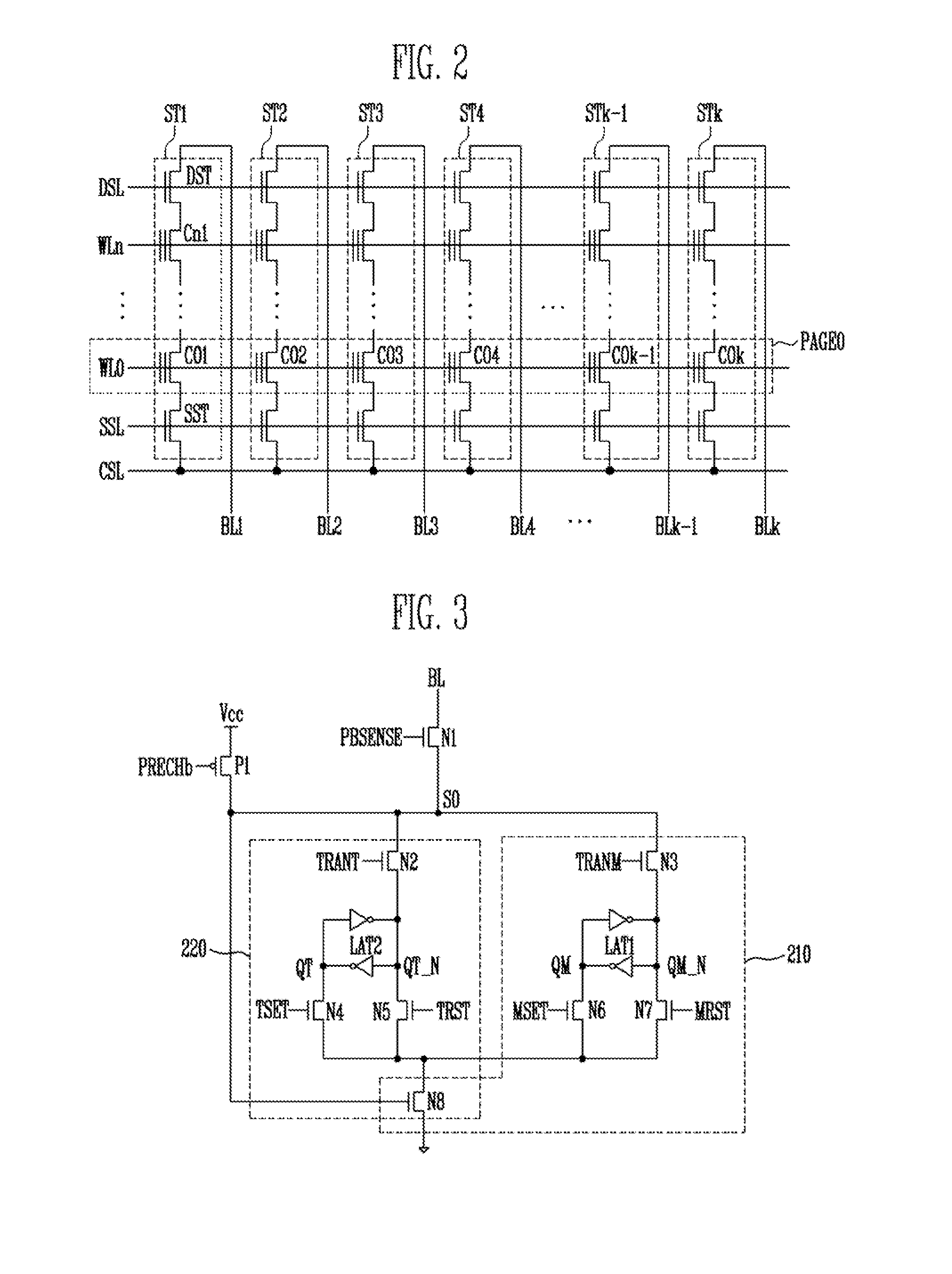

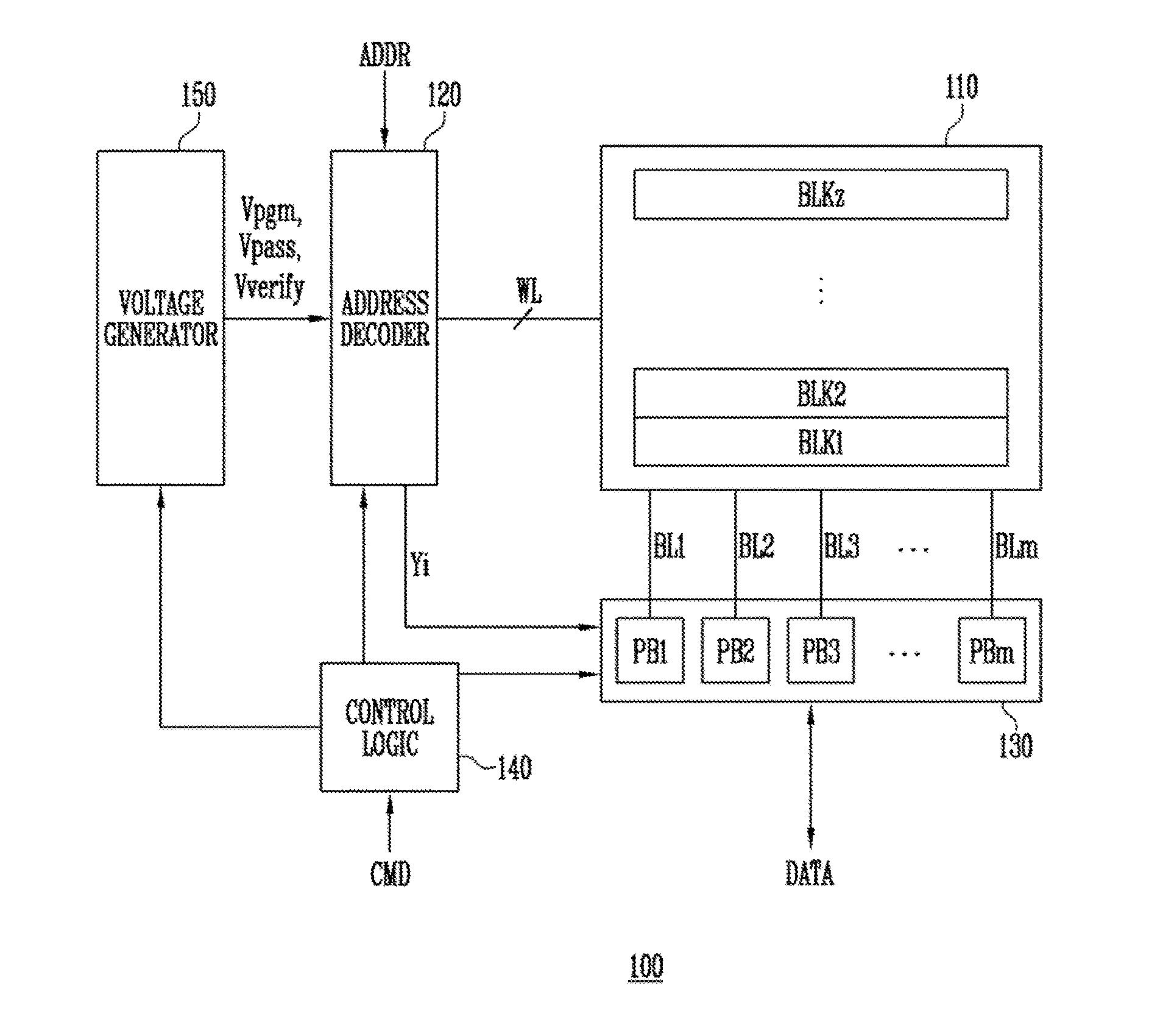

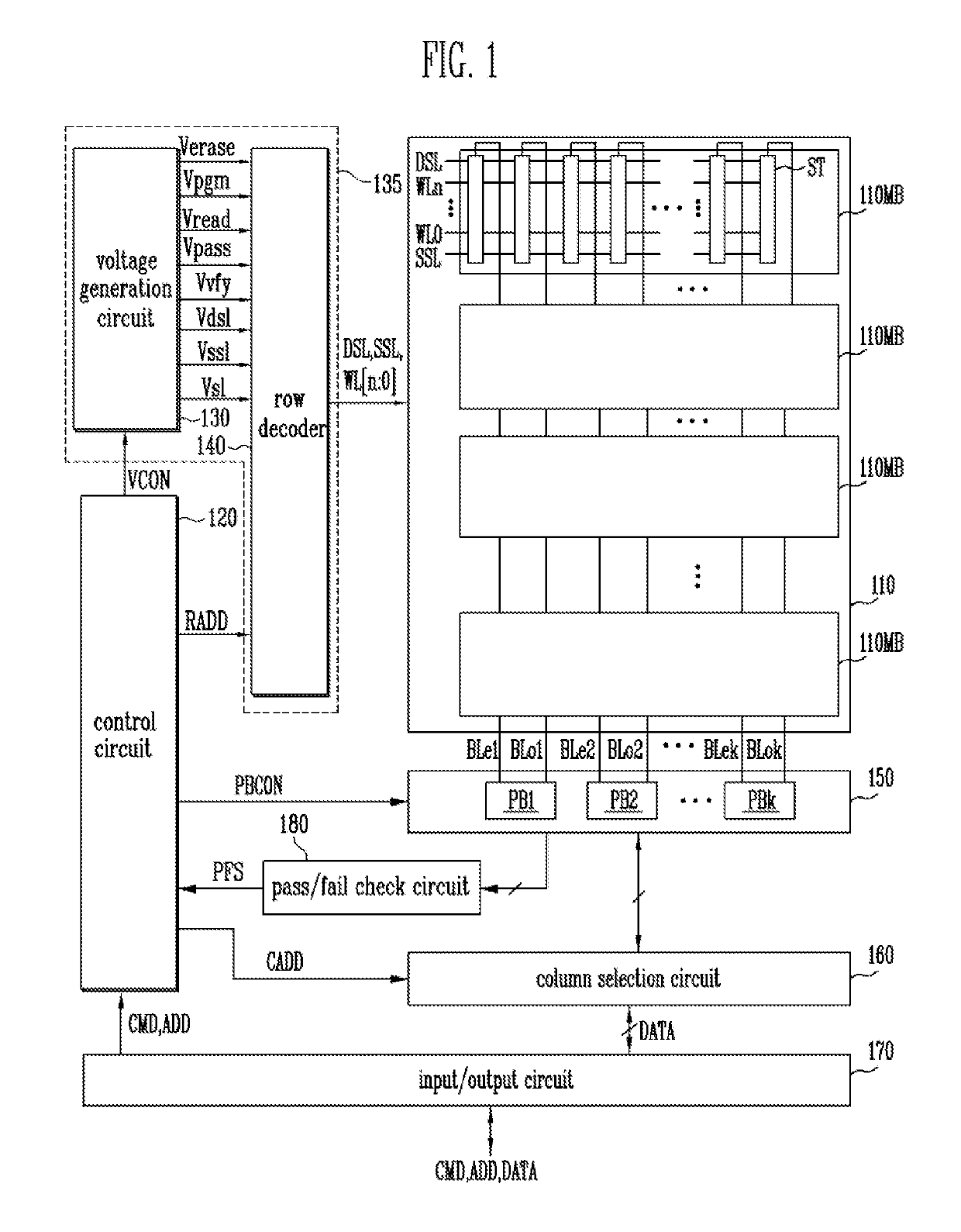

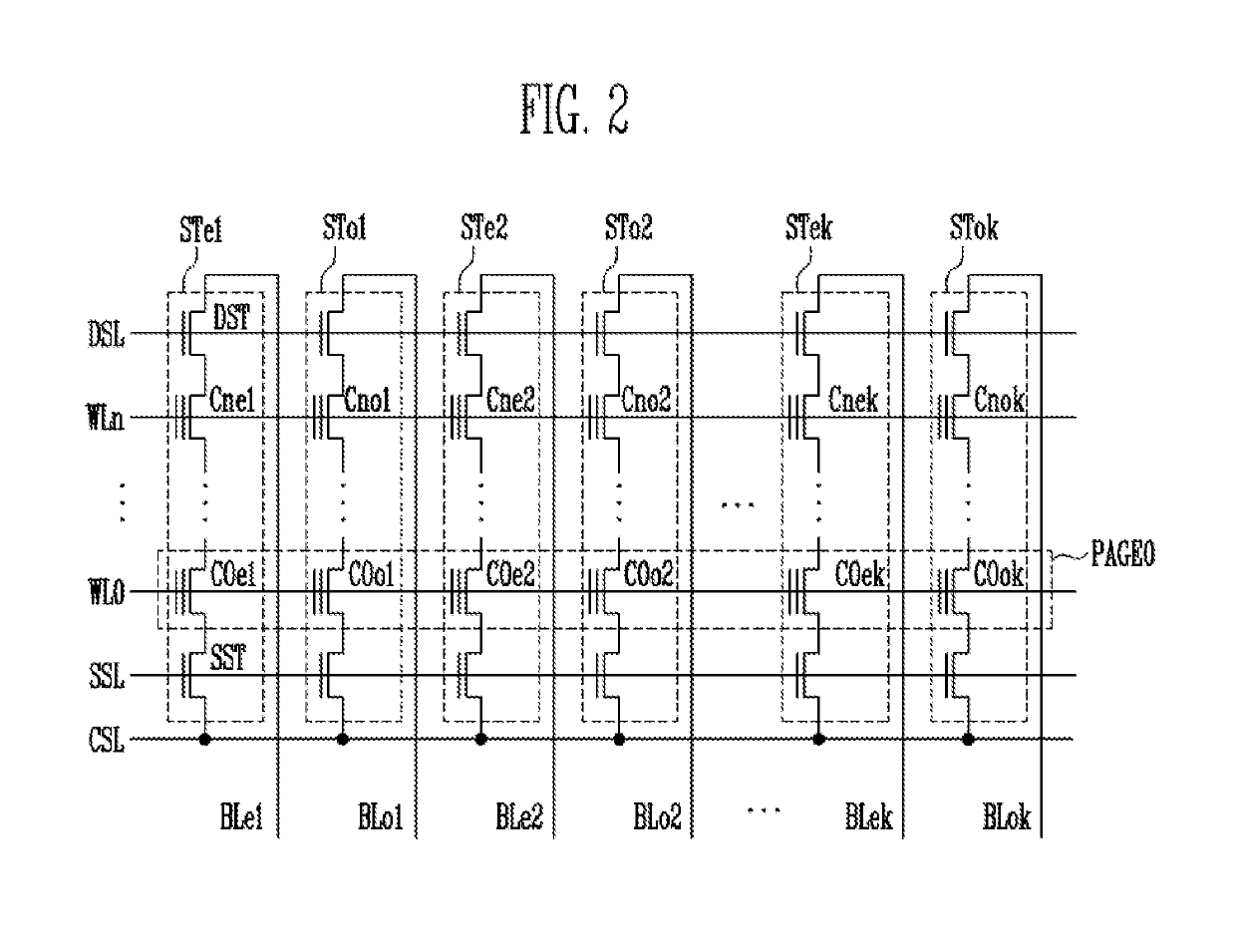

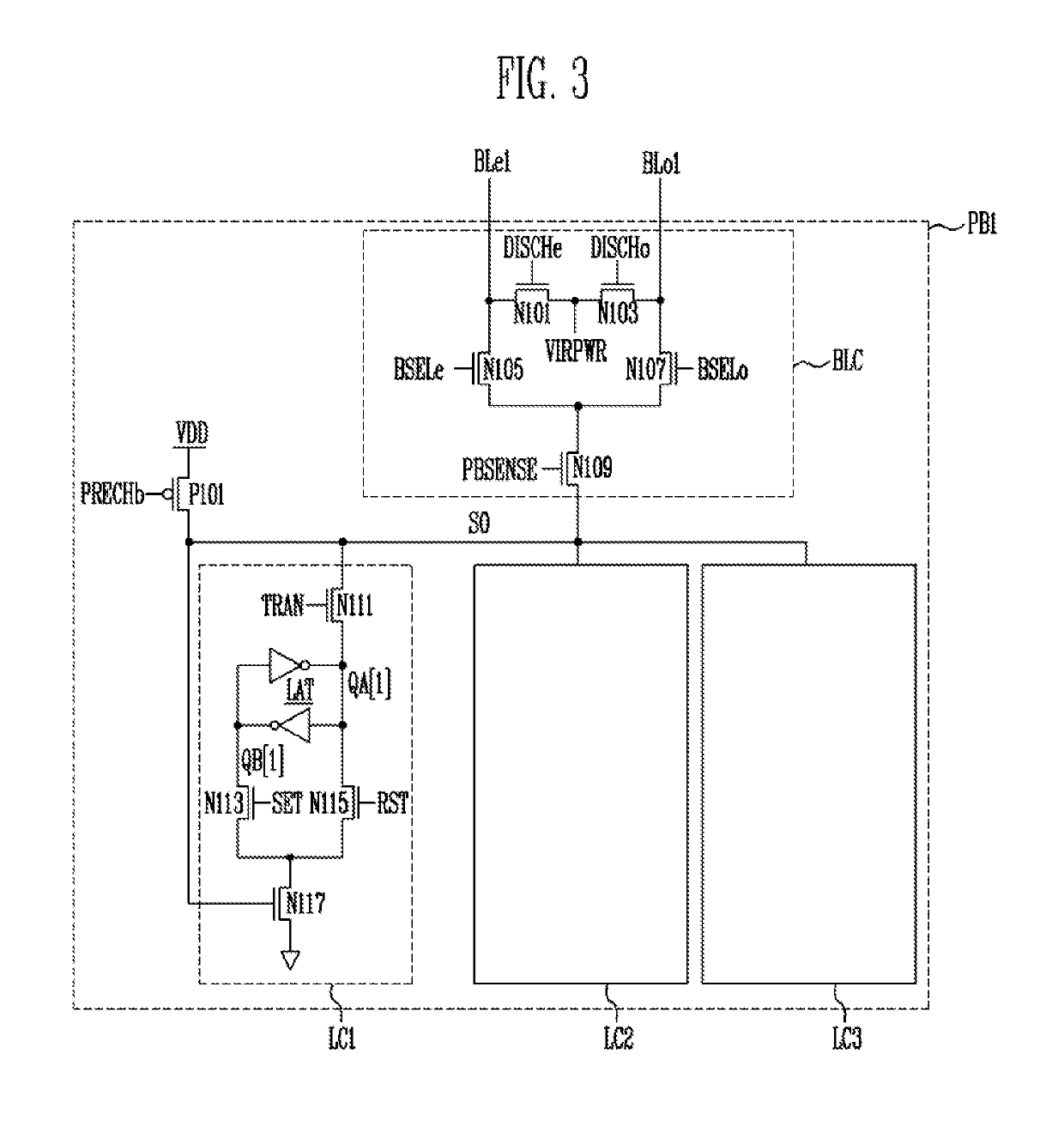

InactiveUS20140351487A1Improve programming speedImproved Threshold Voltage DistributionMemory architecture accessing/allocationRead-only memoriesOperating systemPage buffers

A method of reprogramming a nonvolatile memory device, comprising setting up bit lines of selected memory cells according to logic values of first and second latches of a page buffer connected to the bit lines, supplying a program pulse to the selected memory cells, performing a program verify operation on the selected memory cells using the first and second latches, and performing a predictive program operation on the selected memory cells according to a result of the program verify operation. In the predictive program operation, bit lines of the selected memory cells are setup according to a logic value of a third latch of the page buffer that corresponds to each of the selected memory cells.

Owner:SAMSUNG ELECTRONICS CO LTD

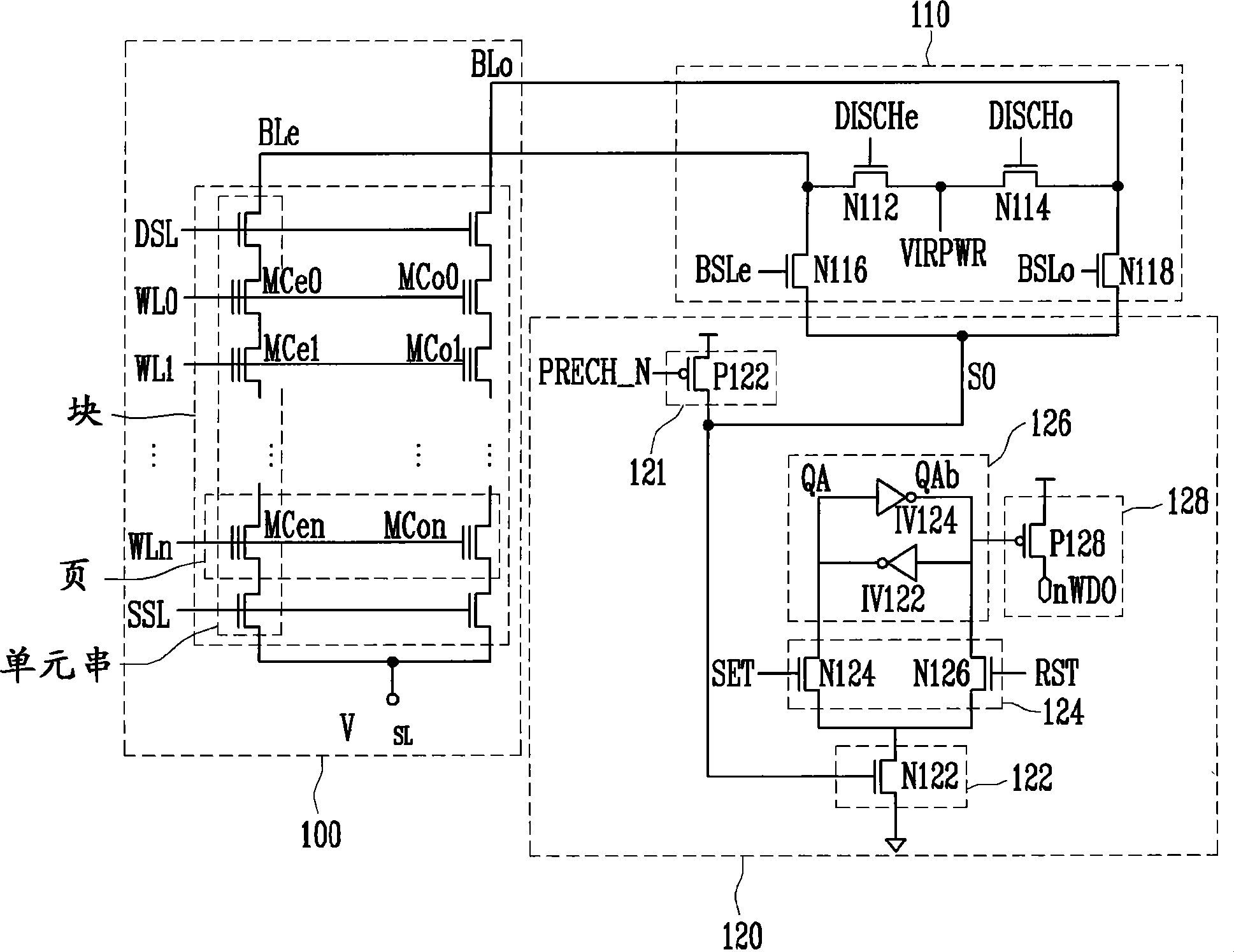

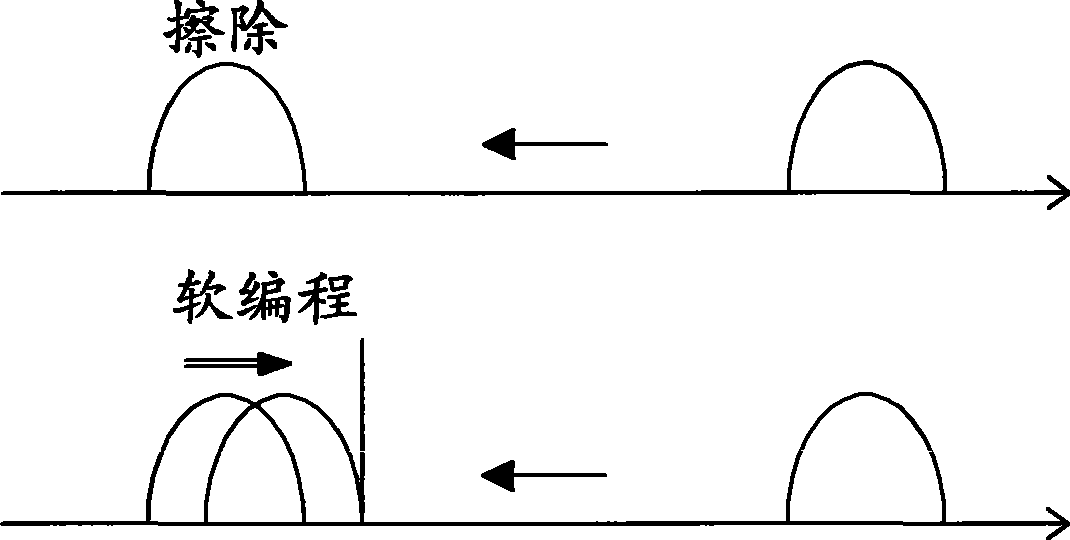

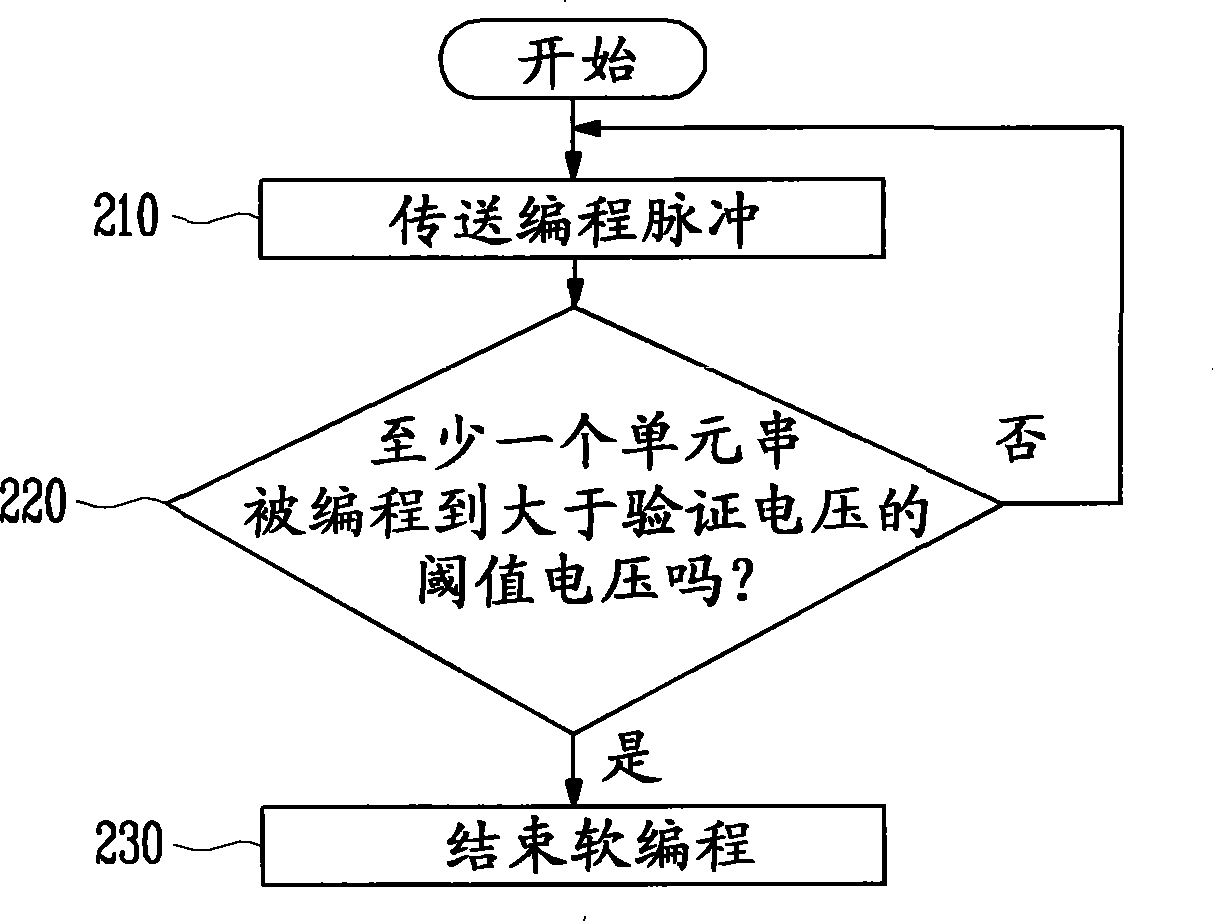

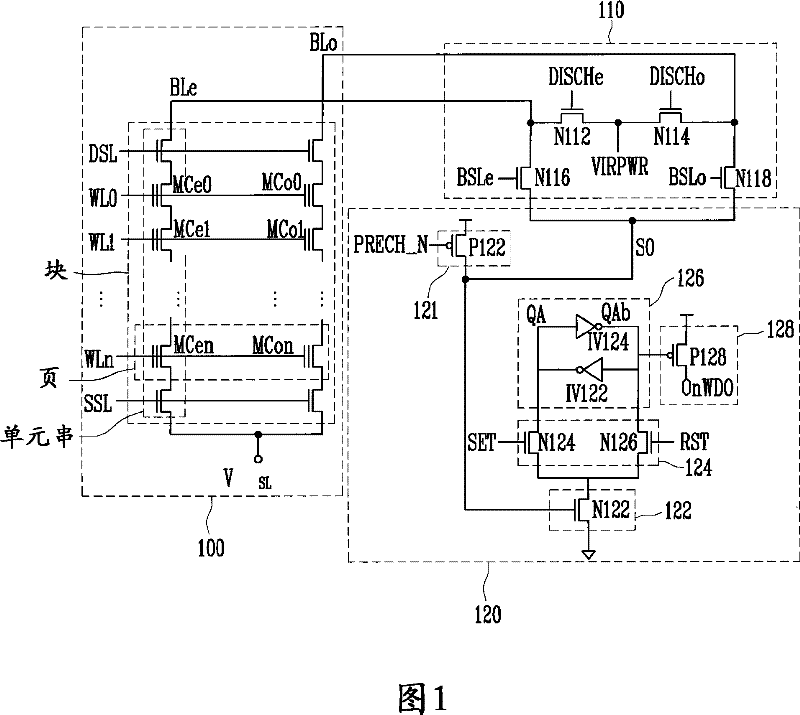

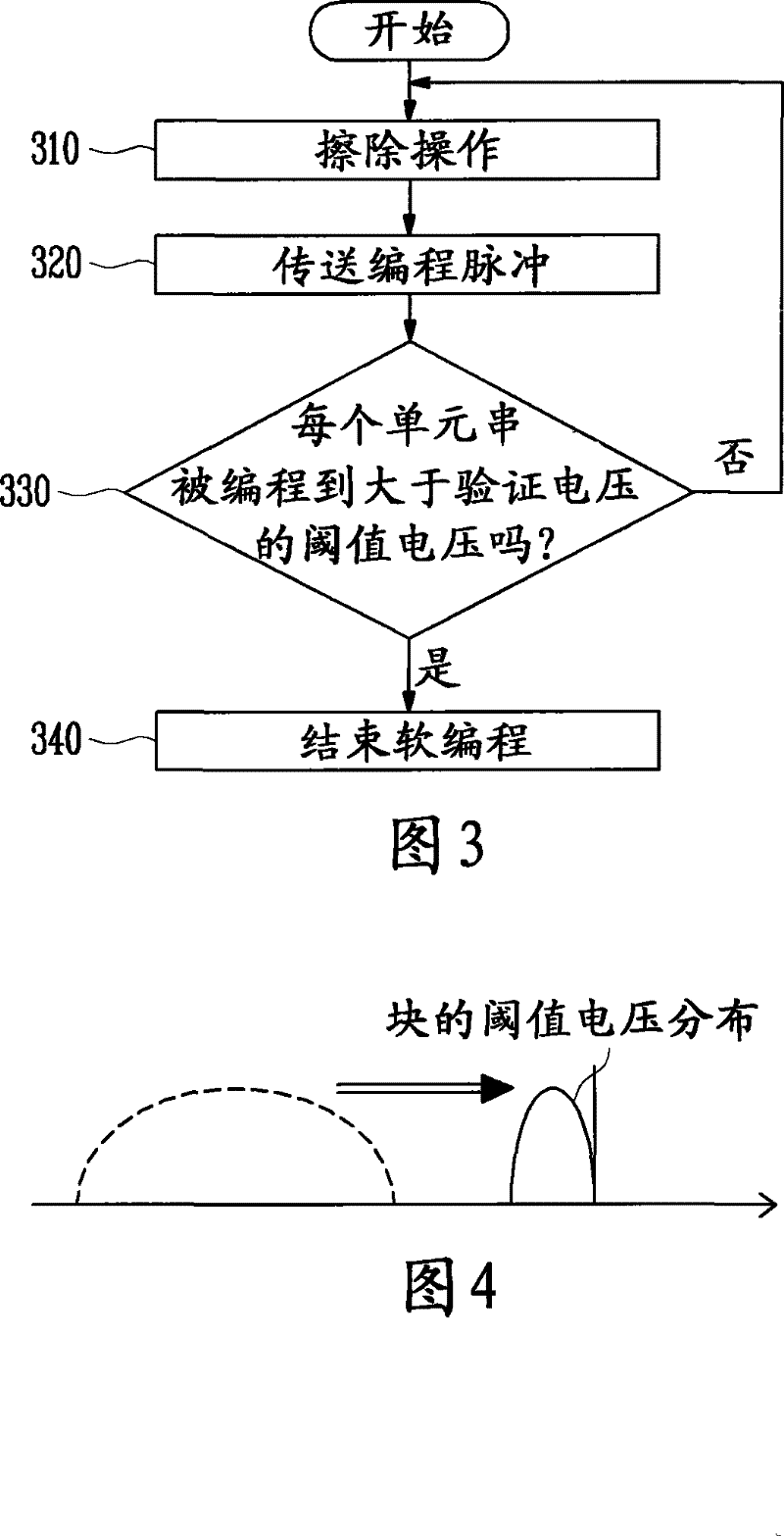

Soft program method in a non-volatile memory device

InactiveCN101364443AImproved Threshold Voltage DistributionImprove read marginRead-only memoriesStorage cellThreshold voltage

A soft program method in a non-volatile memory device for performing a soft program step so as to improve threshold voltage distribution of an erased cell is disclosed. The soft program method in a non-volatile memory device includes performing a soft program for increasing threshold voltages of memory cells by a given level, wherein an erase operation is performed about the memory cells, performing a verifying operation for verifying whether or not a cell programmed to a voltage more than a verifying voltage is existed in each of cell strings, and performing repeatedly the soft program until it is verified that whole cell strings have one or more cell programmed to the voltage more than the verifying voltage.

Owner:SK HYNIX INC

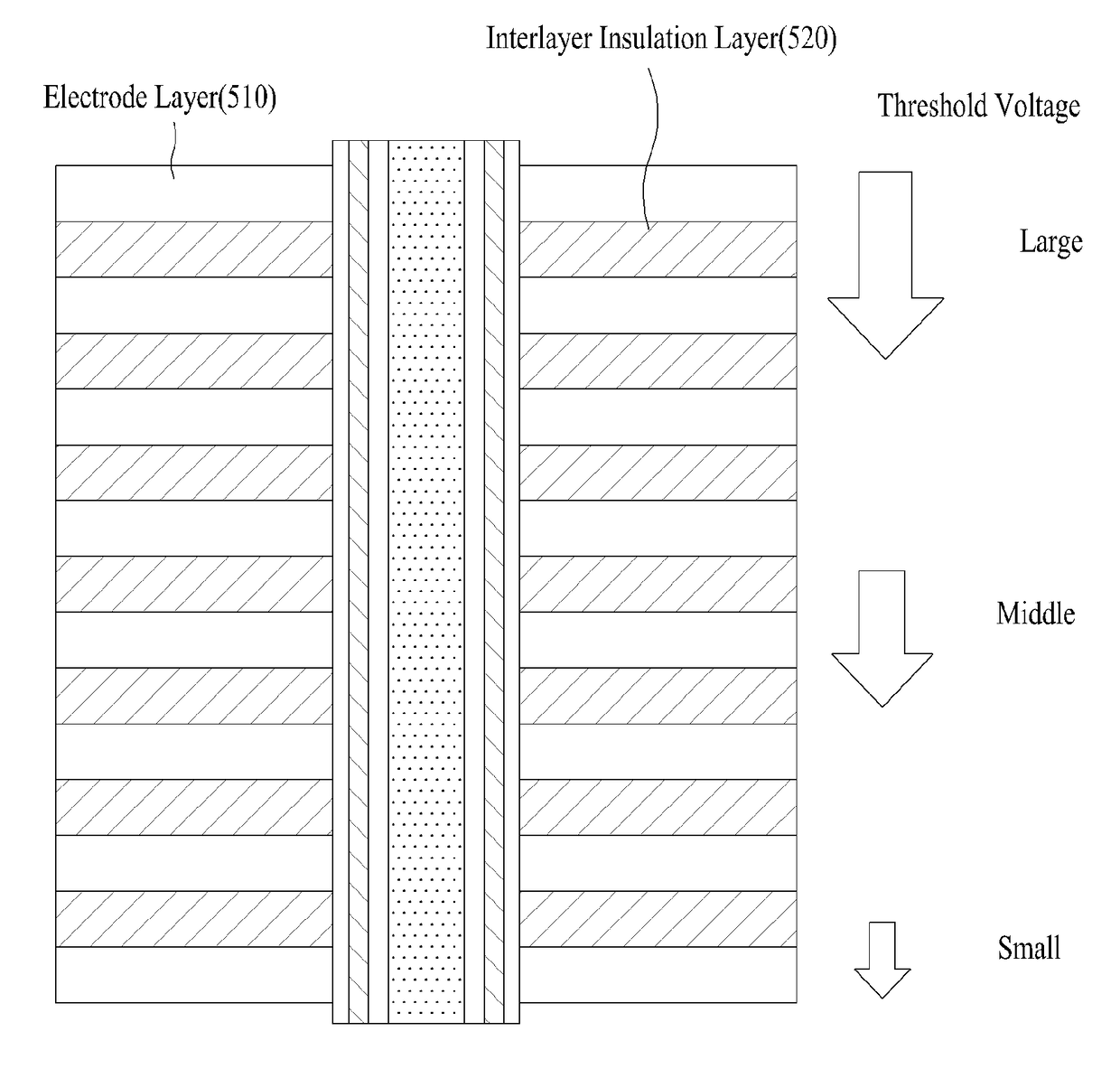

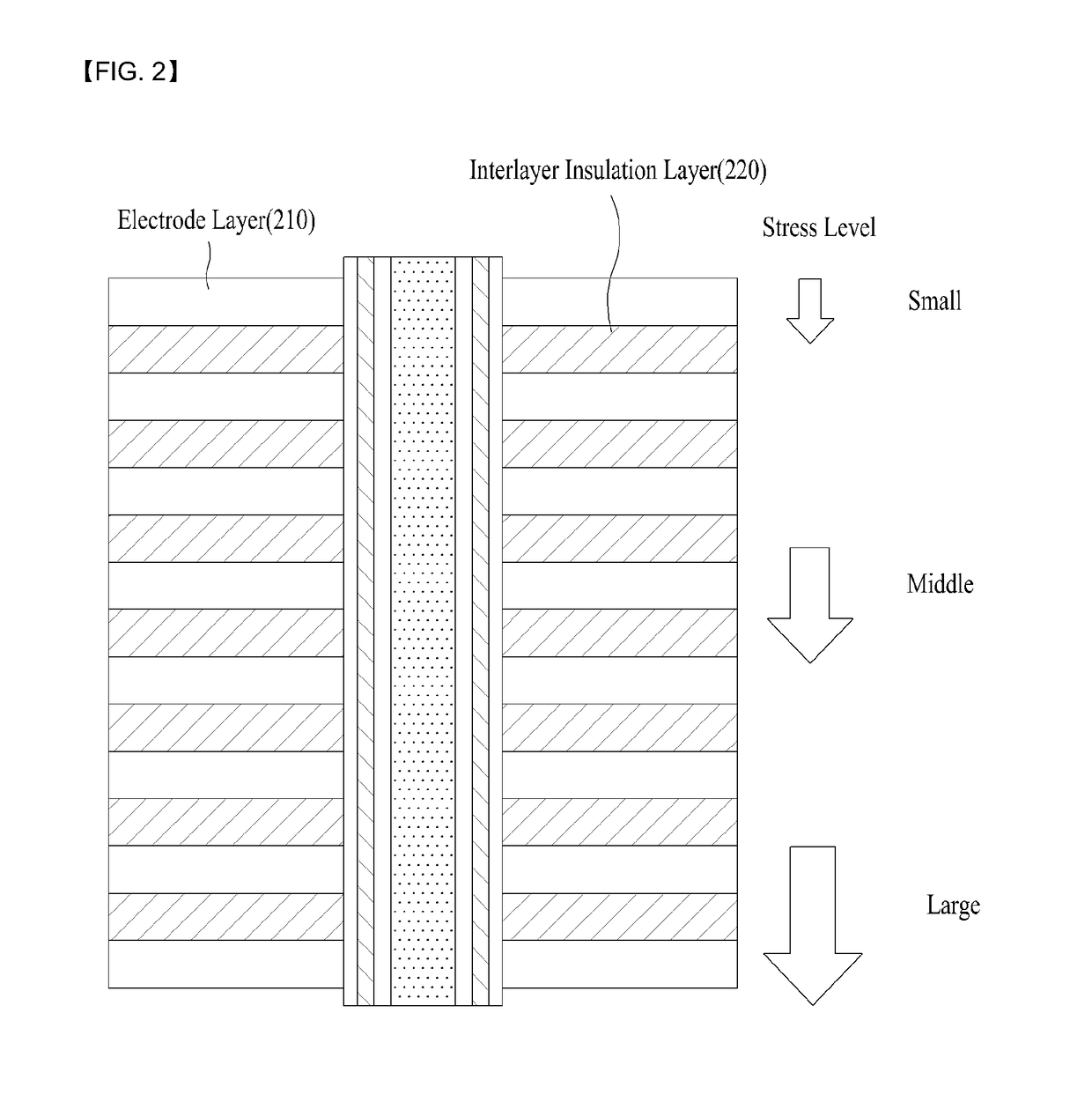

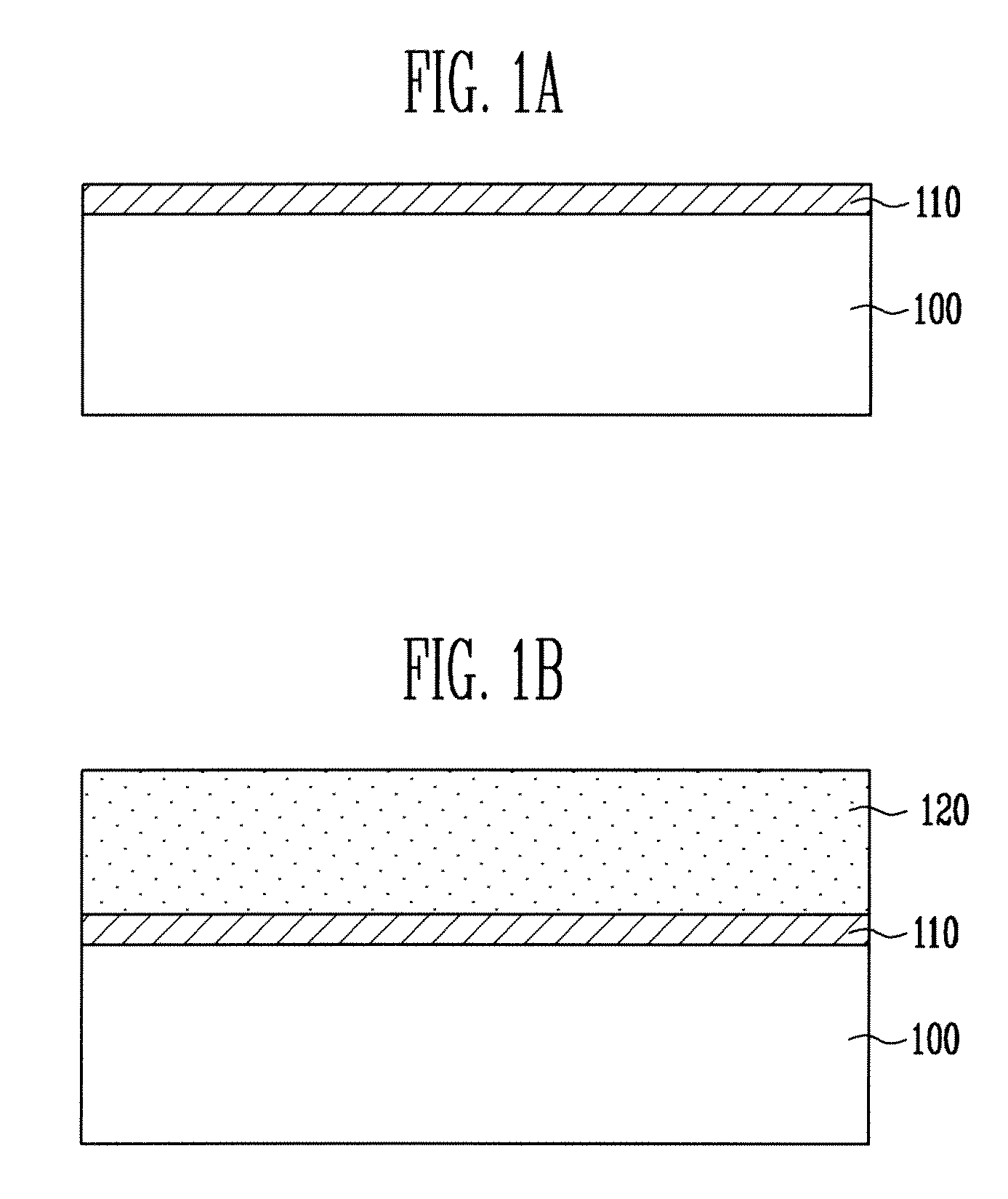

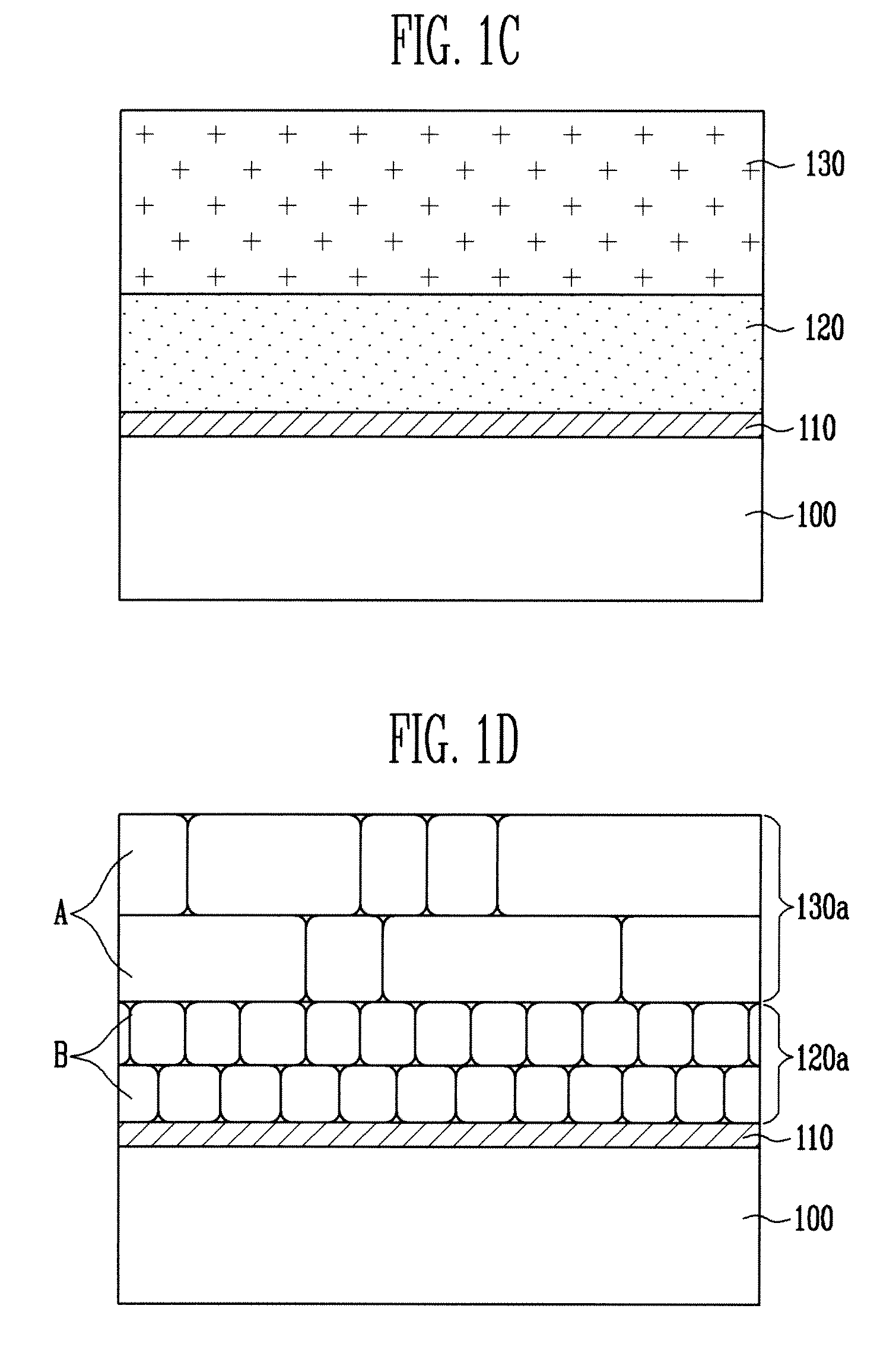

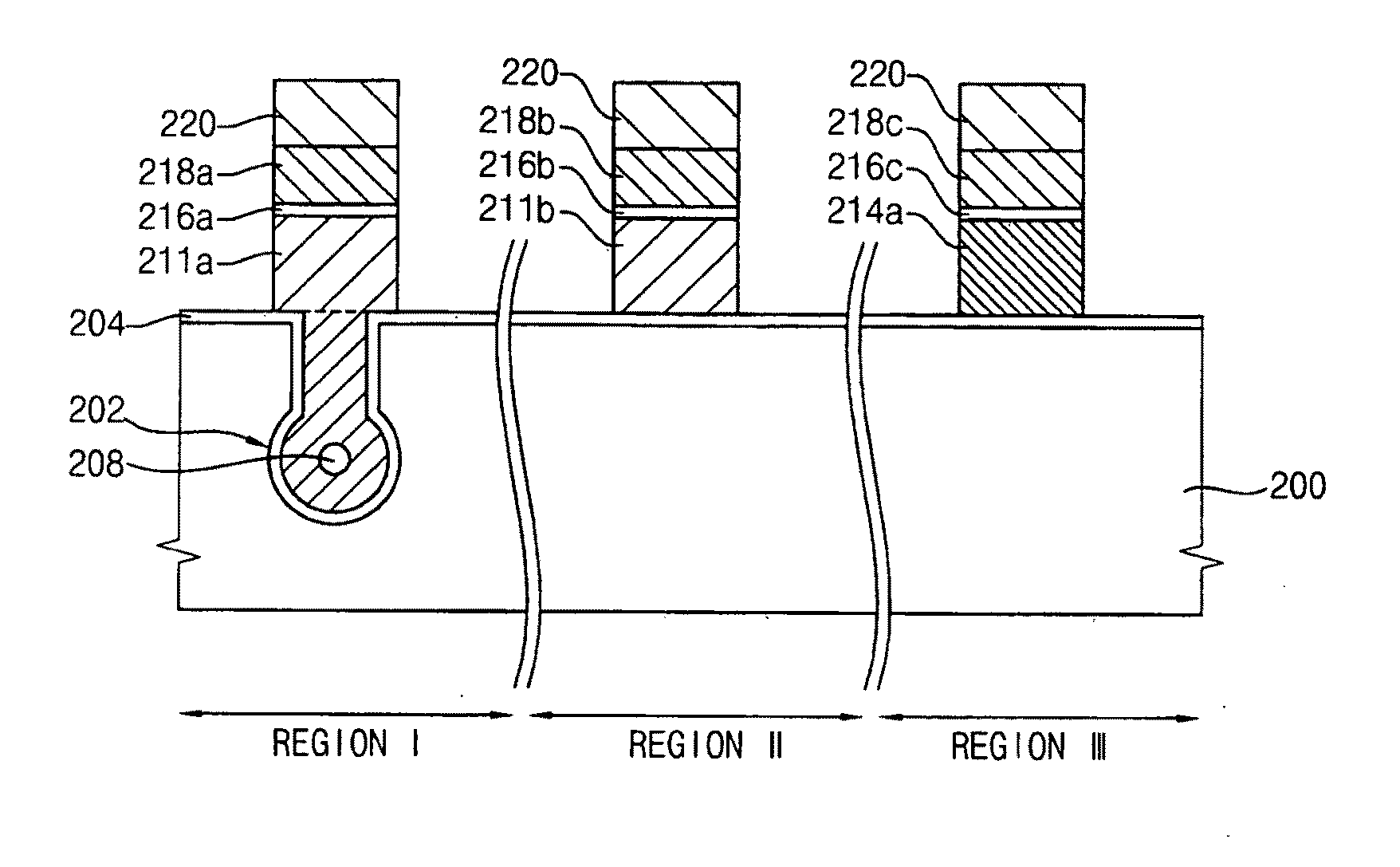

Three dimensional flash memory using electrode layers and/or interlayer insulation layers having different properties, and preparation method therefor

ActiveUS9922990B2Improved Threshold Voltage DistributionIncrease credibilitySolid-state devicesRead-only memoriesInsulation layerPhysical chemistry

Embodiments of the present invention enable threshold voltage distribution of a plurality of electrode layers to be improved by configuring each of the plurality of electrode layer maintains to have different physical structures or materials, etc., thereby enhancing credibility during a process of maintaining stores data and a reading process.

Owner:SAMSUNG ELECTRONICS CO LTD

Nonvolatile memory and related reprogramming method

InactiveUS9281068B2Improve programming speedImproved Threshold Voltage DistributionMemory architecture accessing/allocationRead-only memoriesOperating systemPage buffers

A method of reprogramming a nonvolatile memory device, comprising setting up bit lines of selected memory cells according to logic values of first and second latches of a page buffer connected to the bit lines, supplying a program pulse to the selected memory cells, performing a program verify operation on the selected memory cells using the first and second latches, and performing a predictive program operation on the selected memory cells according to a result of the program verify operation. In the predictive program operation, bit lines of the selected memory cells are setup according to a logic value of a third latch of the page buffer that corresponds to each of the selected memory cells.

Owner:SAMSUNG ELECTRONICS CO LTD

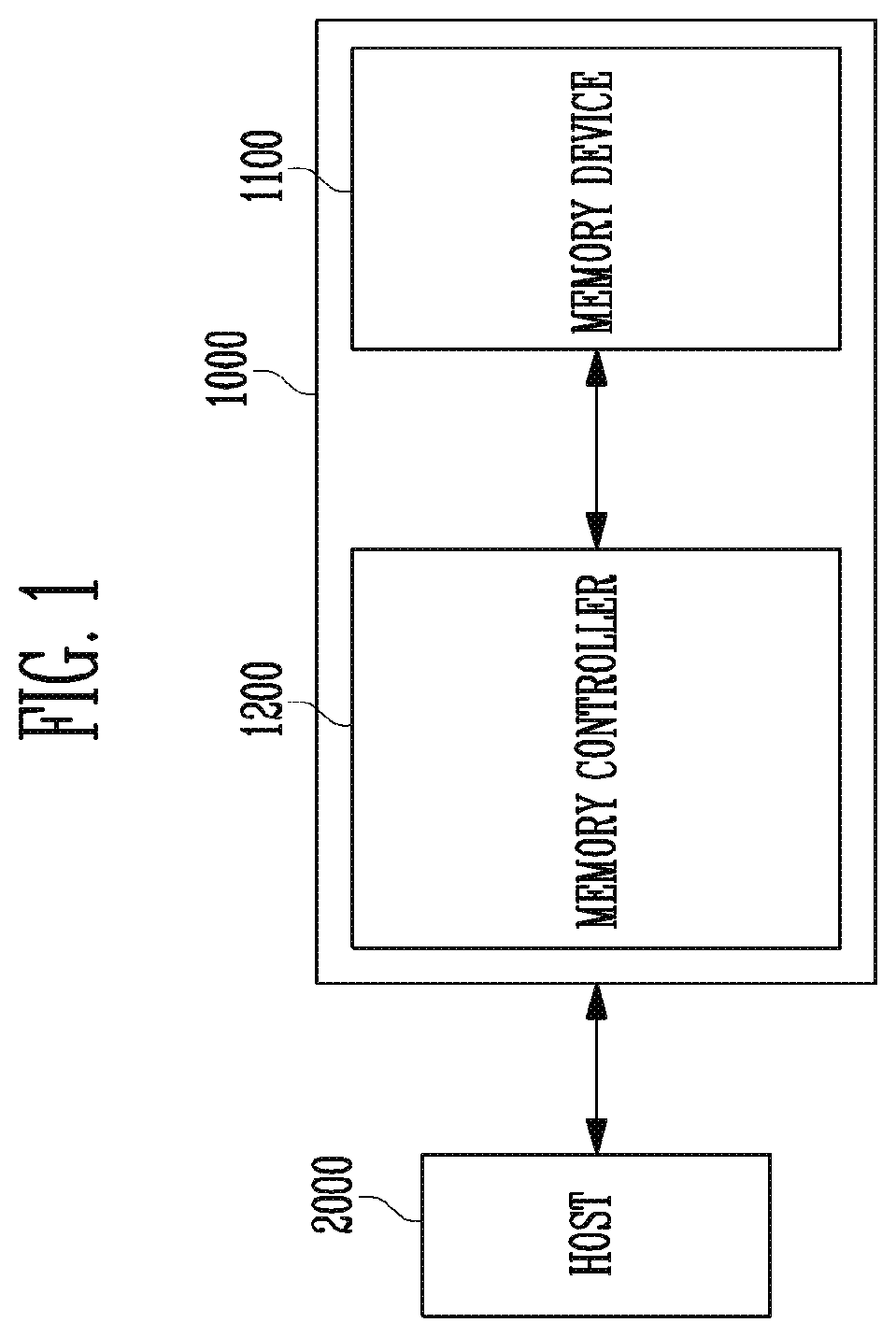

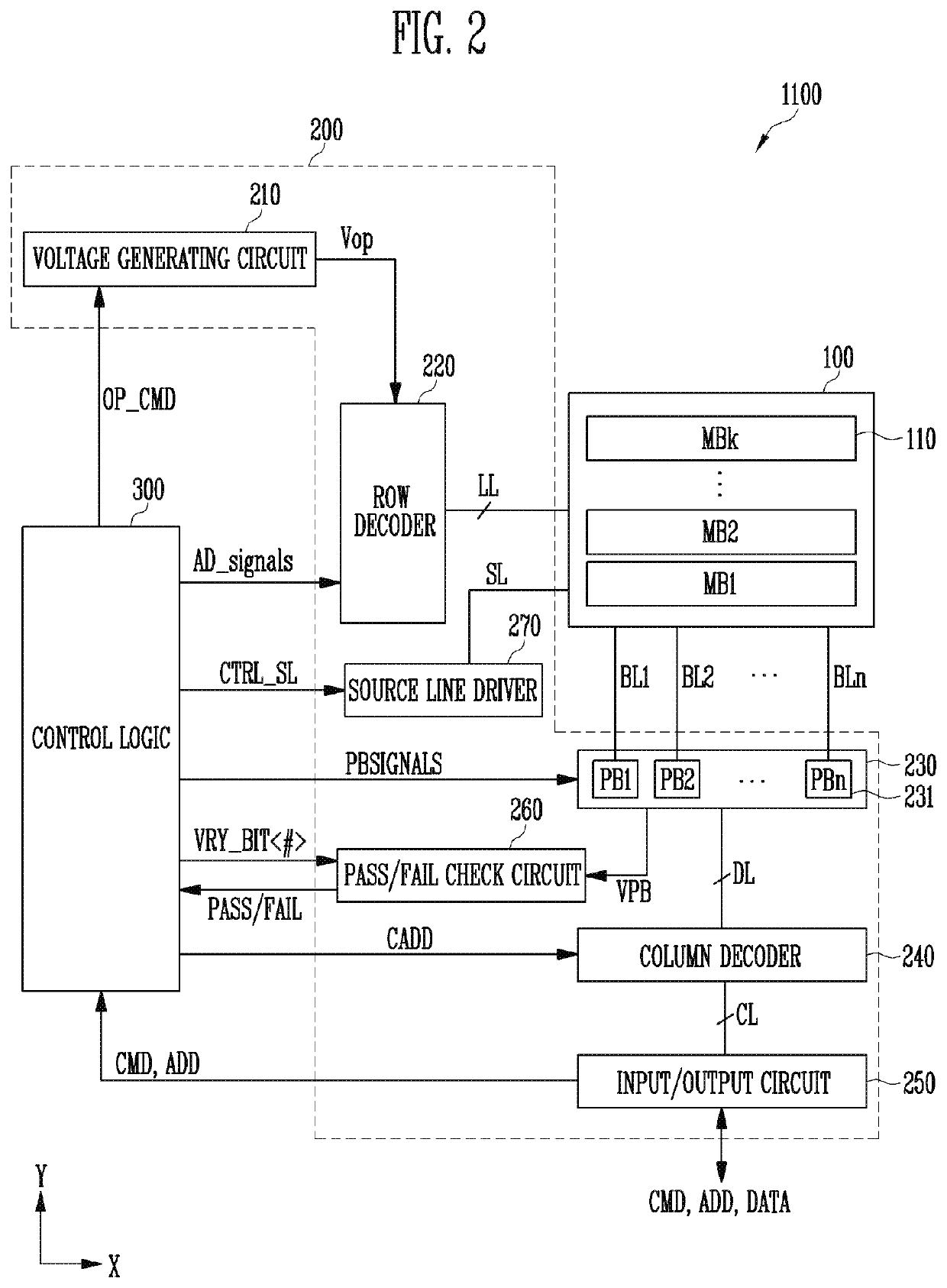

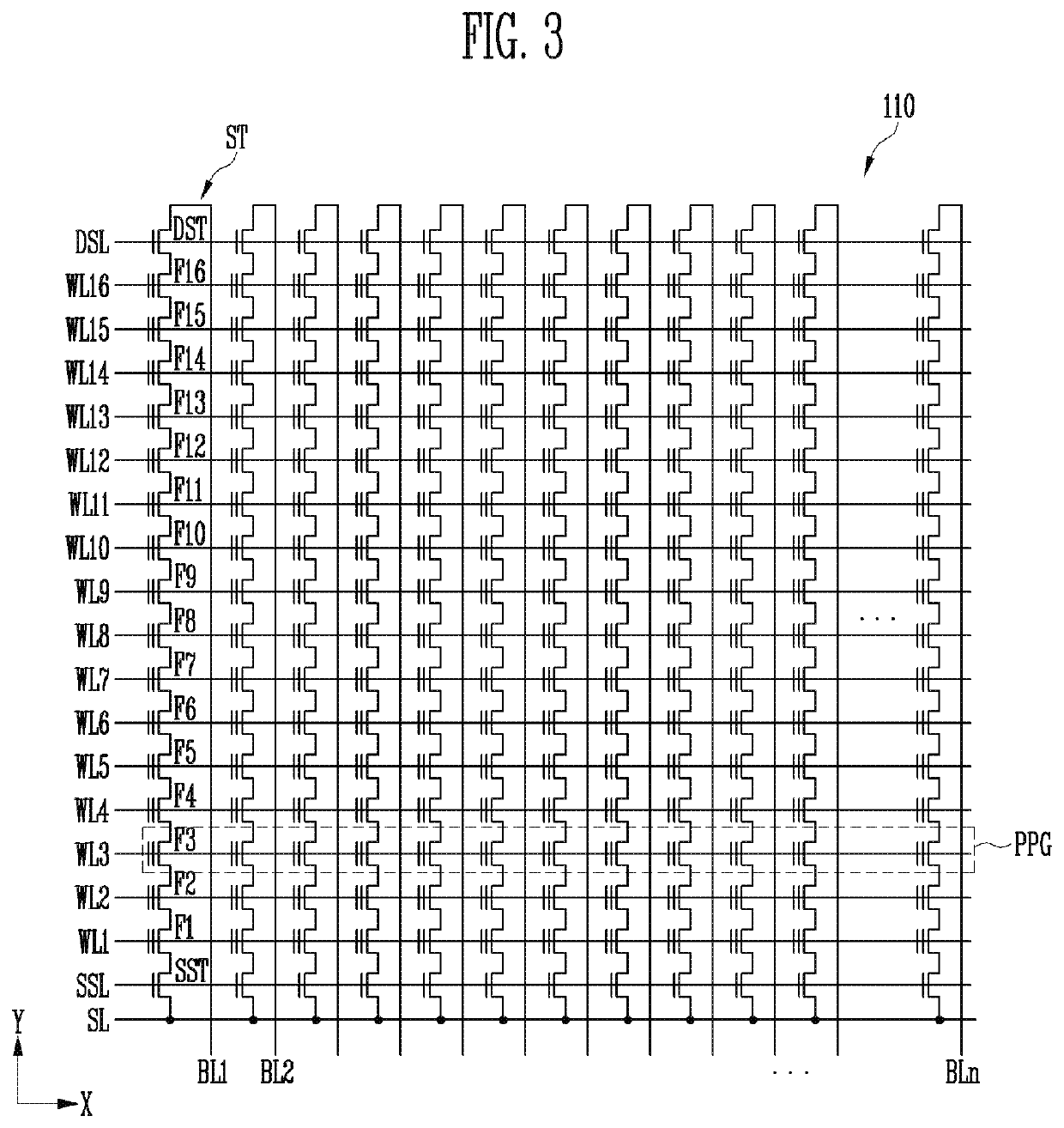

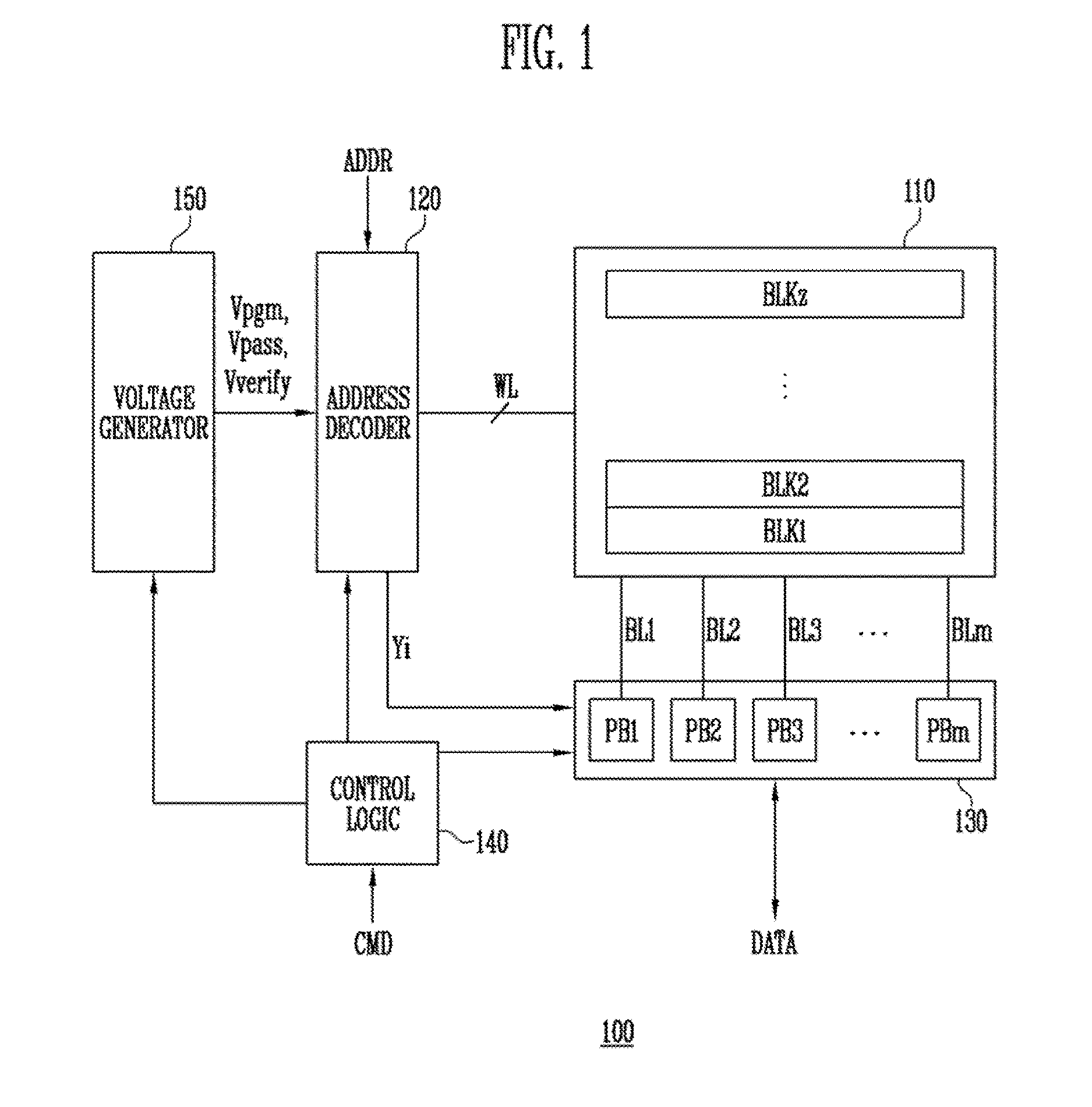

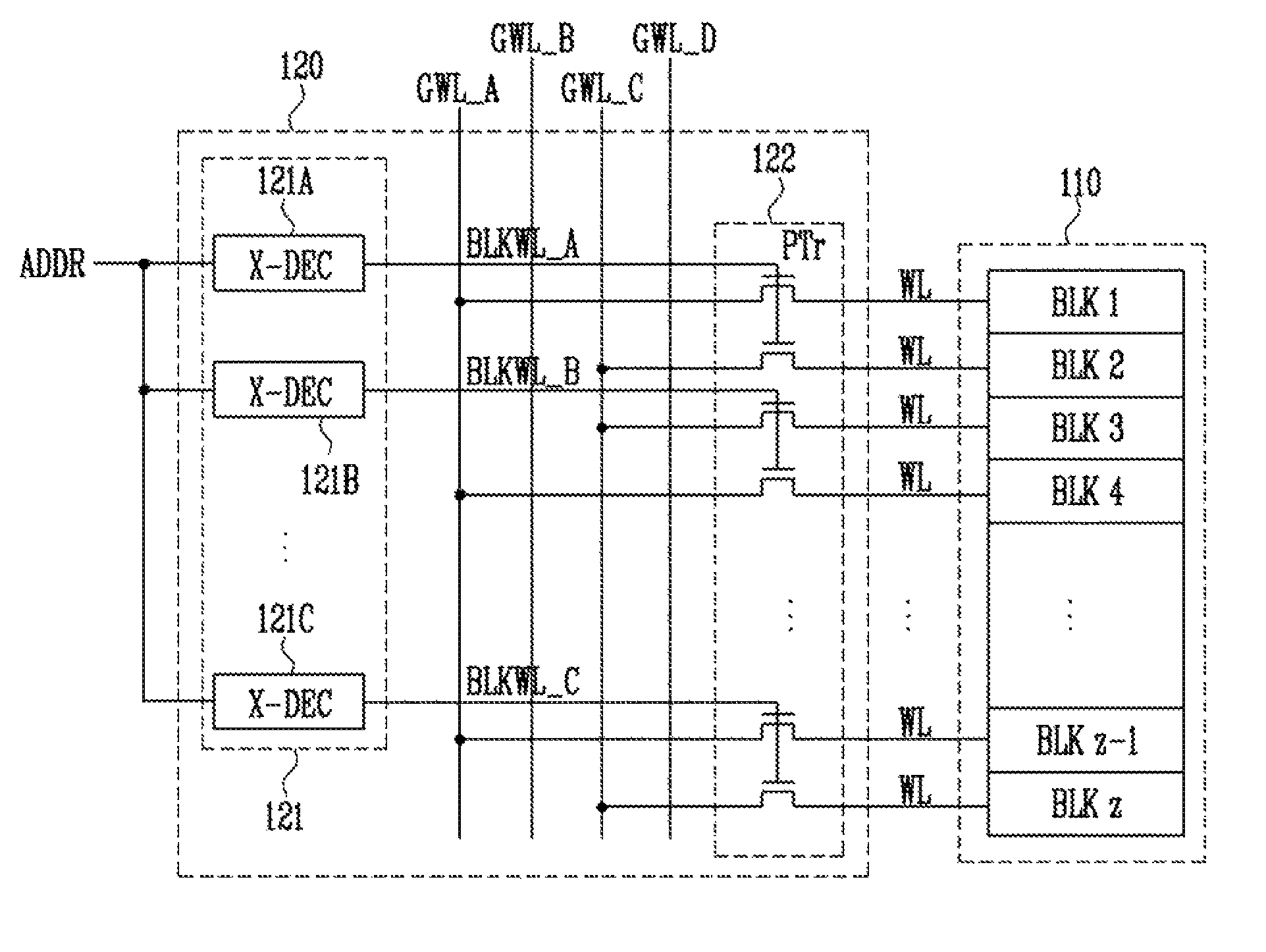

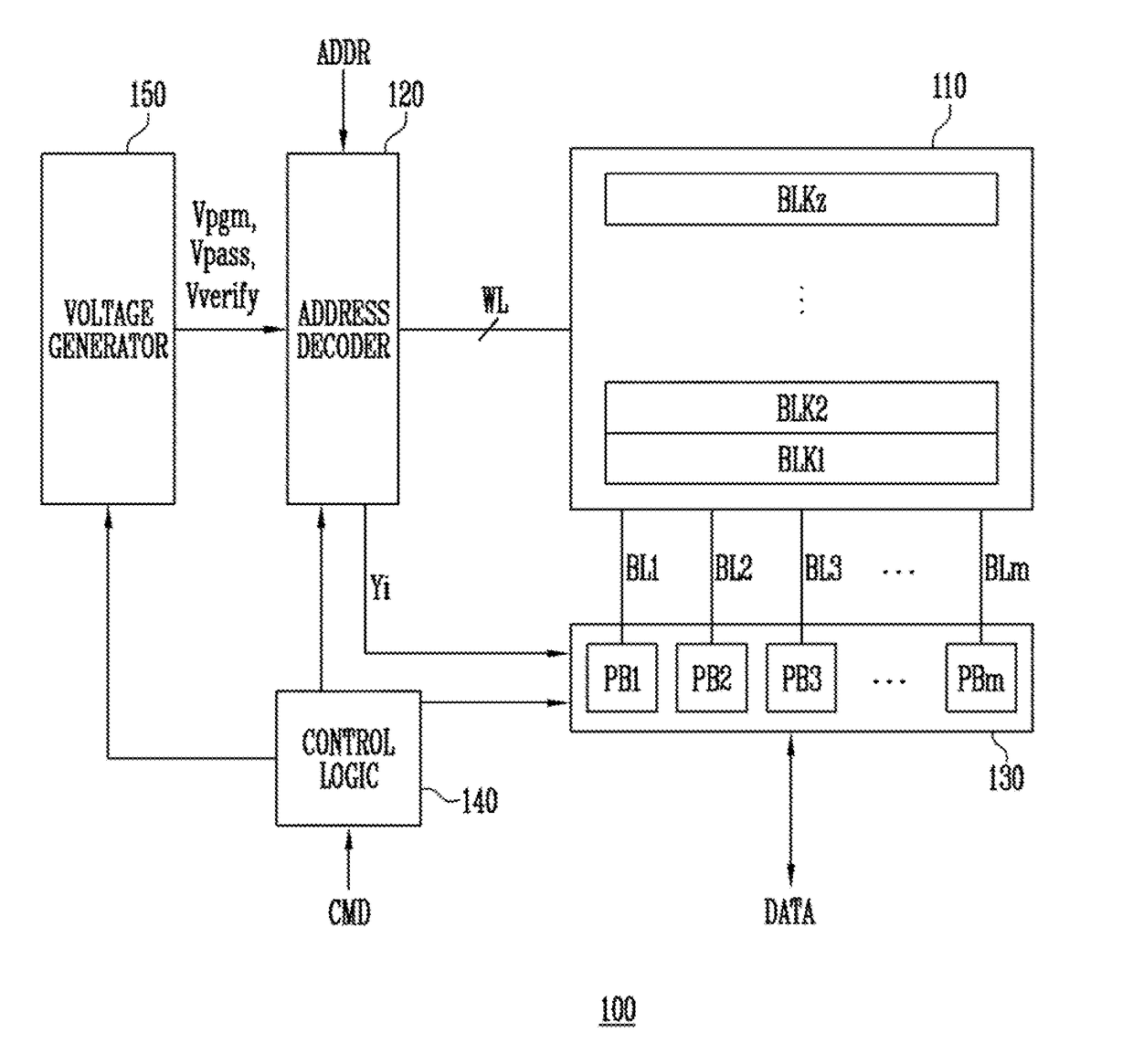

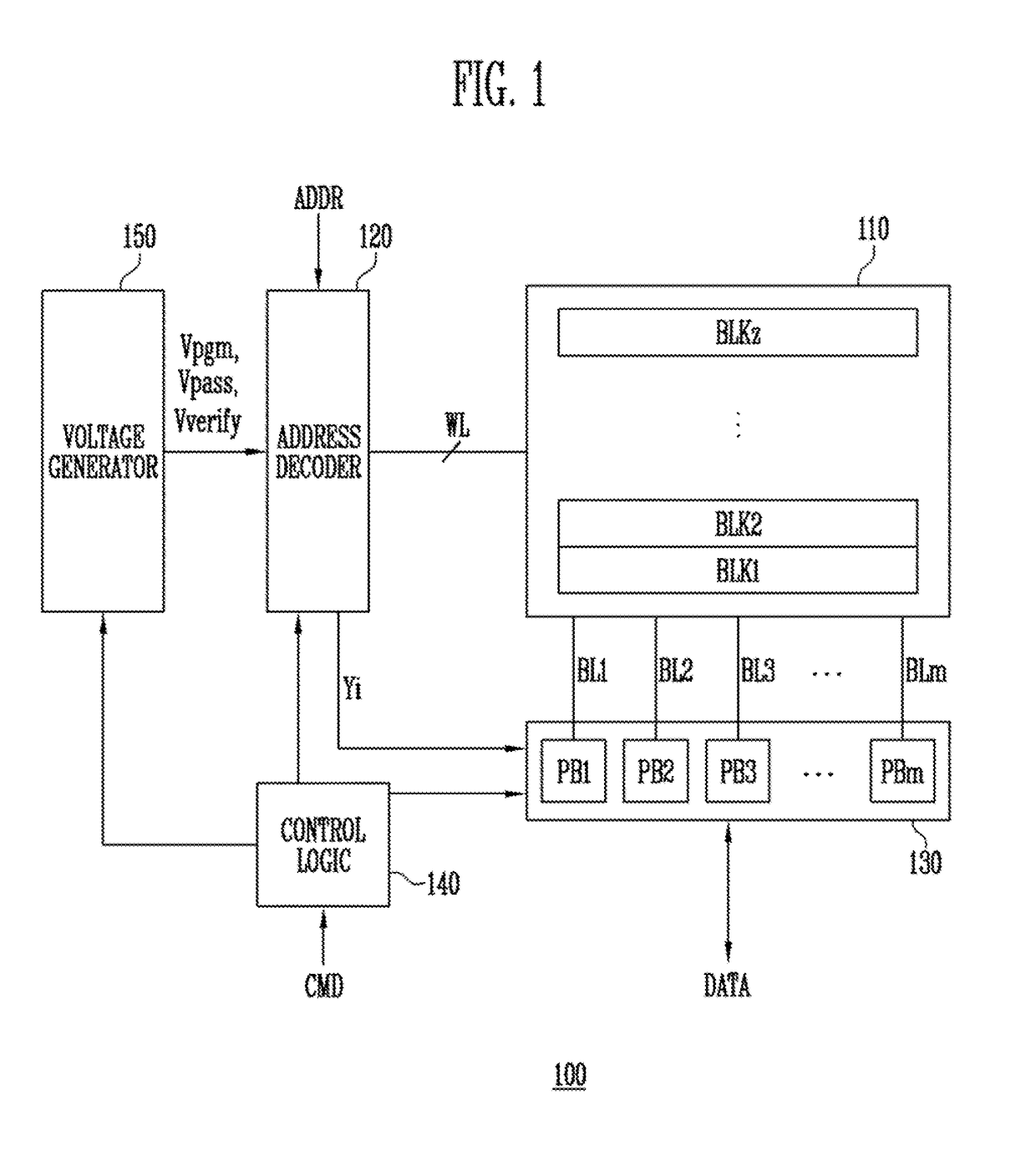

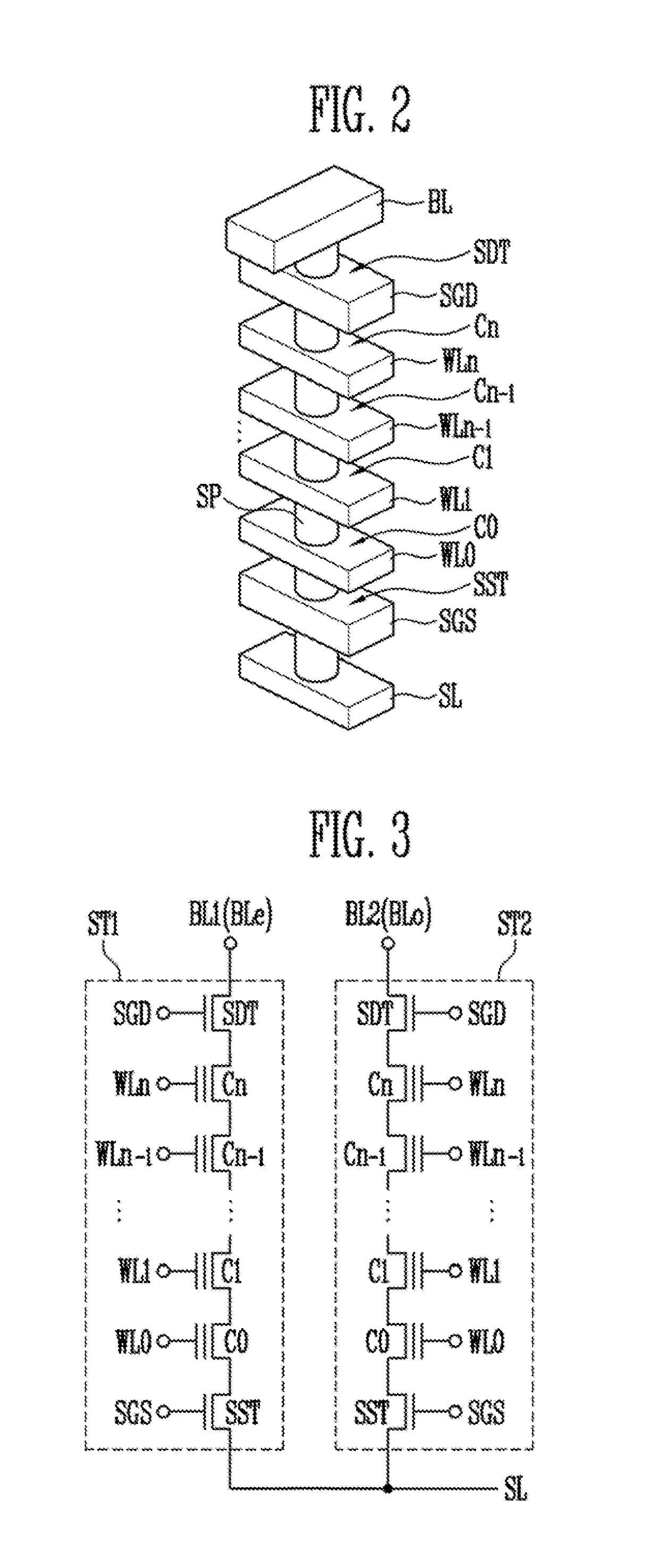

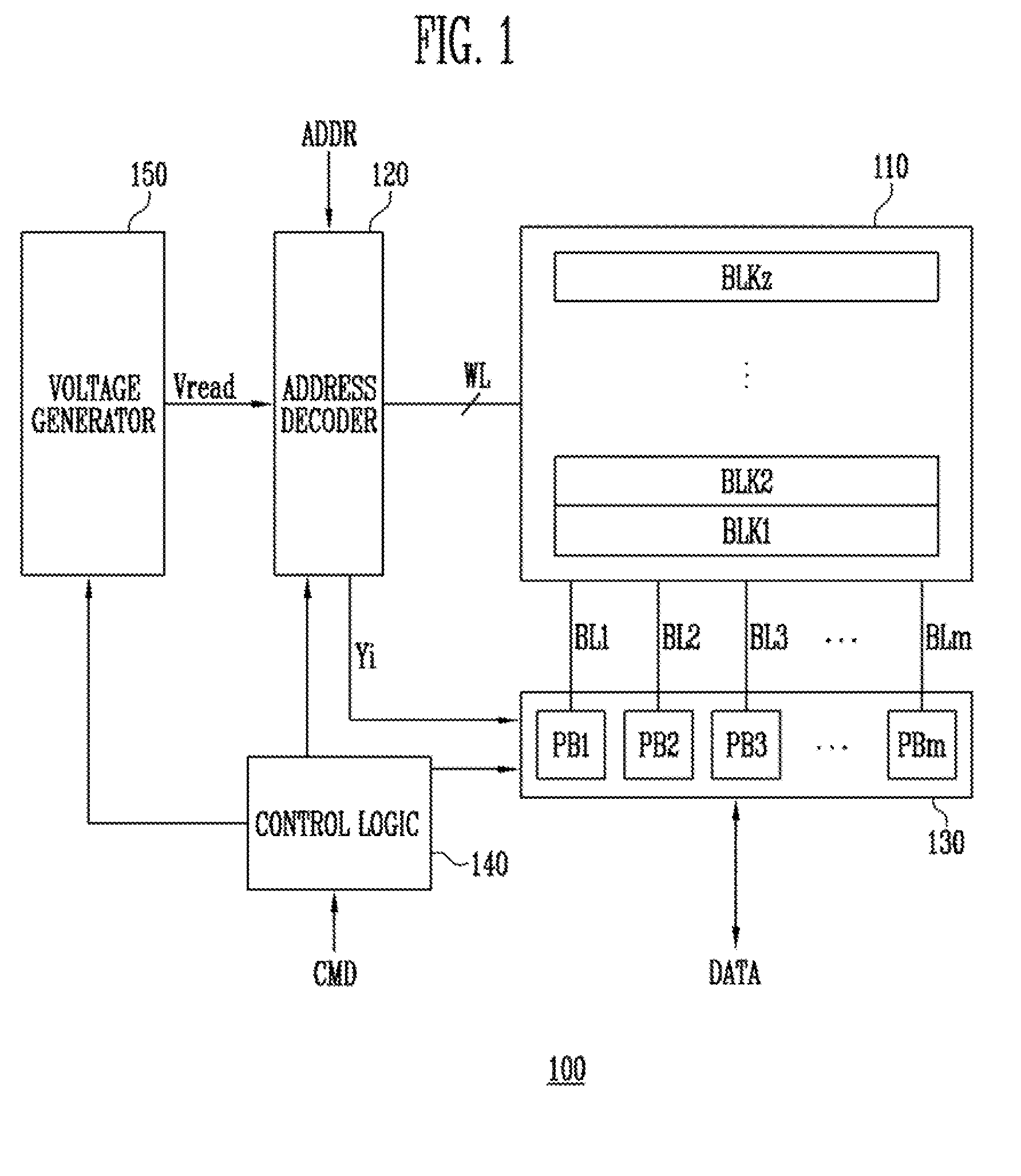

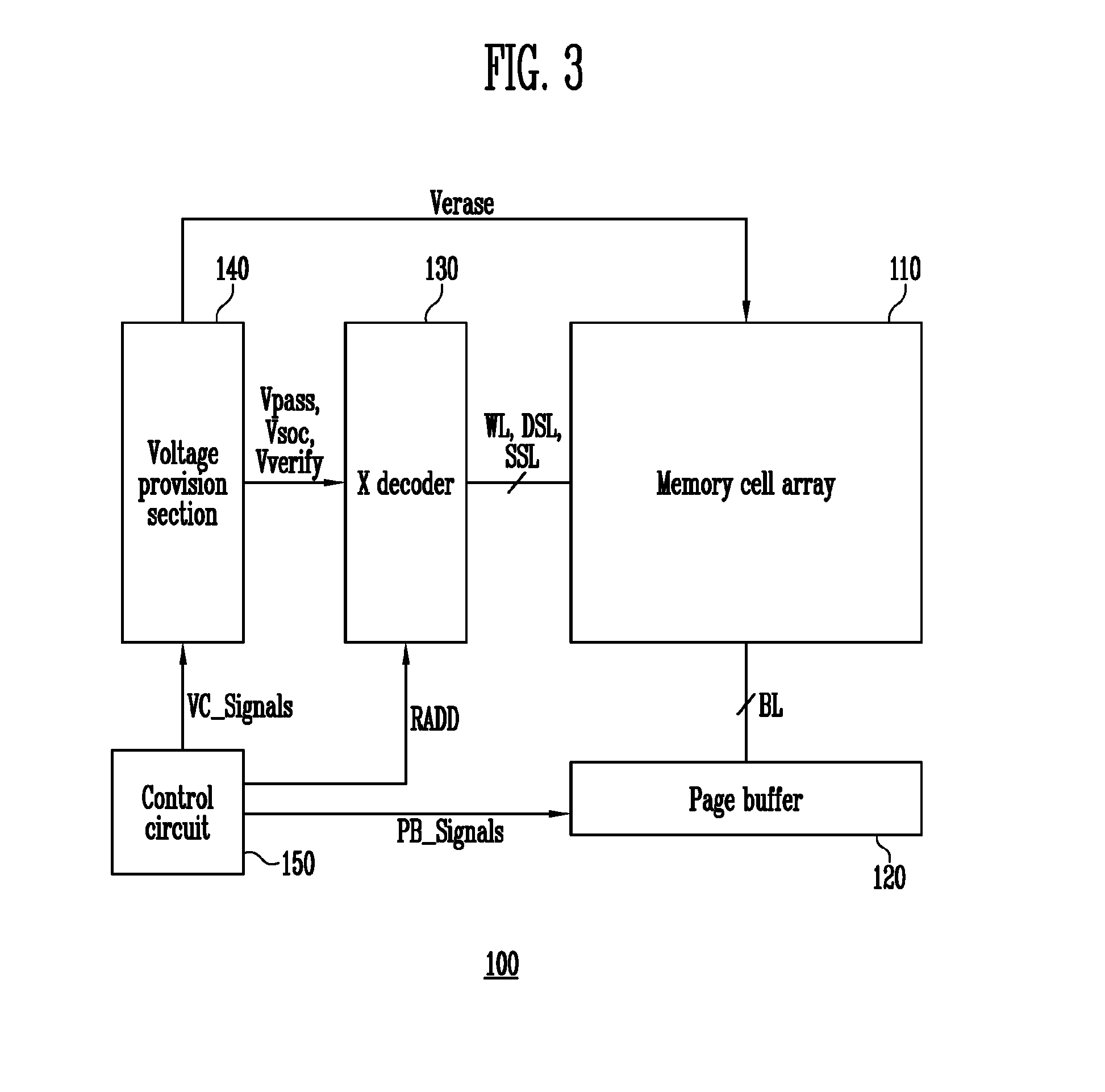

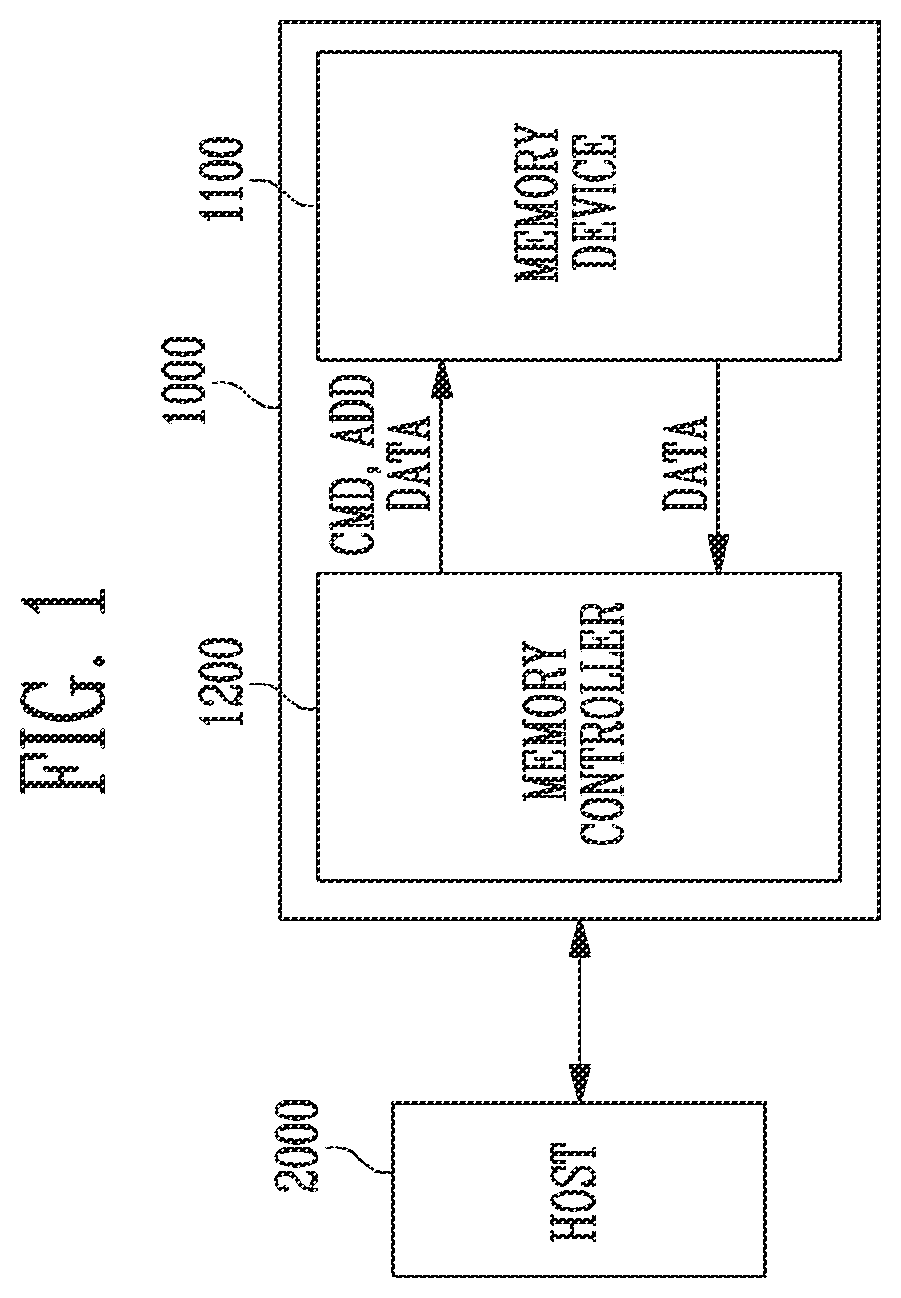

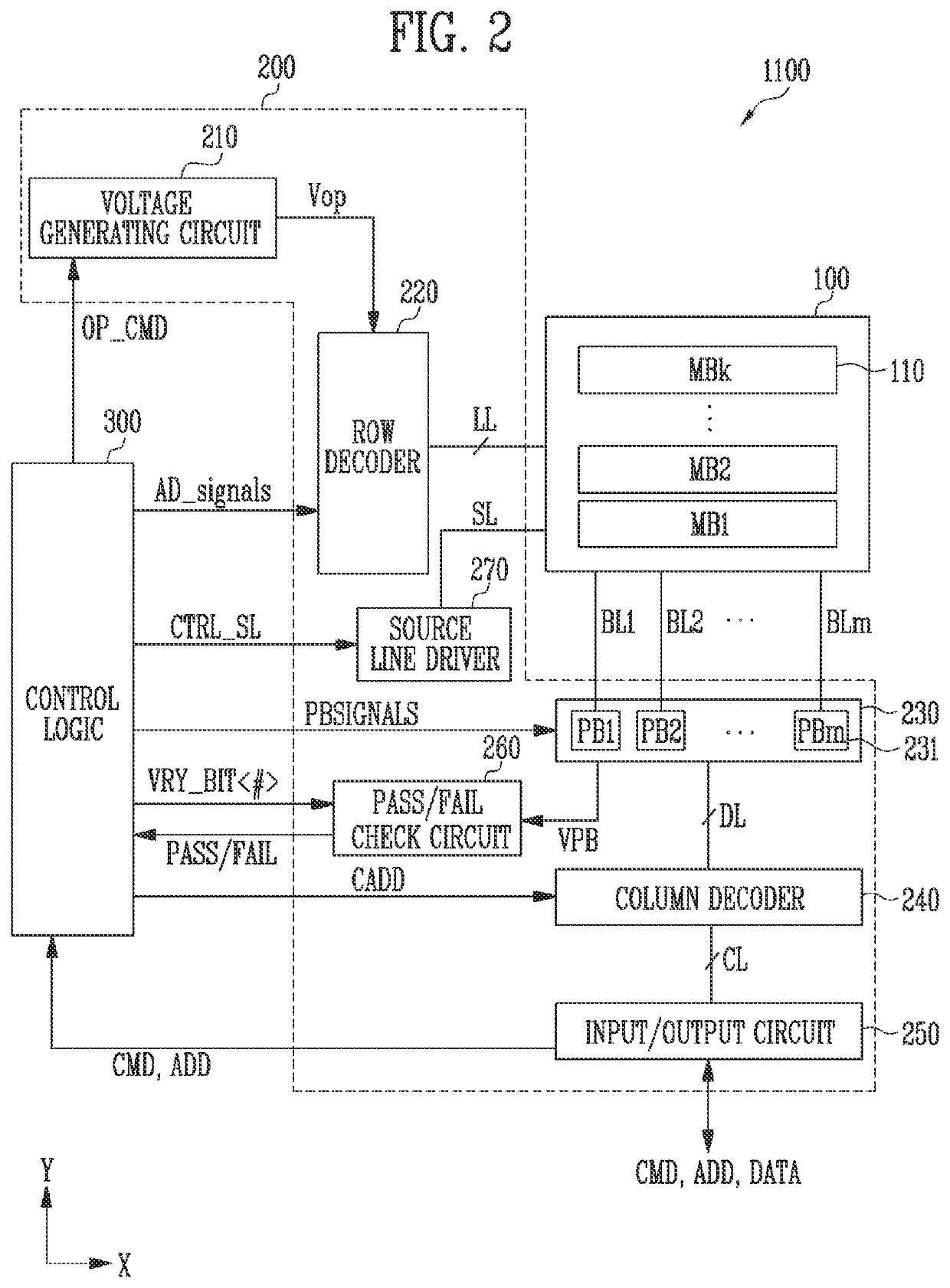

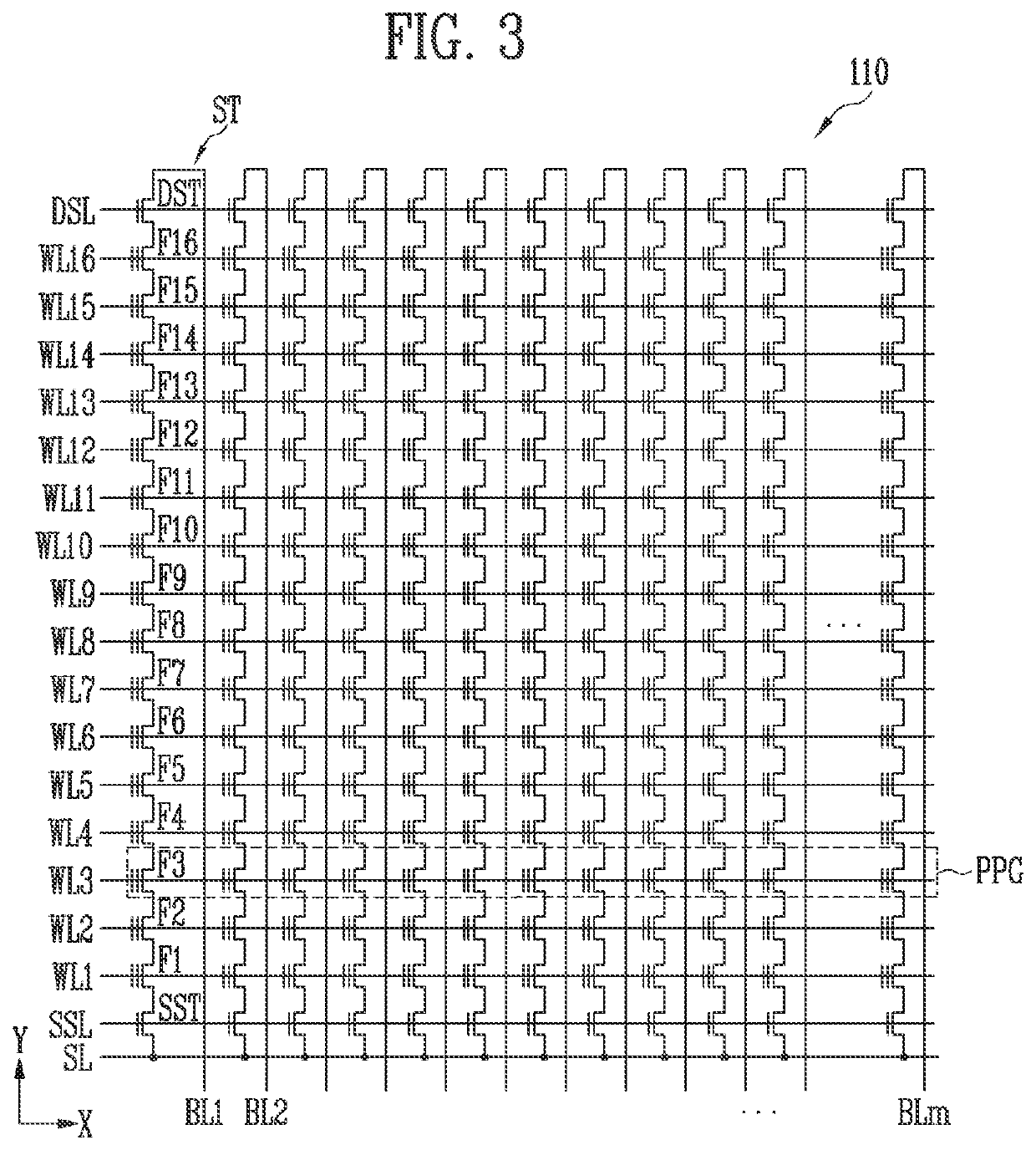

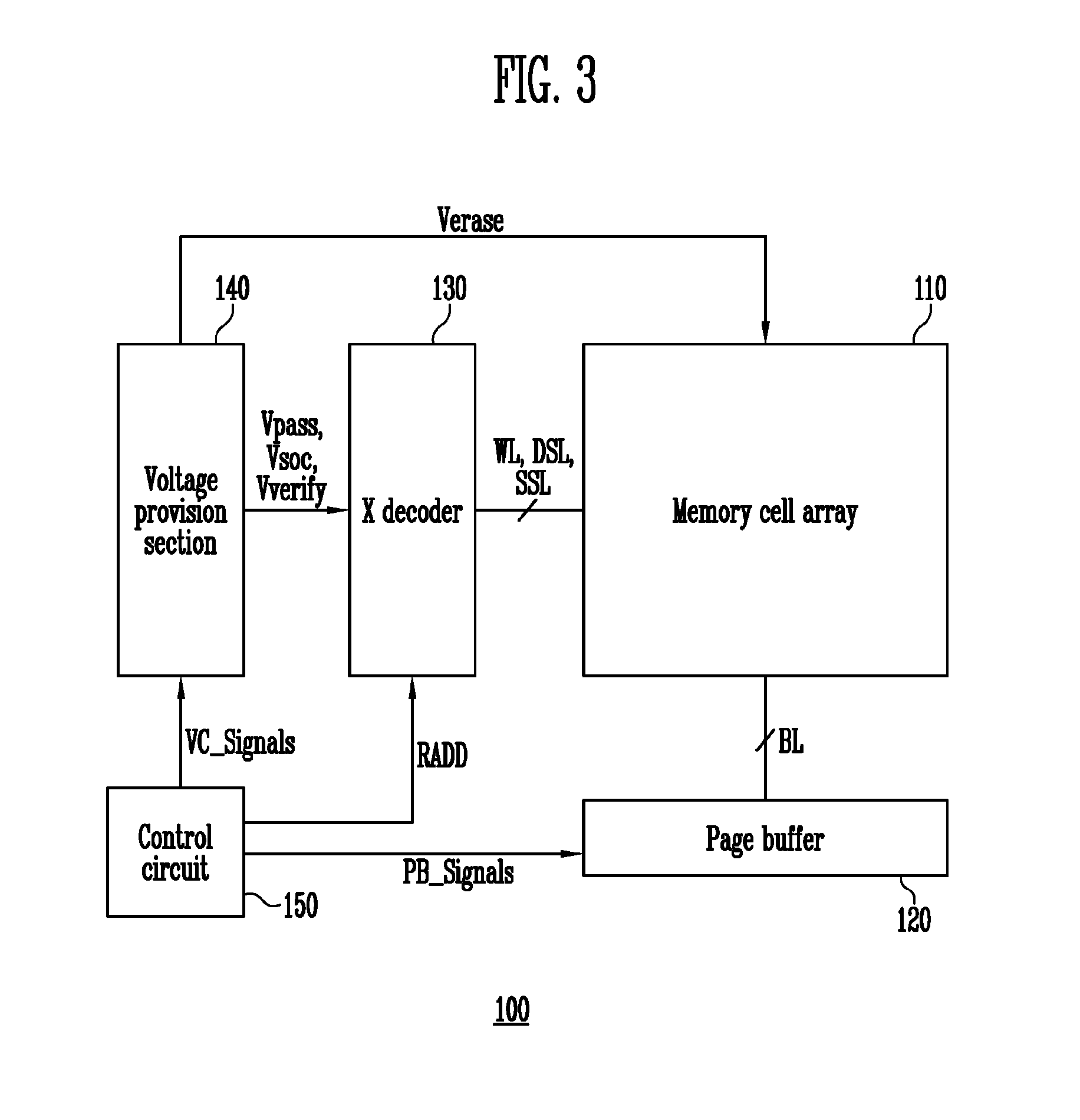

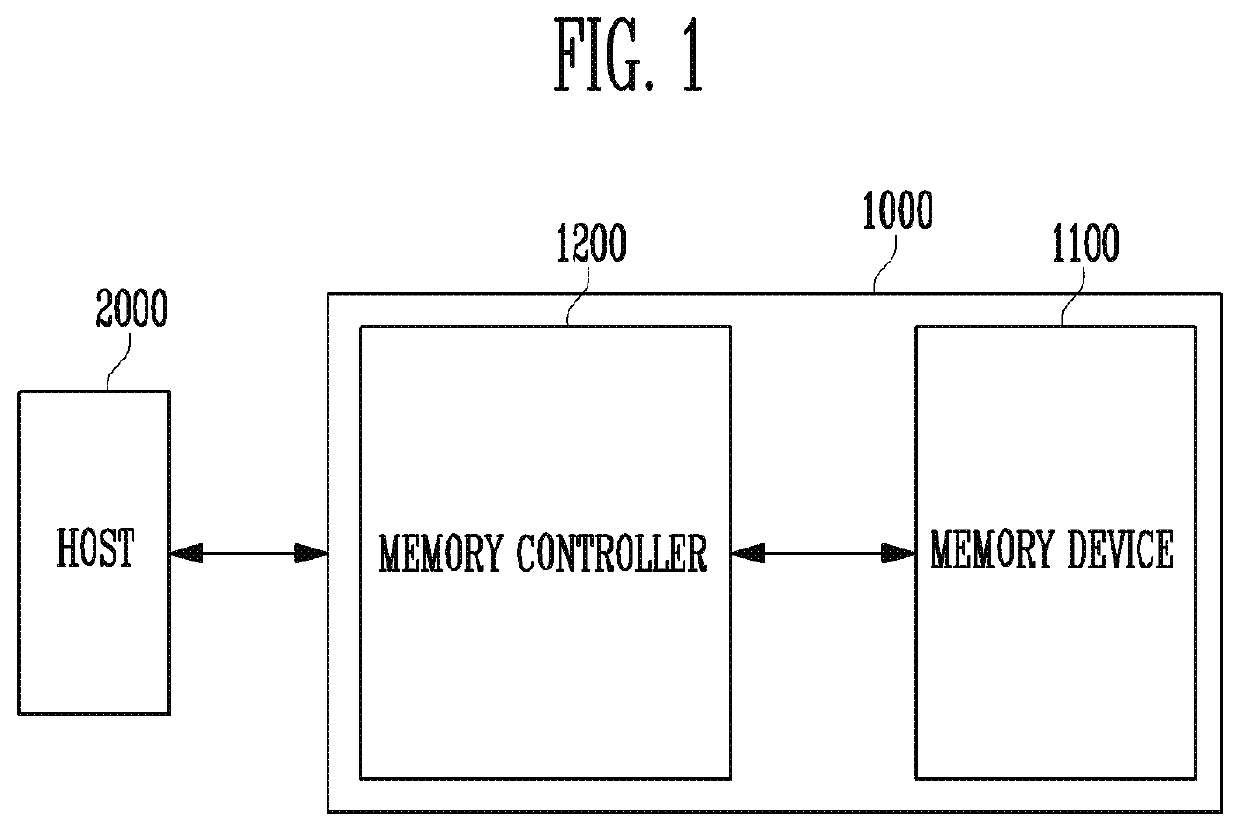

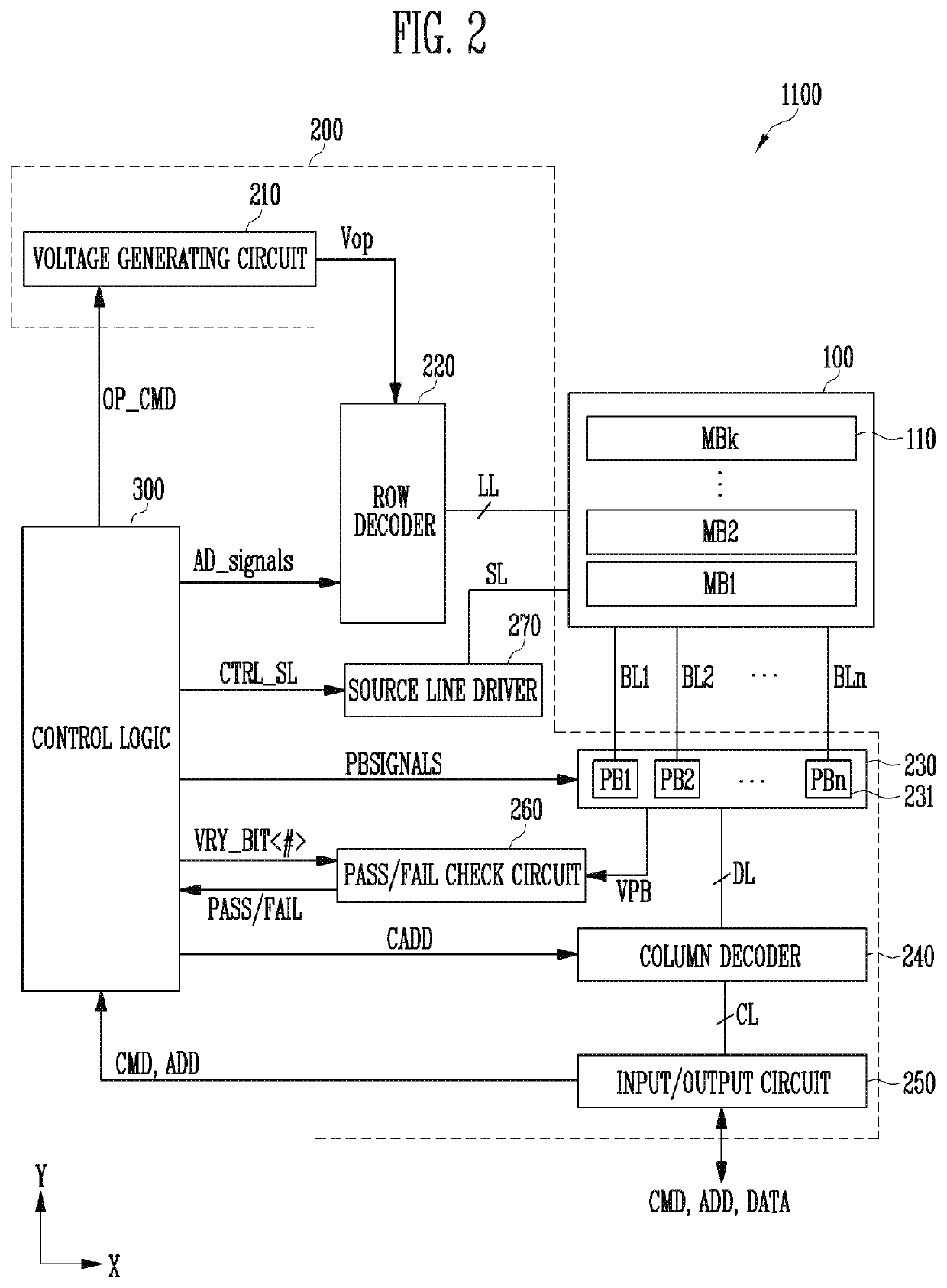

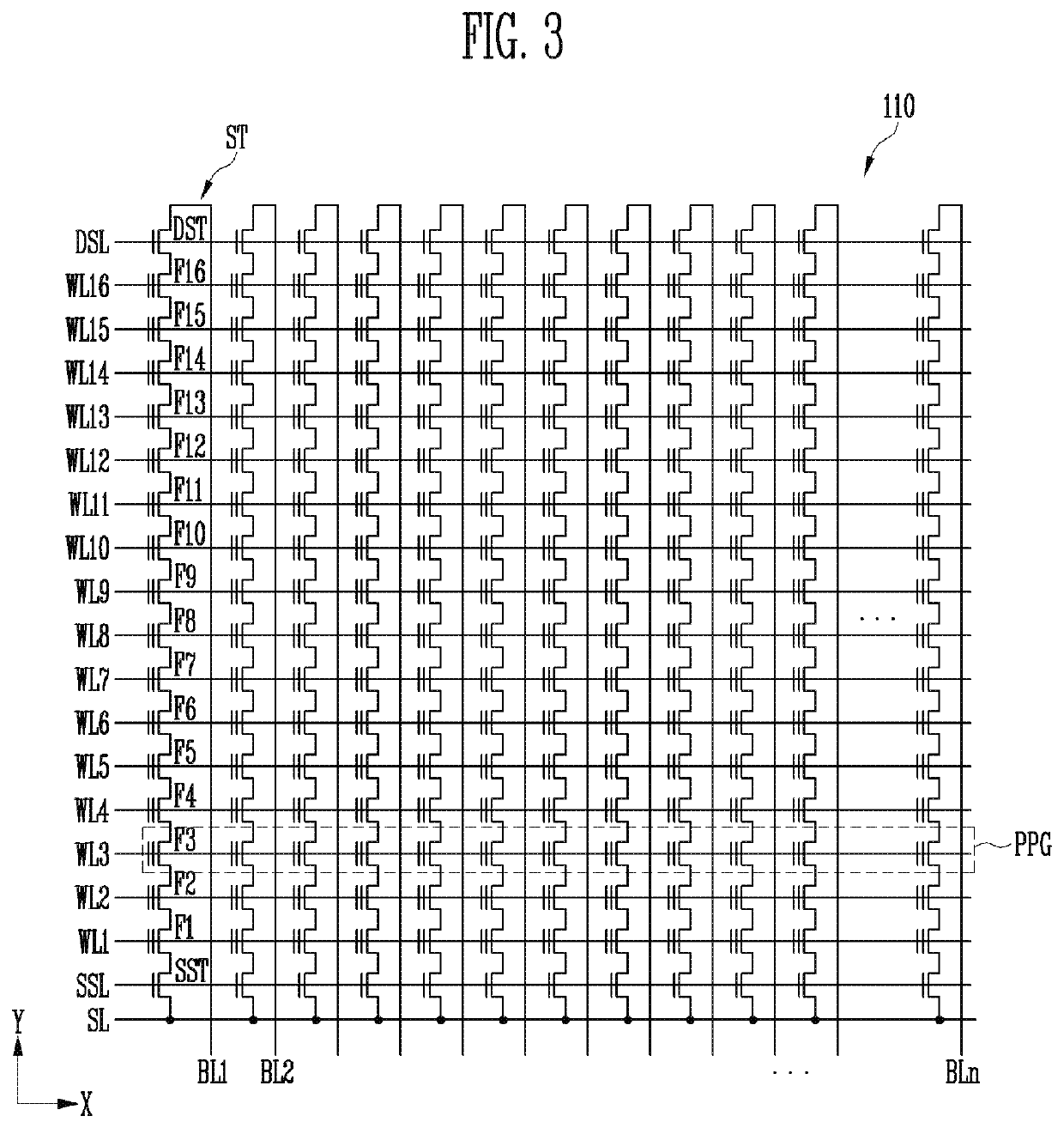

Memory device and an operating method of a memory device

ActiveUS20200111535A1Improved Threshold Voltage DistributionRead-only memoriesStorage cellEngineering

A memory device and an operating method of the memory device is disclosed. The memory device includes a memory cell array including a plurality of memory blocks. The memory device further includes a peripheral circuit for performing an erase voltage application operation, a first erase verify operation, and a second erase verify operation on a selected memory block among the plurality of memory blocks. The memory device also includes a control logic for setting a start erase voltage of an erase operation, based on a result of the first erase verify operation, and controlling the peripheral circuit to perform the second erase verify operation when it is determined that the first erase verify operation on the selected memory block has been passed.

Owner:SK HYNIX INC

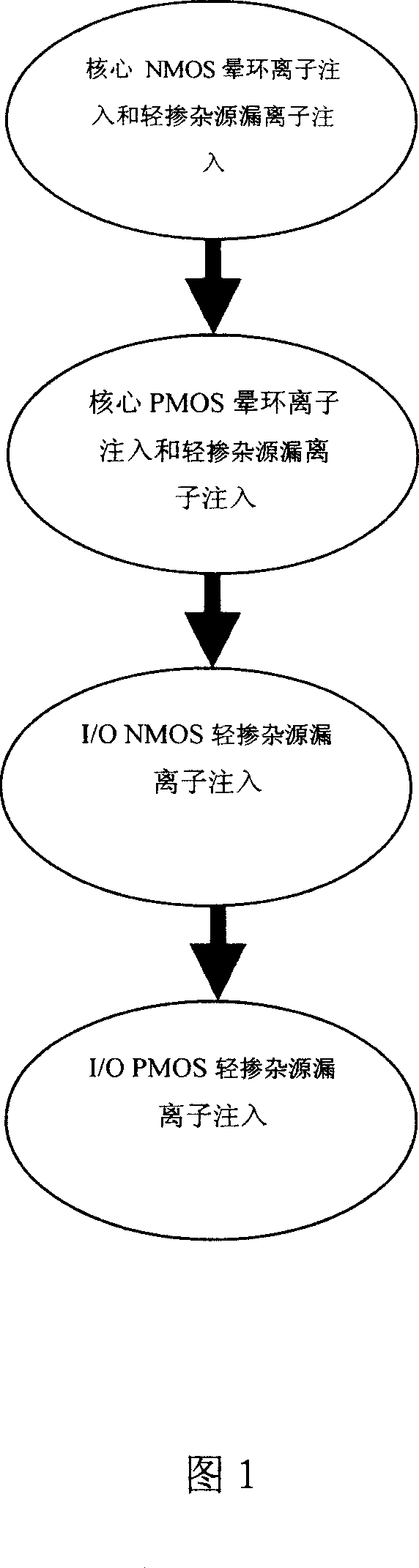

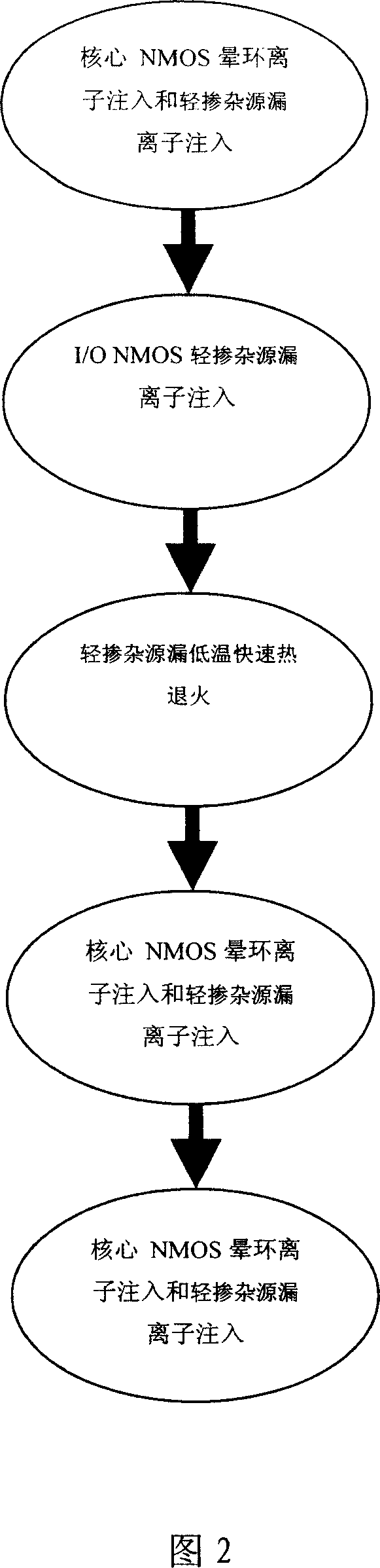

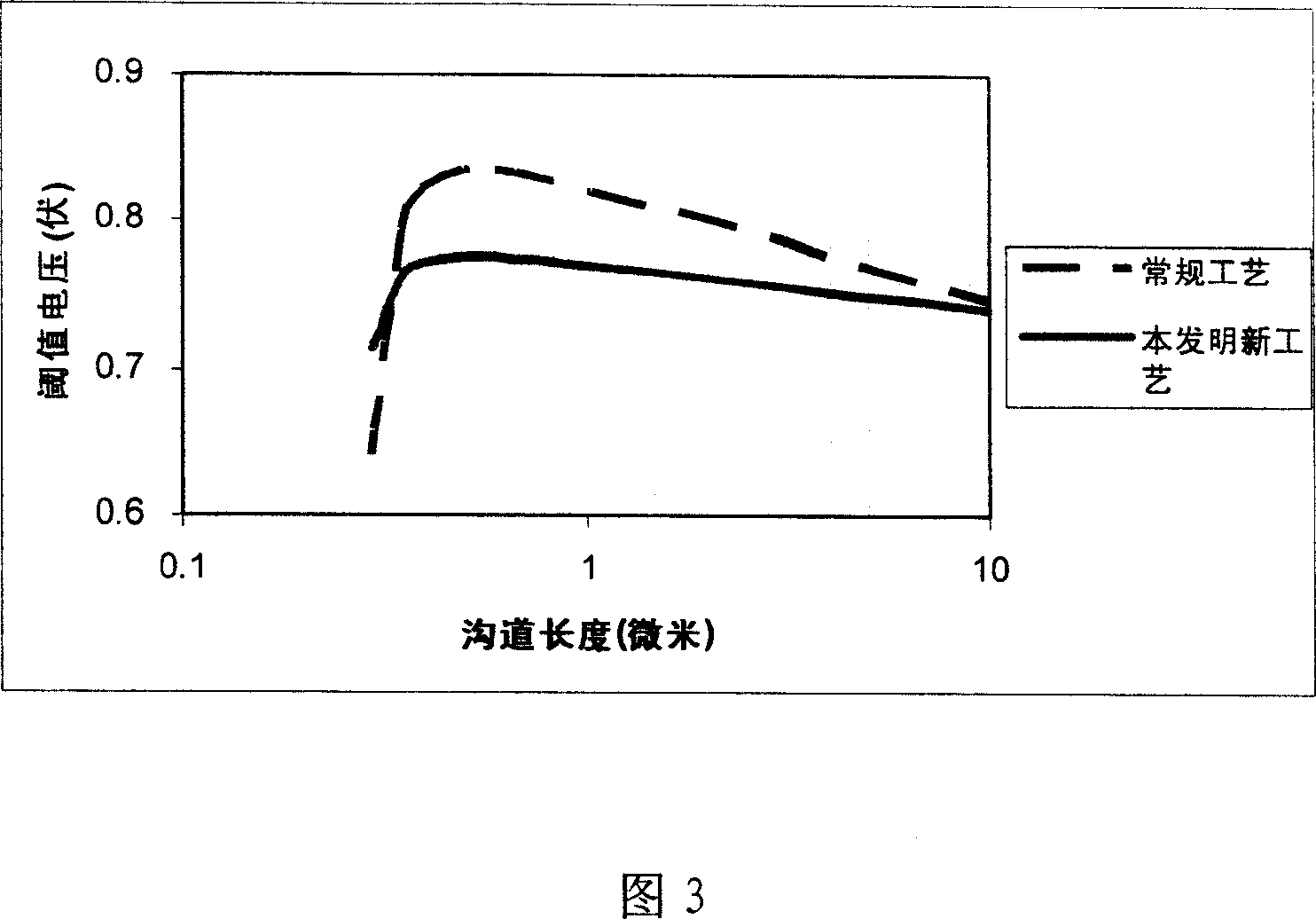

Method for improving voltage distribution of component threshold value

ActiveCN1929098AReduce leakage currentImprove featuresSemiconductor/solid-state device manufacturingRapid thermal annealingIon implantation

This invention discloses one method to improve parts valve voltage distribution, which comprises the following steps: core NMOS air ring ion injection and LDD ion injection; I / O NMOS and LDD ion injecting; c, LDD low temperature rapid annealing; d, core PMOS air ring ion injecting and LDD ion injecting; e, I / O PMOS LDD ion injecting.

Owner:SHANGHAI HUAHONG GRACE SEMICON MFG CORP

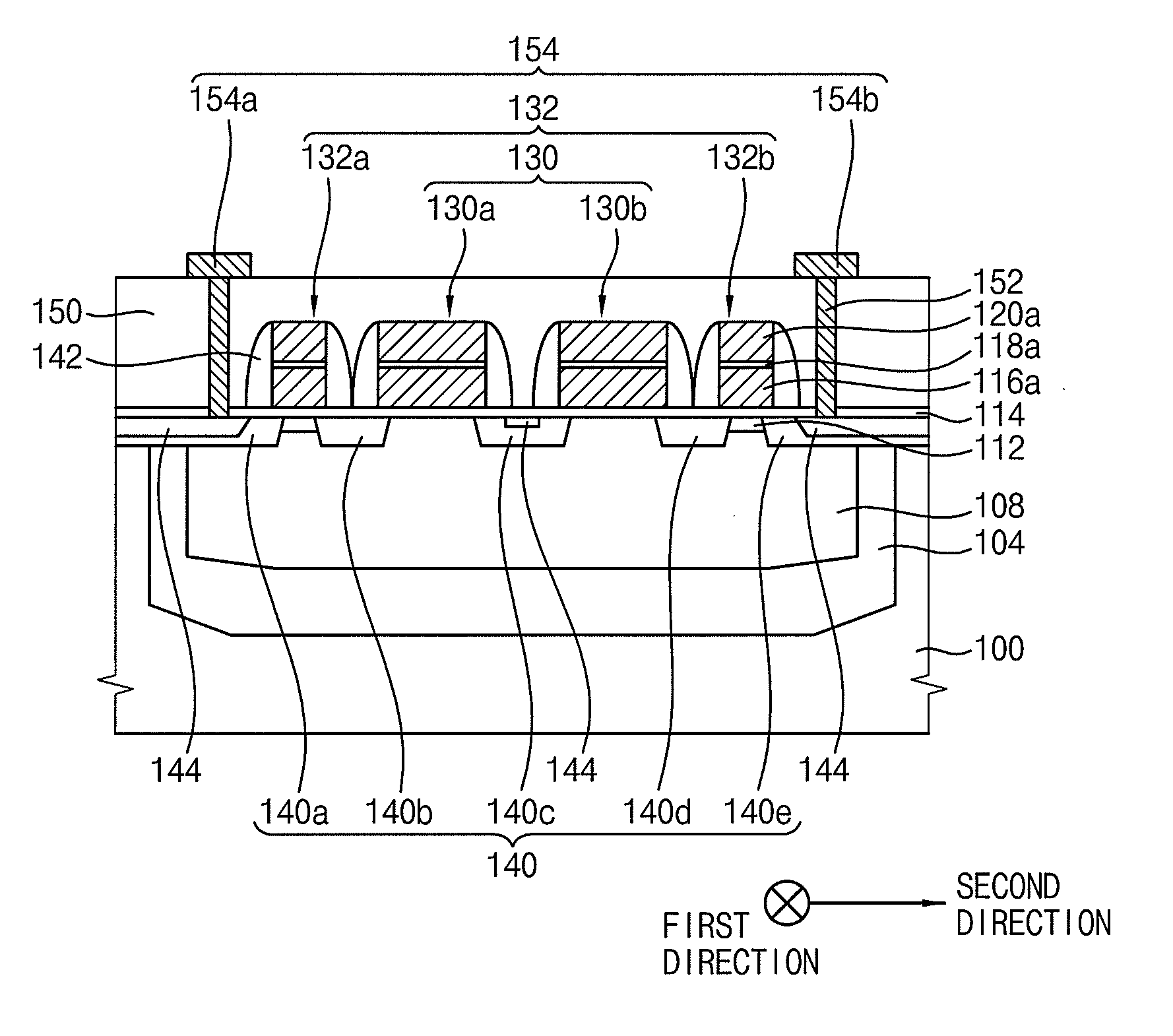

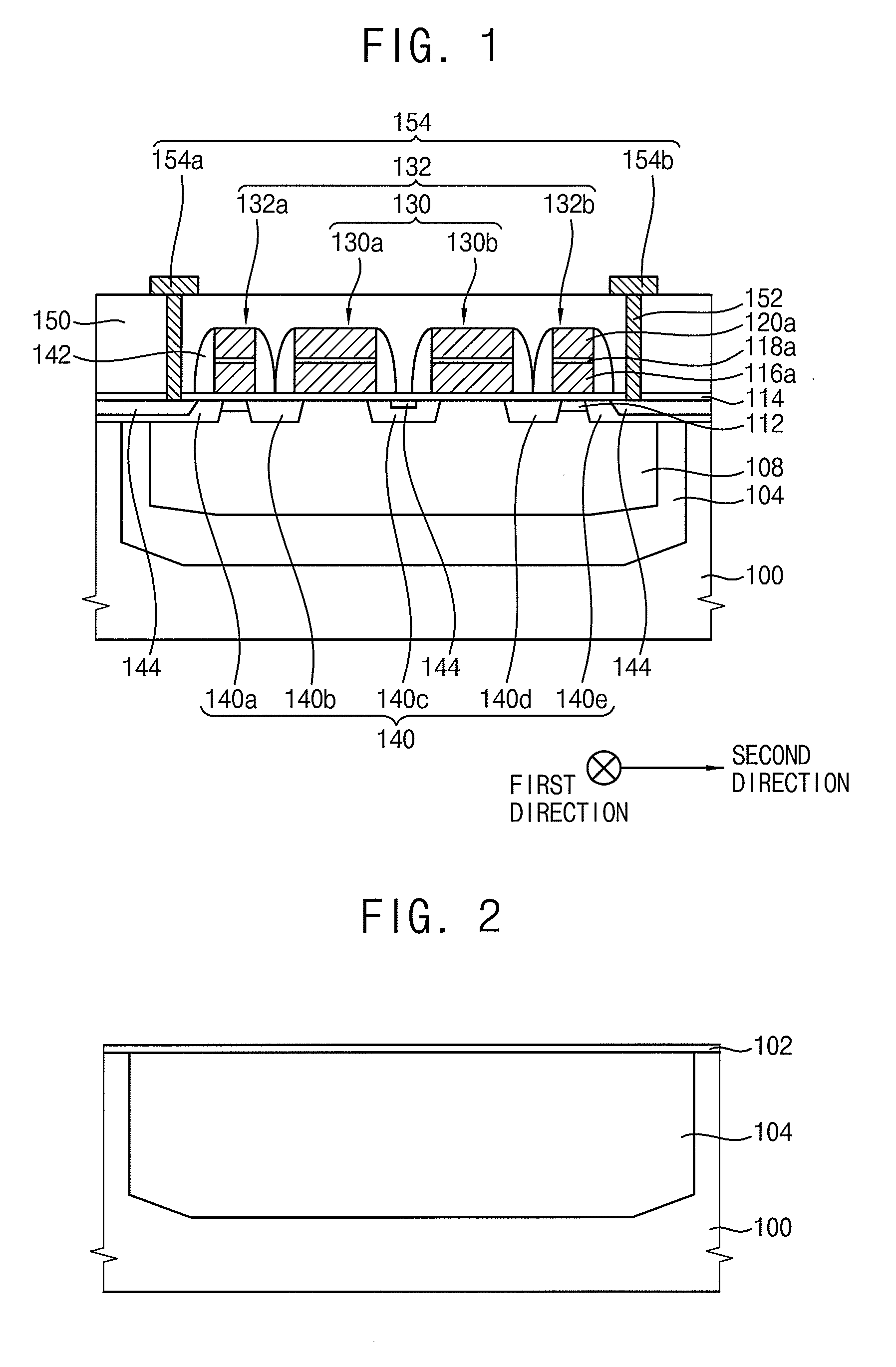

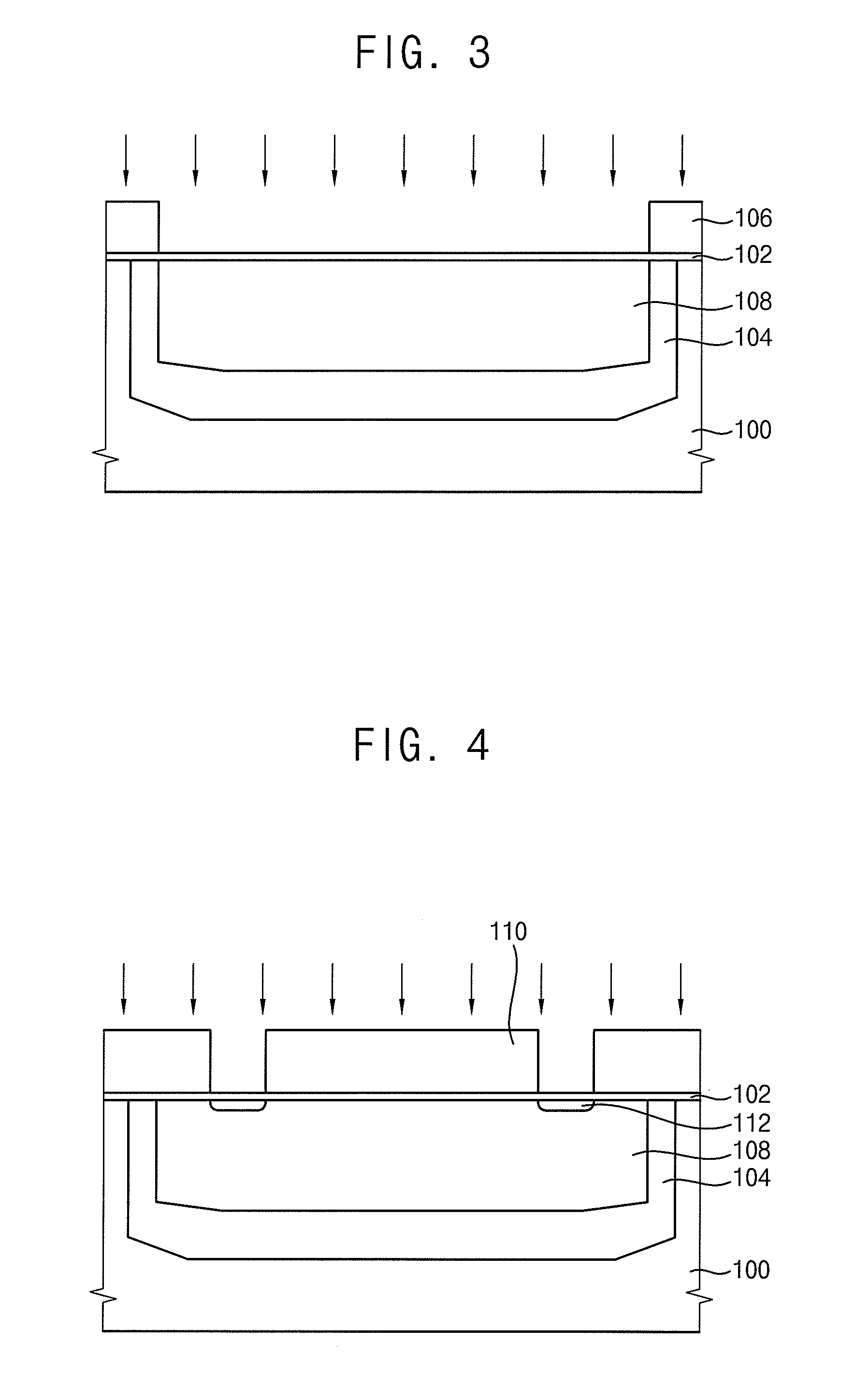

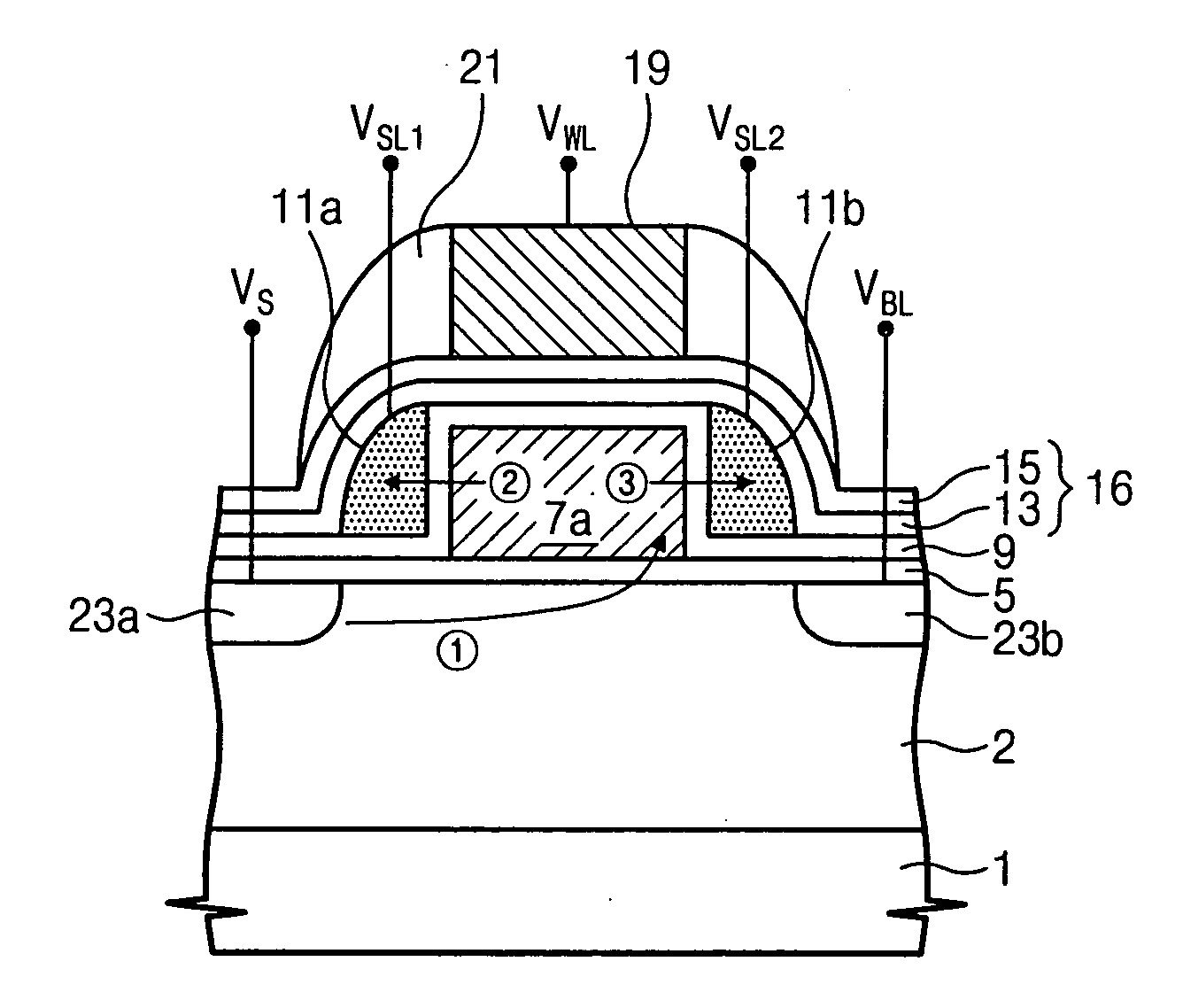

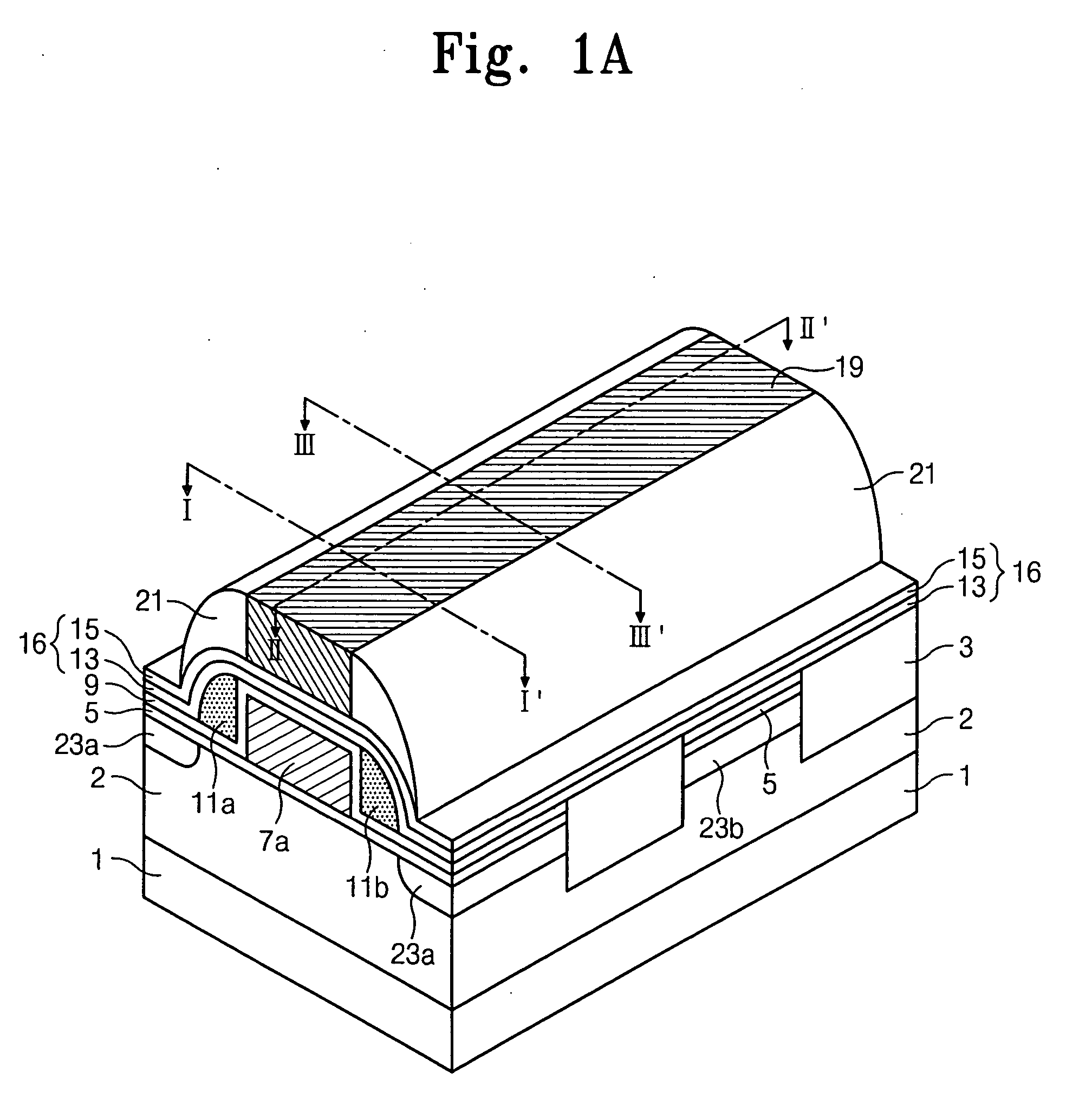

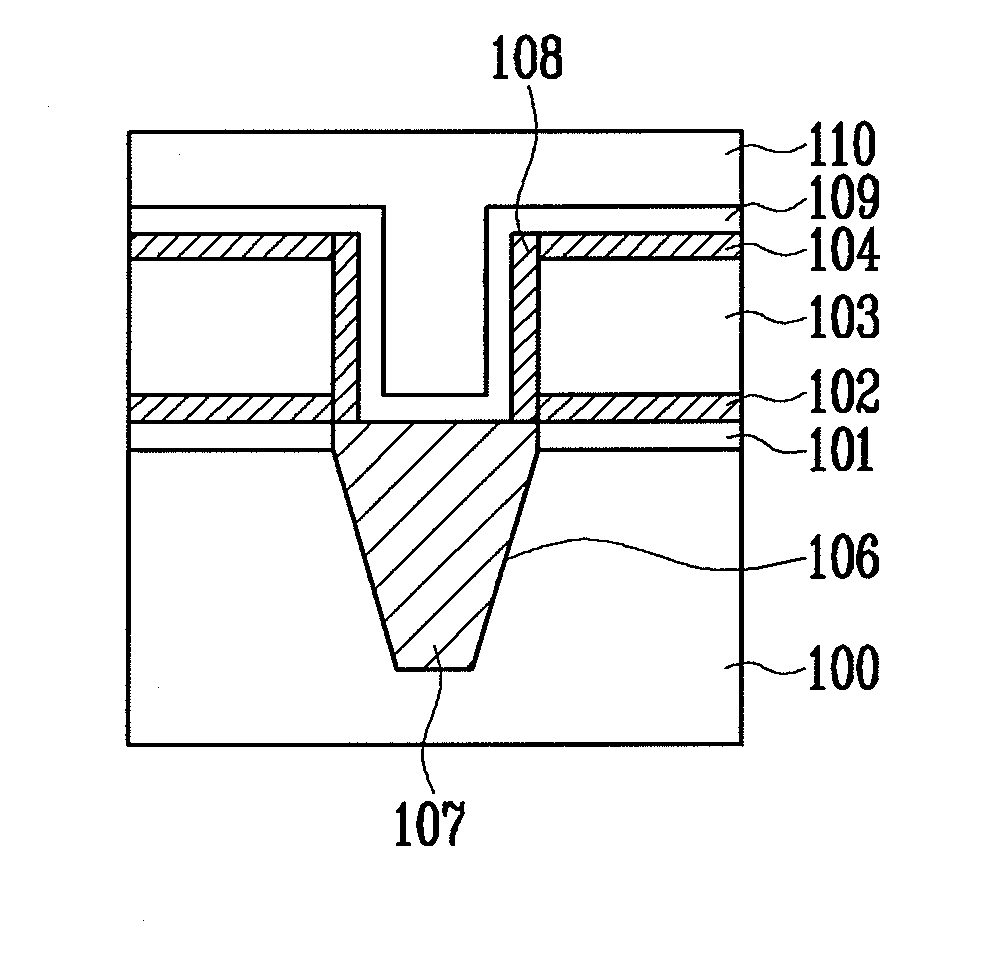

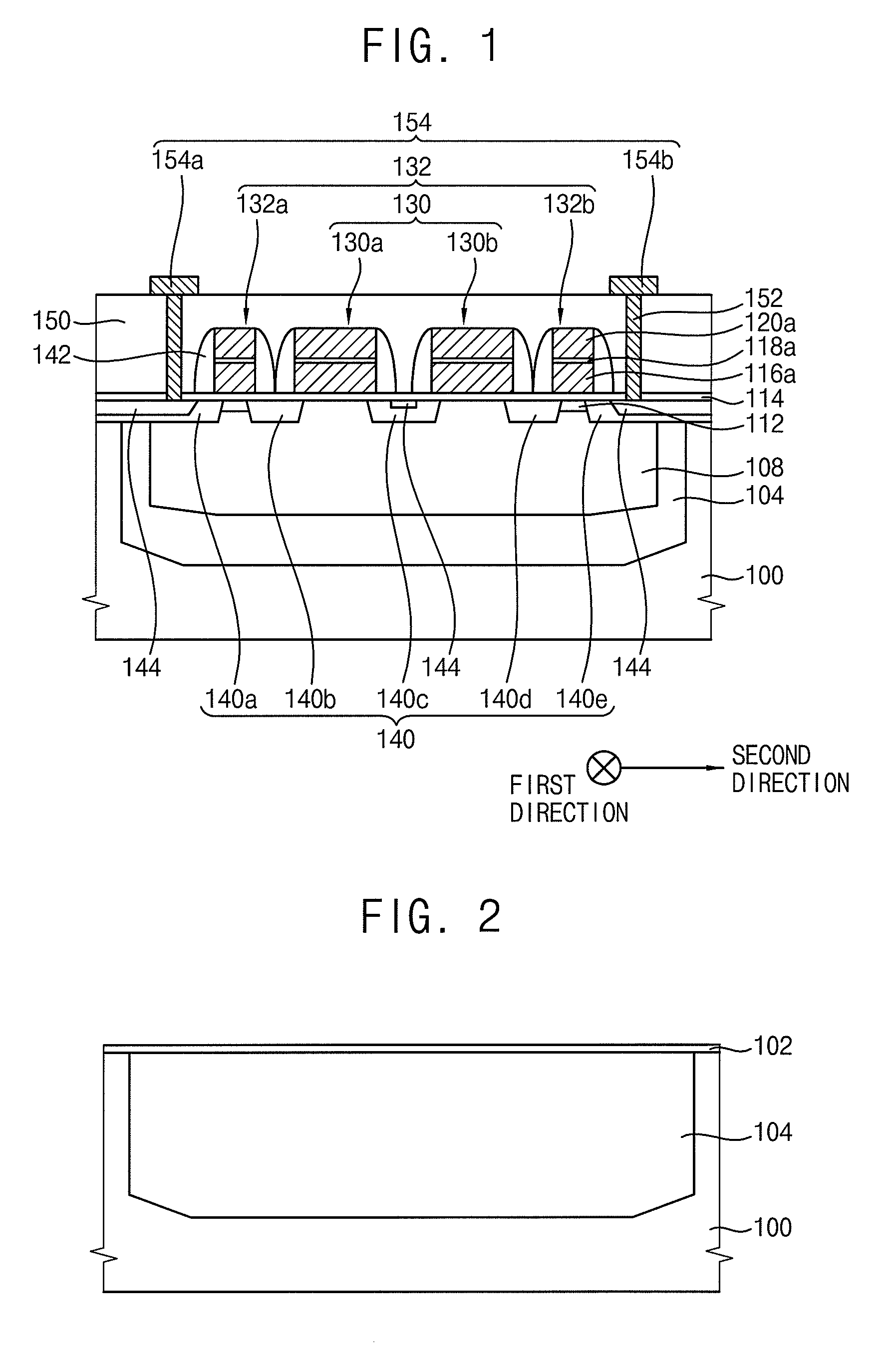

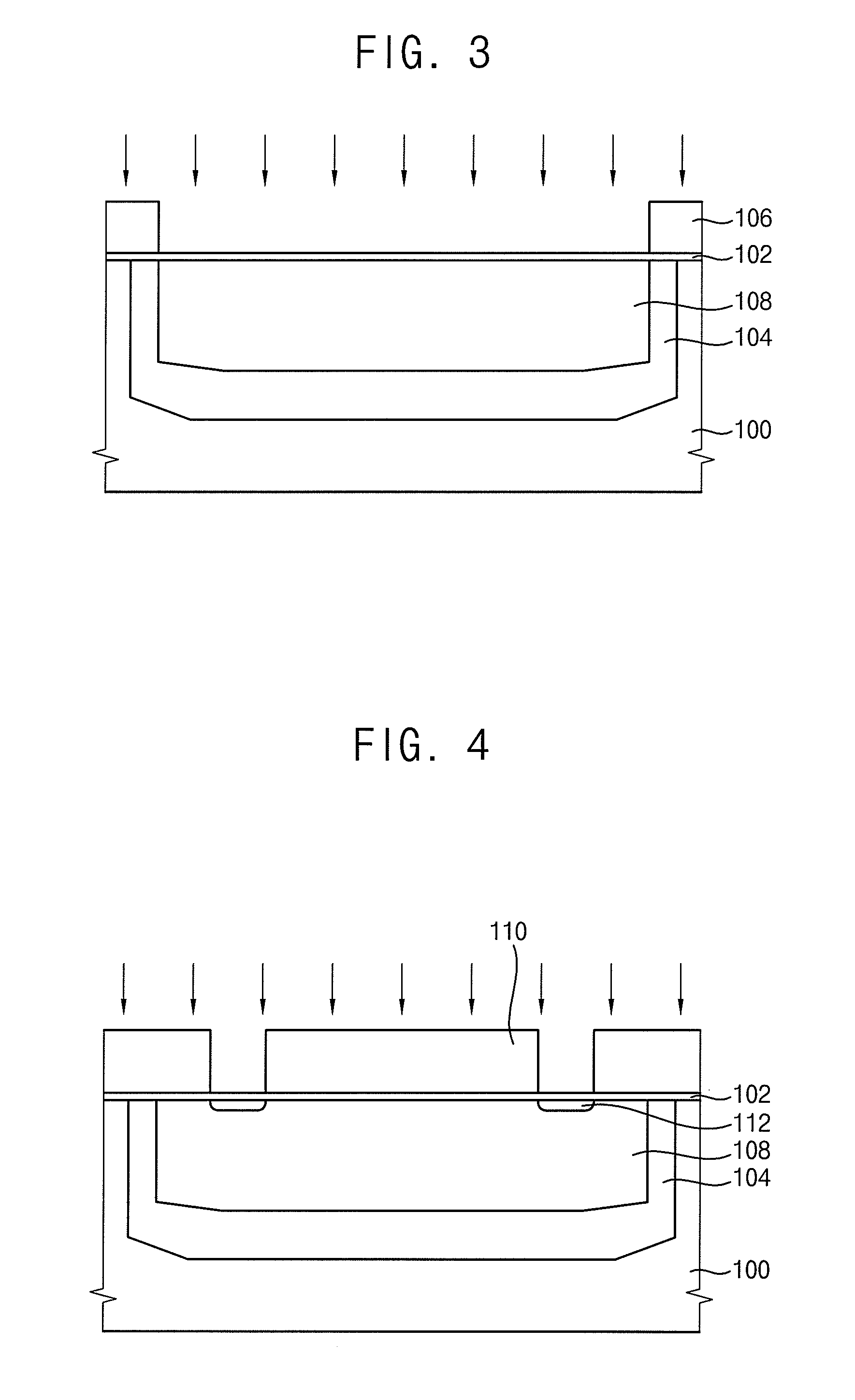

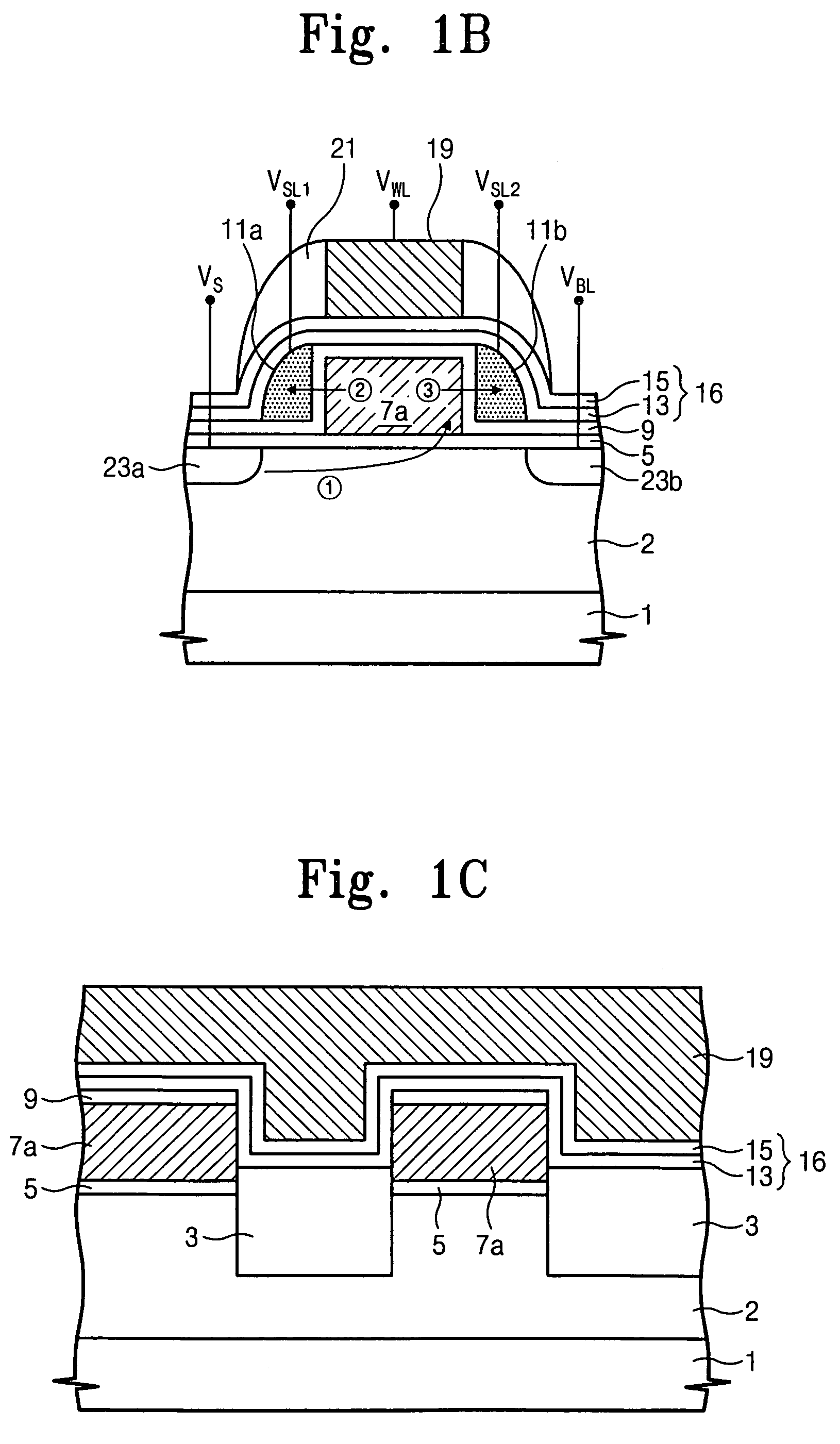

Non-volatile memory device, method of manufacturing the same and method of operating the same

InactiveUS20080089136A1Reduce disturbanceImproved Threshold Voltage DistributionTransistorSolid-state devicesEngineeringOxide

A non-volatile memory device includes a first sensing line, a first word line, a depletion channel region, and impurity regions. The first sensing line and the first word line are formed adjacent to each other in parallel on a substrate. The first sensing line and the first word line have a tunnel oxide layer, a first conductive pattern, a dielectric layer pattern and a second conductive pattern sequentially stacked on the substrate. The depletion channel region is formed at an upper portion of the substrate under the first sensing line. The impurity regions are formed at upper portions of the substrate exposed by the first sensing line and the first word line.

Owner:SAMSUNG ELECTRONICS CO LTD

Erase Method of Flash Memory Device

ActiveUS20090201728A1Improved Threshold Voltage DistributionFail occurrence ratioRead-only memoriesDigital storageVoltage rangeComputer science

Erase and program methods of a flash memory device including MLCs for increasing the program speed are described. In the erase method, MLCs are pre-programmed so that a voltage range in which threshold voltages of MLCs are distributed can be reduced. Therefore, a fail occurrence ratio can be reduced when erasing MLCs, the threshold voltage distribution of MLCs can be improved and an overall program time can be shortened in a subsequent program operation.

Owner:SK HYNIX INC

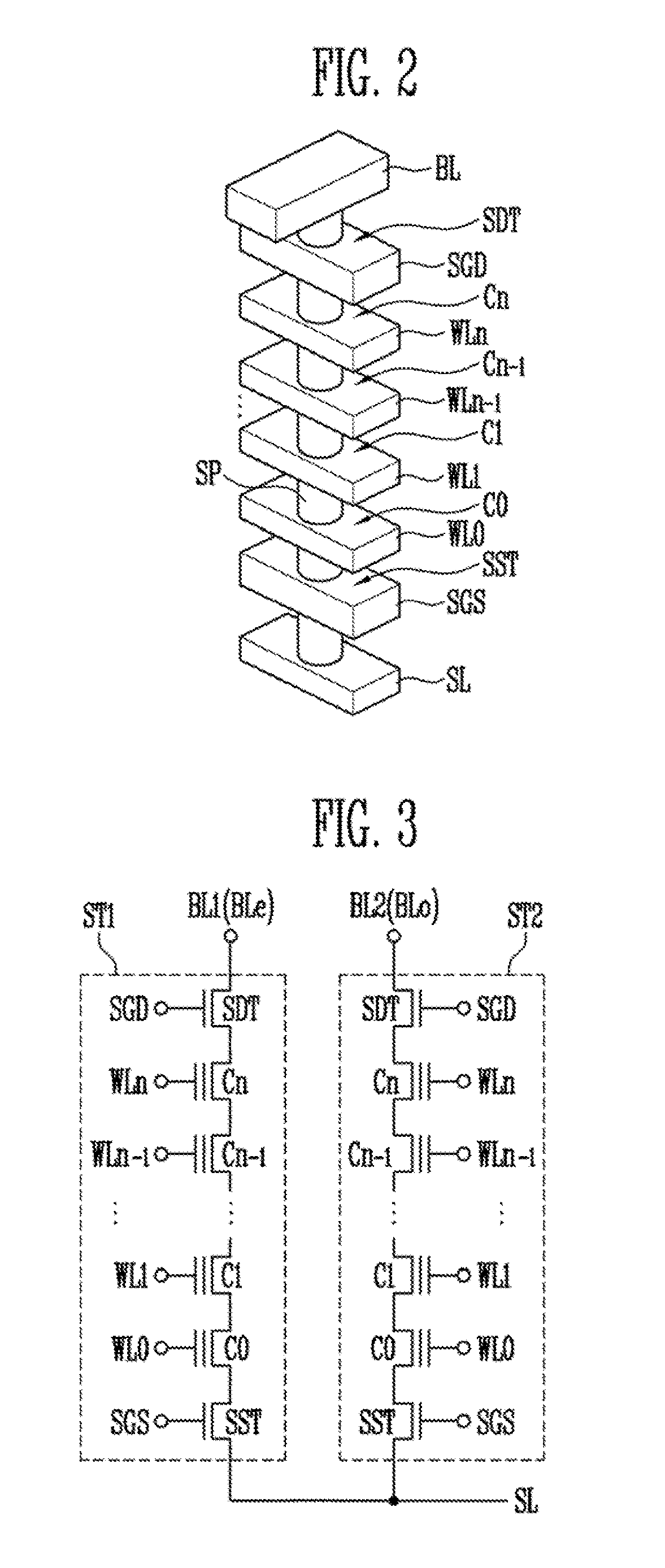

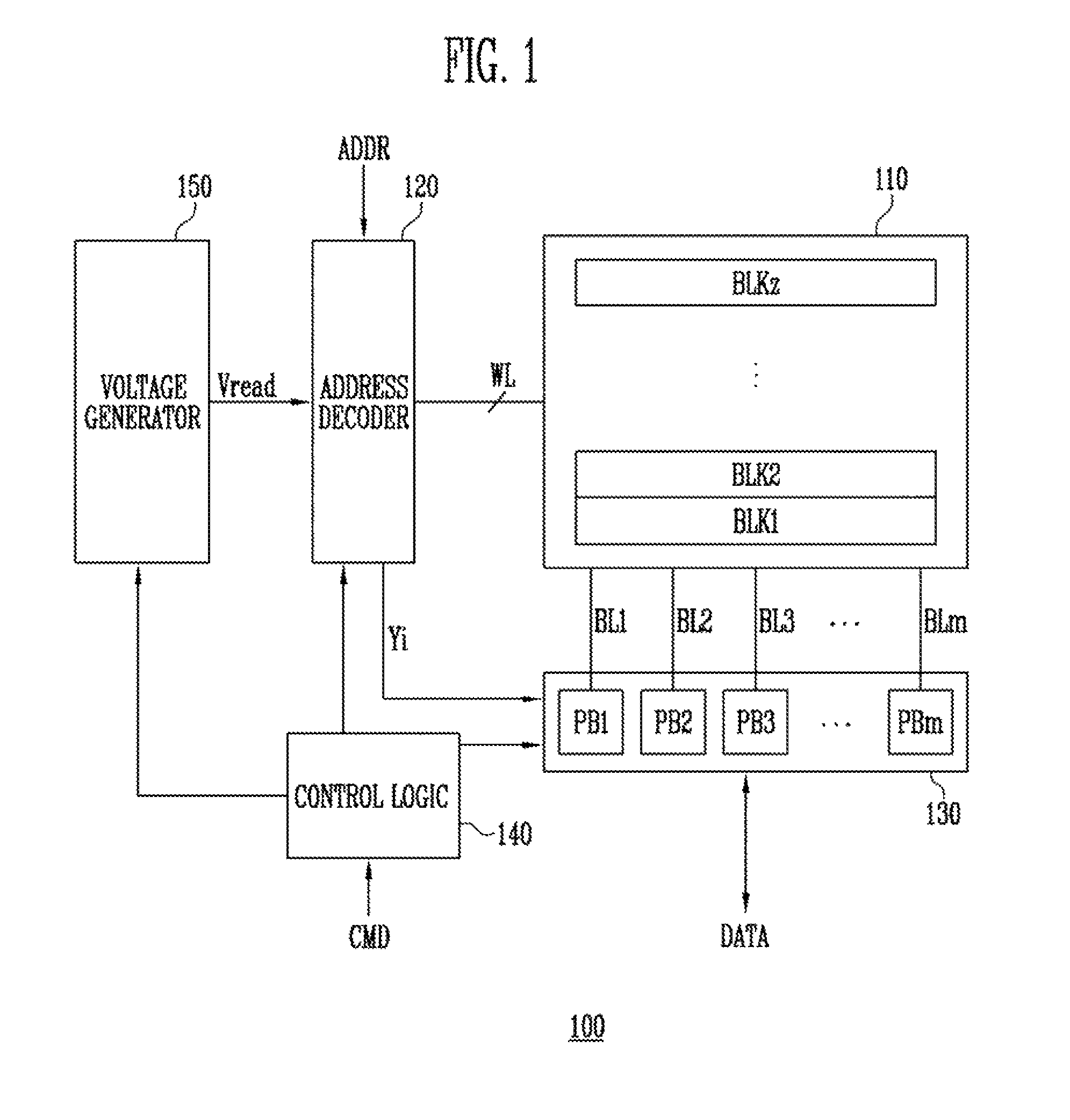

Semiconductor memory device and method of operating the same

ActiveUS20140369134A1Improved Threshold Voltage DistributionHigh data reliabilityRead-only memoriesDigital storageBit lineComputer science

A semiconductor memory device and a method of operating the same perform a program loop, including a program operation and a program verification operation based on a sub-verification voltage smaller than a target verification voltage and the target verification voltage, to the memory cells until a threshold voltage of the memory cells is greater than the target verification voltage. A positive voltage, supplied to the bit line of the memory cell of which the threshold voltage is higher than the sub-verification voltage, is increased whenever the program operation is performed, and thus a threshold voltage distribution of the memory cells may be improved.

Owner:SK HYNIX INC

Semiconductor memory device with improved program verification reliability

ActiveUS20170025184A1Raise the threshold voltageImproved Threshold Voltage DistributionRead-only memoriesStorage cellHemt circuits

A semiconductor memory device includes a memory cell array including first and second groups of memory strings respectively coupled to first and second groups of bit-lines, wherein the first and second groups of memory strings respectively include first and second groups of selection transistor cells; a peripheral circuit suitable for applying a program voltage, and performing program verification operation for the memory cell array; and a control logic suitable for controlling the peripheral circuit to perform a first program verification operation for the first group of selection transistor cells and a second program verification operation for the second group of selection transistor cells.

Owner:SK HYNIX INC

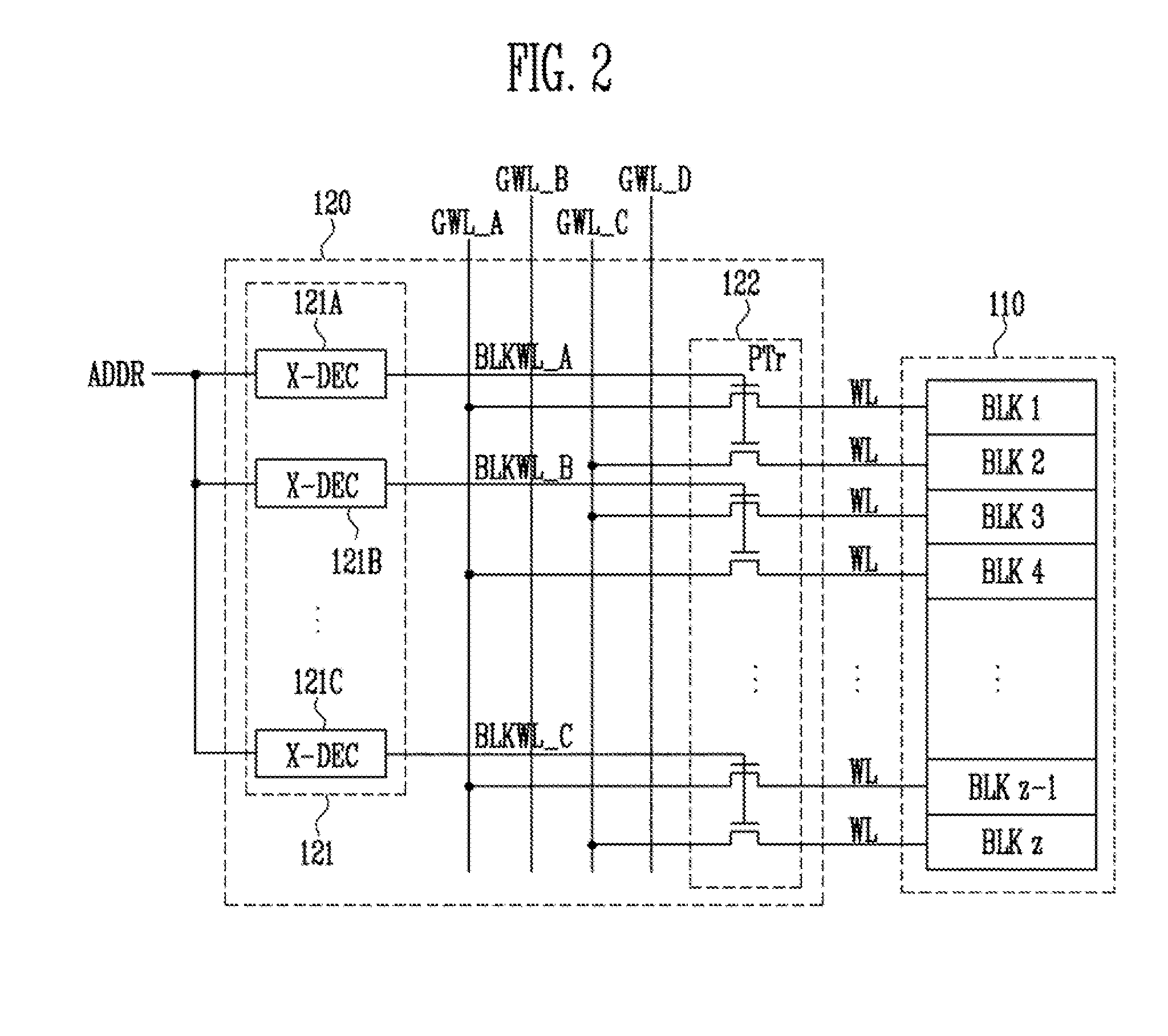

Semiconductor memory device

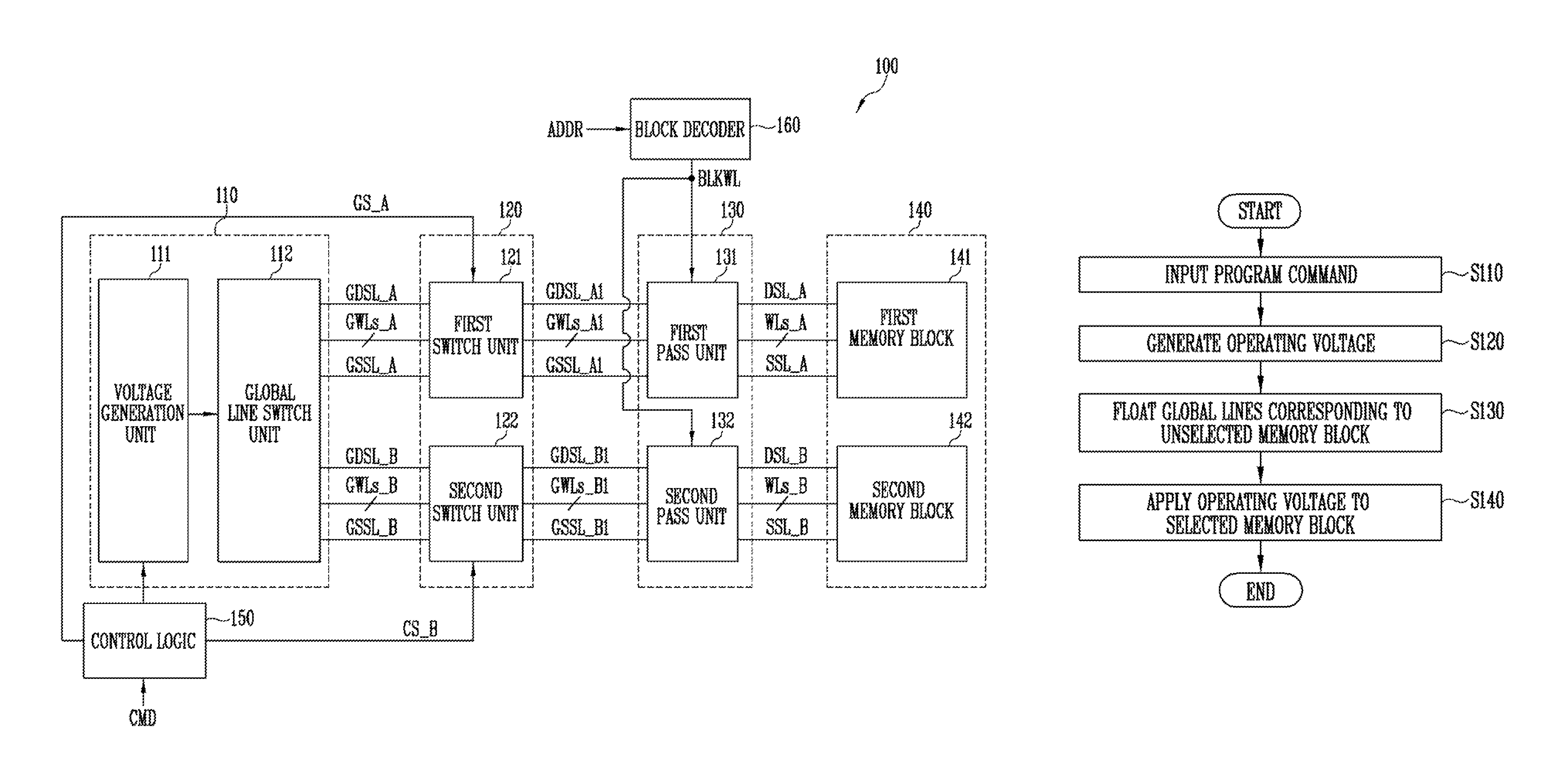

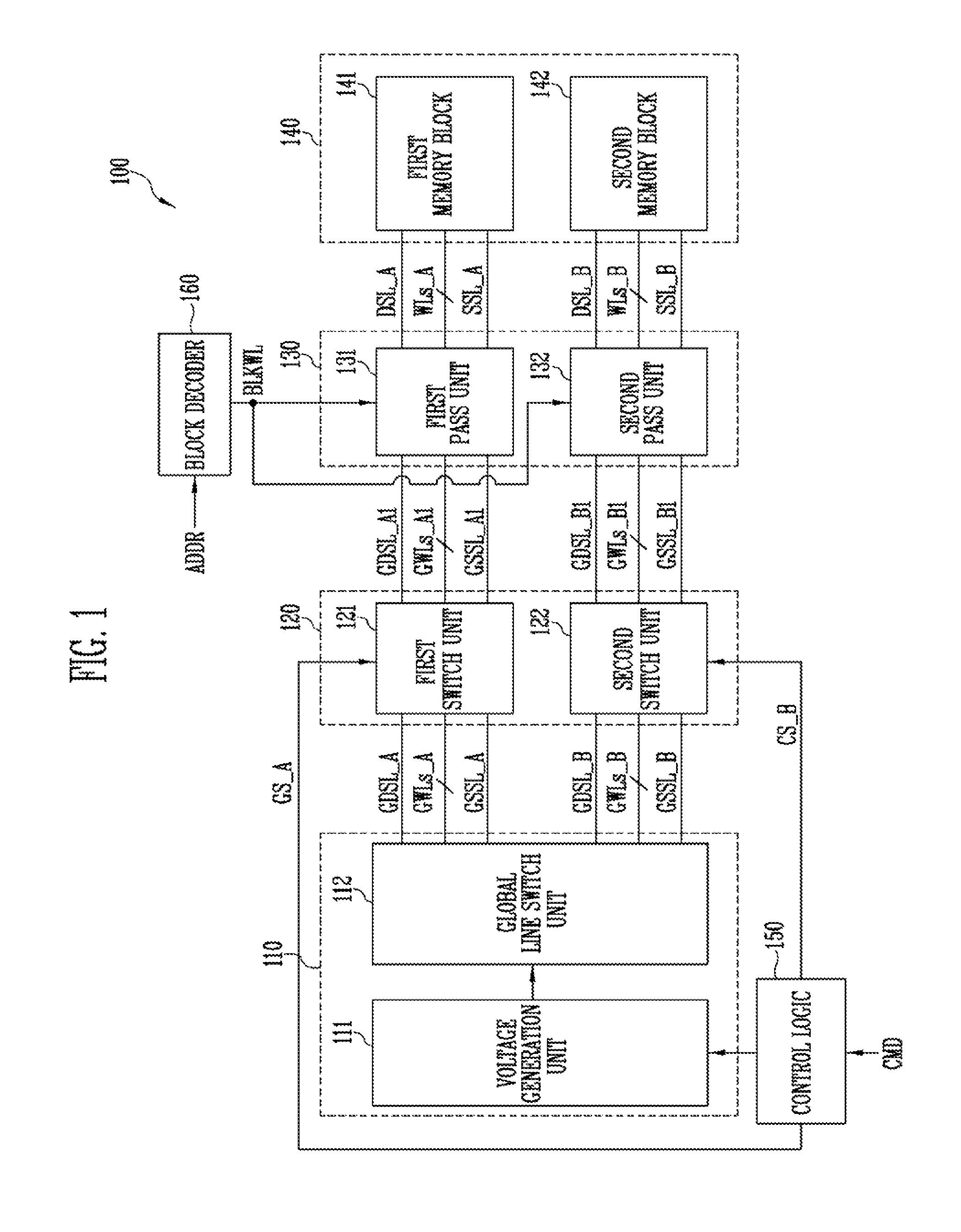

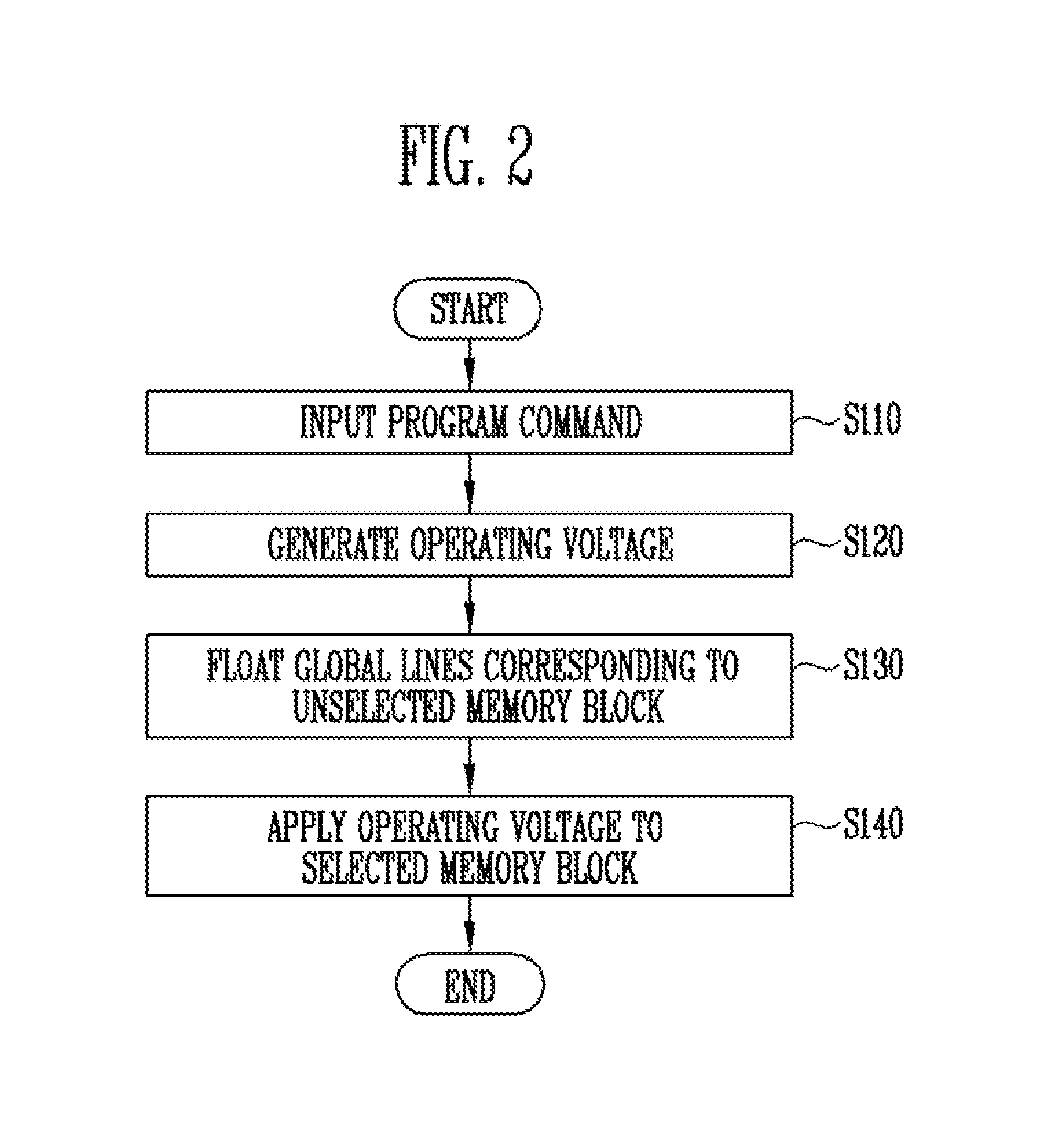

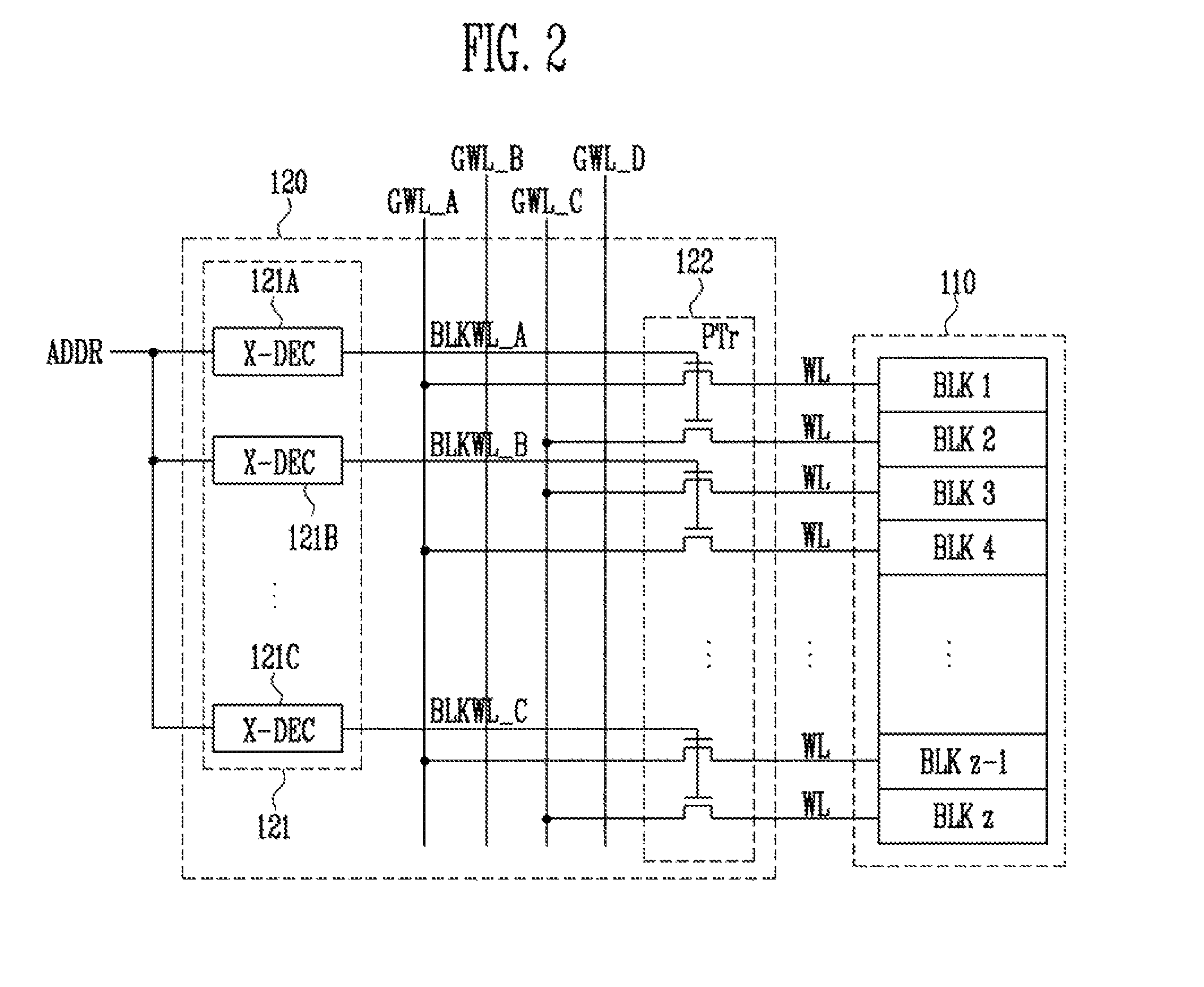

ActiveUS9472292B1Improved Threshold Voltage DistributionRead-only memoriesDigital storageControl signalHemt circuits

A semiconductor memory device includes a memory unit including a first memory block and a second memory block, a power supply unit suitable for applying a plurality of operating voltages to one of first global lines or second global lines, a switching circuit suitable for switching the first global lines and first internal global lines in response to a first control signal and switching the second global lines and second internal global lines in response to a second control signal, and a pass circuit suitable for electrically connecting the first internal global lines to word lines and selection lines of the first memory block and electrically connecting the second internal global lines to word lines and selection lines of the second memory block in response to a block selection signal.

Owner:SK HYNIX INC

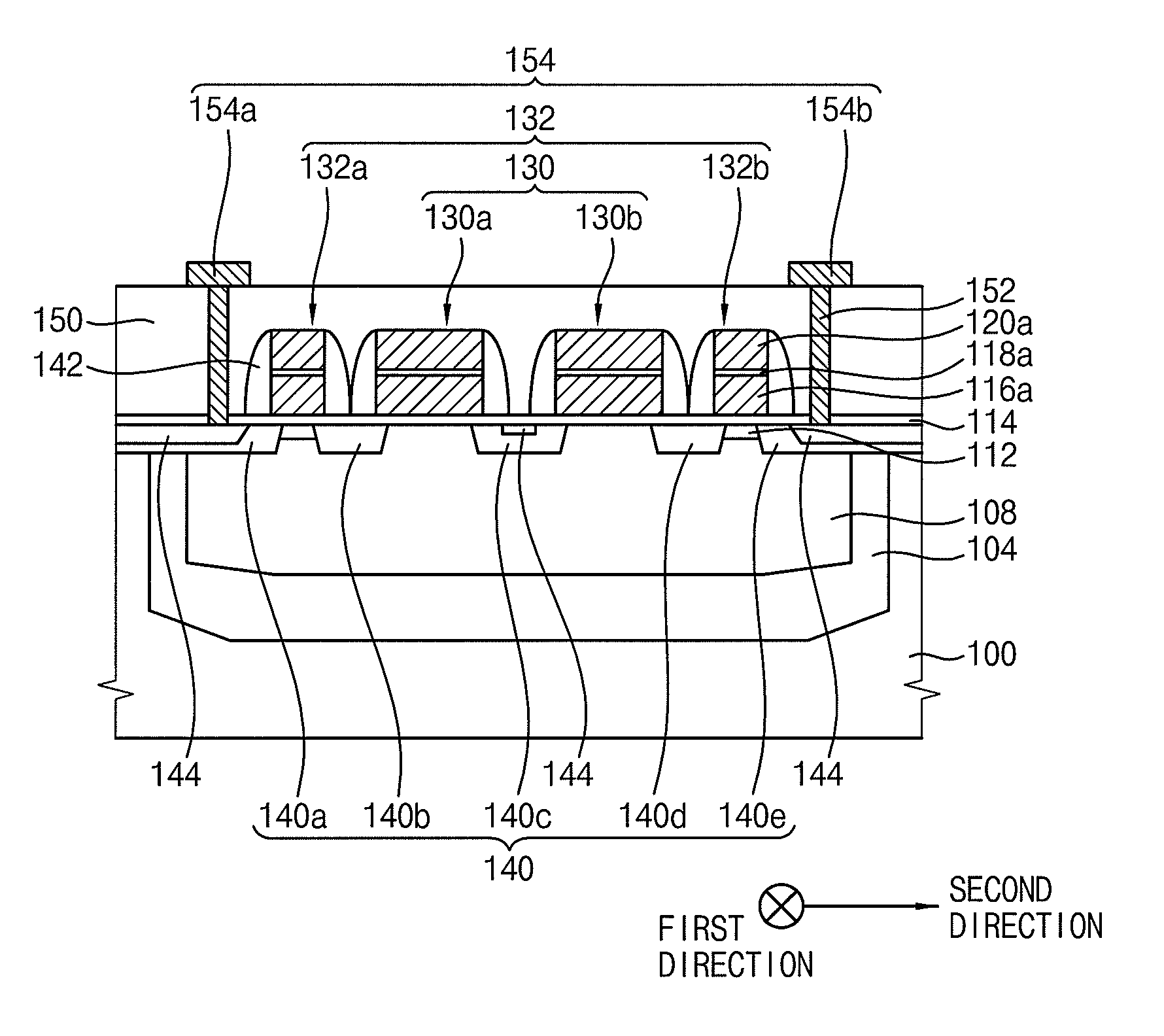

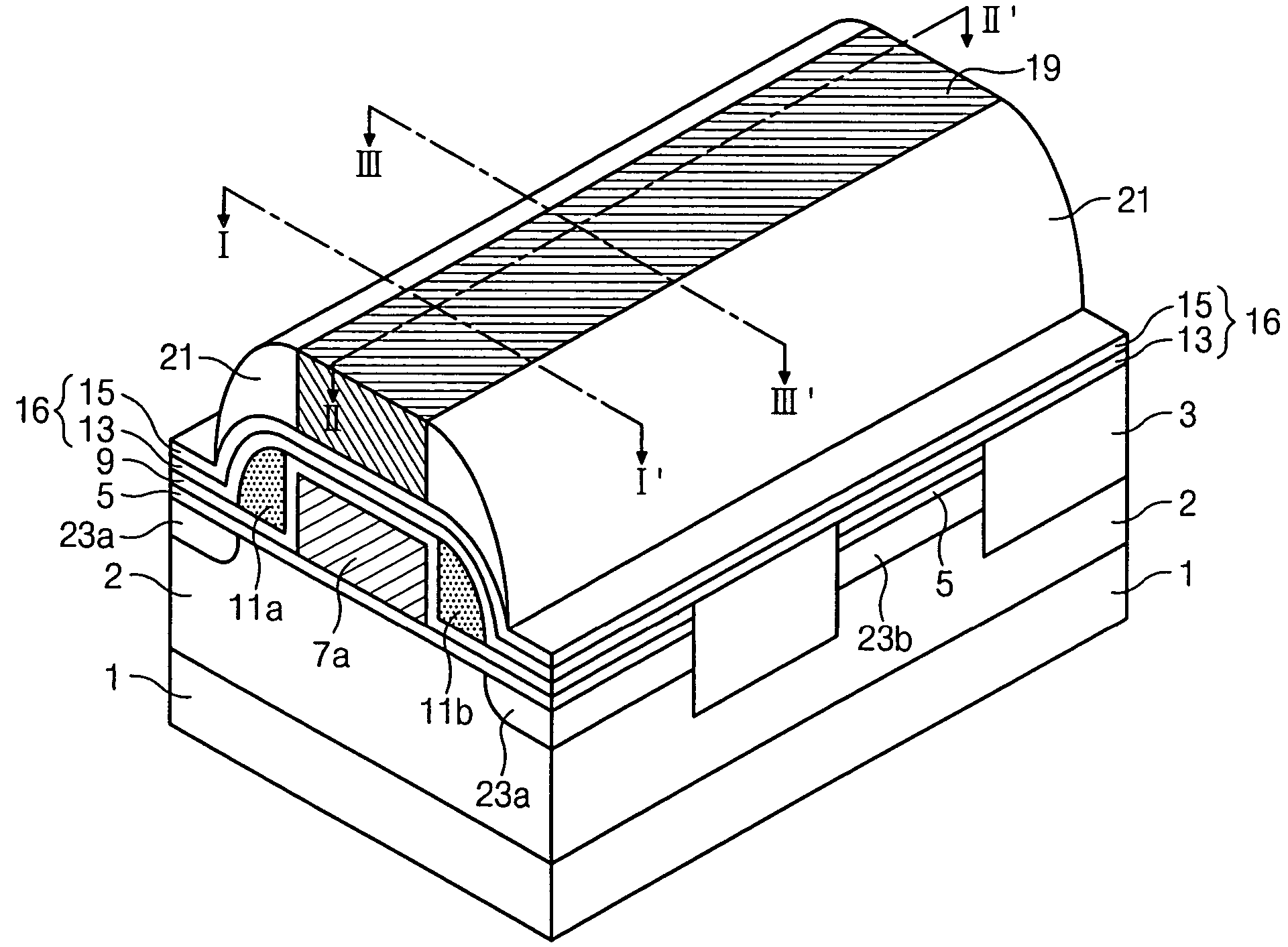

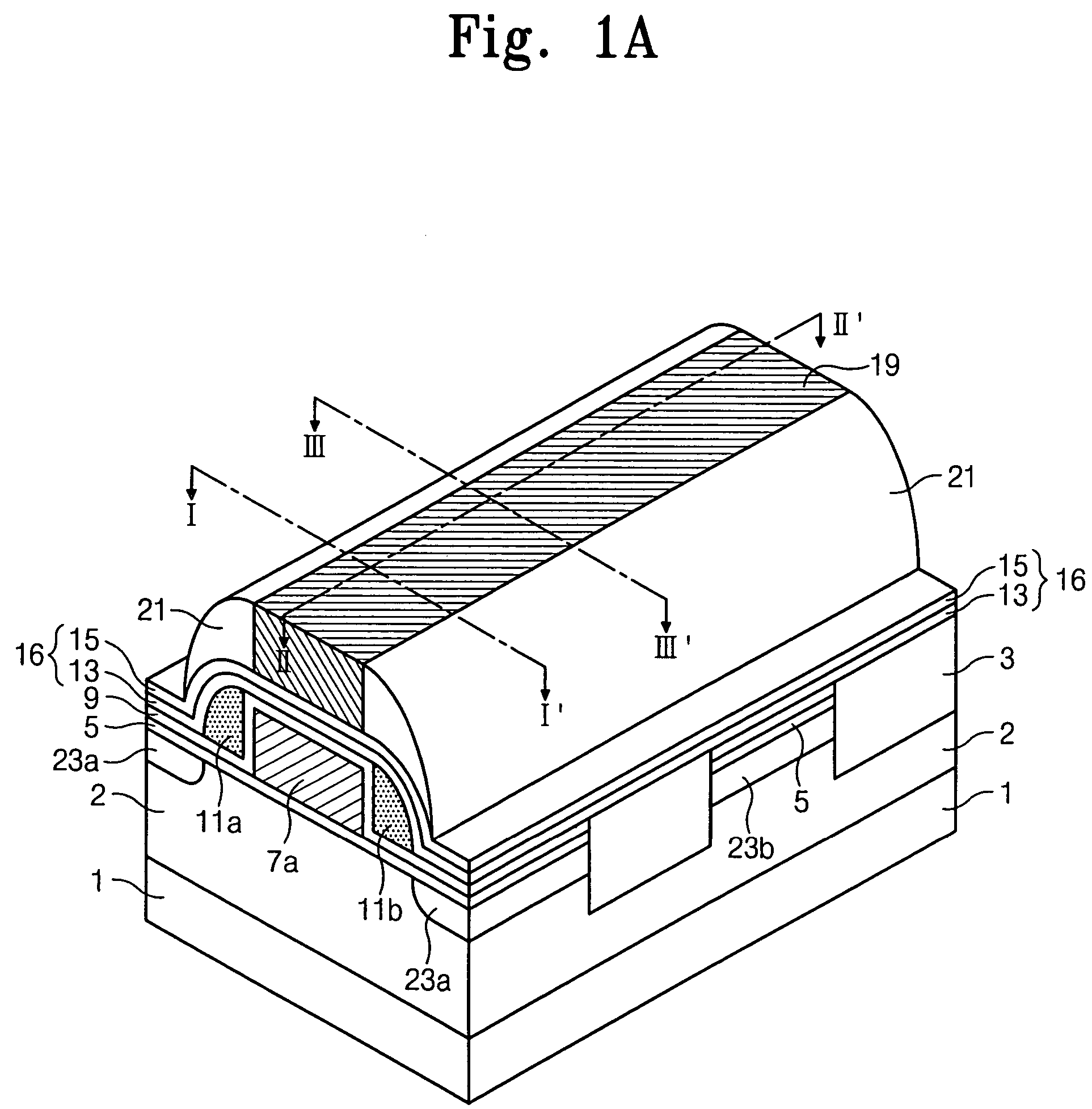

Non-volatile memory device and methods of forming and operating the same

ActiveUS20070023820A1Improved Threshold Voltage DistributionHigh degreeTransistorSolid-state devicesEngineeringThreshold voltage

In a non-volatile memory device and methods of forming and operating the same, one memory transistor includes sidewall selection gates covering both sidewalls of a floating gate when the floating gate and a control gate are stacked. The sidewall selection gates are in a spacer form. Since the sidewall selection gates are in a spacer form on the sidewall of the floating gate, the degree of integration of cells can be improved. Additionally, since the side wall selection gates are disposed on both sidewalls of the floating gate, a voltage applied from a bit line and a common source line can be controlled and thus conventional writing / erasing errors can be prevented. Therefore, distribution of threshold voltage can be improved.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor memory device improving threshold voltage of unselected memory block and operating method thereof

ActiveUS9466372B2Improved Threshold Voltage DistributionRead-only memoriesSemiconductorThreshold voltage

Owner:SK HYNIX INC

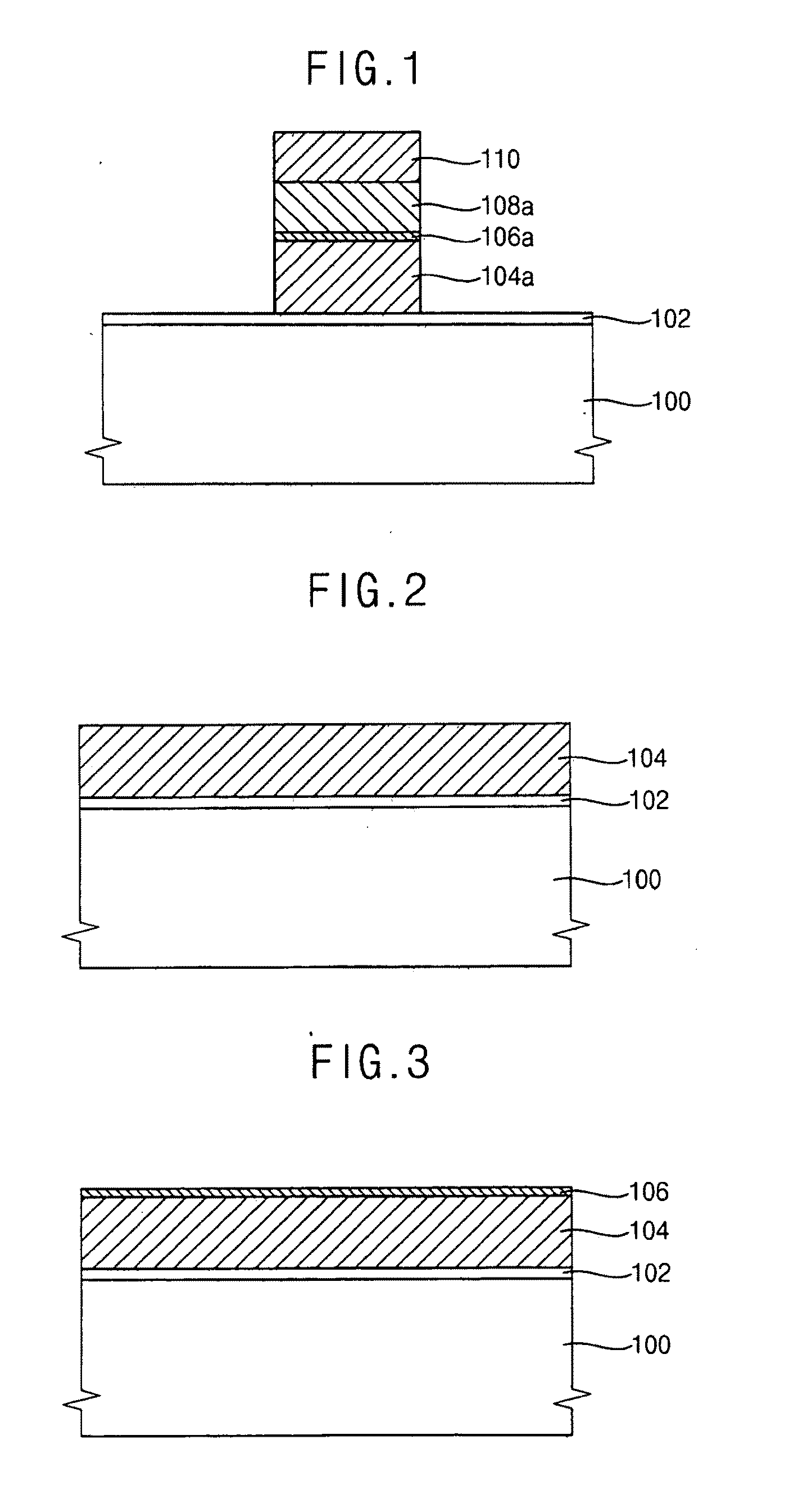

Method of Forming Gate Electrode

InactiveUS20090181528A1Improved Threshold Voltage DistributionWriting connectorsWriting accessoriesSilanesAmorphous silicon

The present invention discloses to a method of forming a gate electrode, the method according to the present invention comprises the steps of forming a lower amorphous silicon layer using silane (SiH4) gas and nitrous oxide (N2O) gas; forming an upper amorphous silicon layer on the lower amorphous silicon layer; and crystallizing the lower and upper amorphous silicon layers through a thermal process.

Owner:SK HYNIX INC

Semiconductor memory device with improved program verification reliability

ActiveUS20180130540A1Improved Threshold Voltage DistributionRead-only memoriesBit lineProgram proving

A semiconductor memory device includes a memory cell array including first and second groups of memory strings respectively coupled to first and second groups of bit-lines, wherein the first and second groups of memory strings respectively include first and second groups of selection transistor cells; a peripheral circuit suitable for applying a program voltage, and performing program verification operation for the memory cell array; and a control logic suitable for controlling the peripheral circuit to perform a first program verification operation for the first group of selection transistor cells and a second program verification operation for the second group of selection transistor cells.

Owner:SK HYNIX INC

Semiconductor memory device and operating method thereof

ActiveUS20160148690A1Improved Threshold Voltage DistributionRead-only memoriesDigital storageSemiconductorPeripheral

The present invention relates to a semiconductor memory device and an operating method thereof. The semiconductor memory device may include at least two memory blocks sharing a row decoder, and a peripheral circuit performing a read operation on a selected memory block, between the at least two memory blocks, wherein the peripheral circuit applies a discharge voltage to an unselected memory block, between the at least two memory blocks, for a preset time after a period in which a read voltage is applied to the selected memory block is terminated.

Owner:SK HYNIX INC

Semiconductor memory device and method of operating the same

InactiveUS20140056075A1Raise the threshold voltageImproved Threshold Voltage DistributionRead-only memoriesDigital storageControl circuitComputer science

A semiconductor memory device and a method of operating the same are disclosed. The semiconductor memory device includes a memory cell array configured to include memory cells, a peripheral circuit configured to perform an erase operation and a soft program operation and a control circuit configured to control the peripheral circuit so that the memory cells are programmed though a hot carrier injection HCI method when the soft program operation is performed.

Owner:SK HYNIX INC

Semiconductor memory device and method of operating the same

ActiveUS8982638B2Improved Threshold Voltage DistributionHigh data reliabilityRead-only memoriesDigital storageBit lineComputer science

A semiconductor memory device and a method of operating the same perform a program loop, including a program operation and a program verification operation based on a sub-verification voltage smaller than a target verification voltage and the target verification voltage, to the memory cells until a threshold voltage of the memory cells is greater than the target verification voltage. A positive voltage, supplied to the bit line of the memory cell of which the threshold voltage is higher than the sub-verification voltage, is increased whenever the program operation is performed, and thus a threshold voltage distribution of the memory cells may be improved.

Owner:SK HYNIX INC

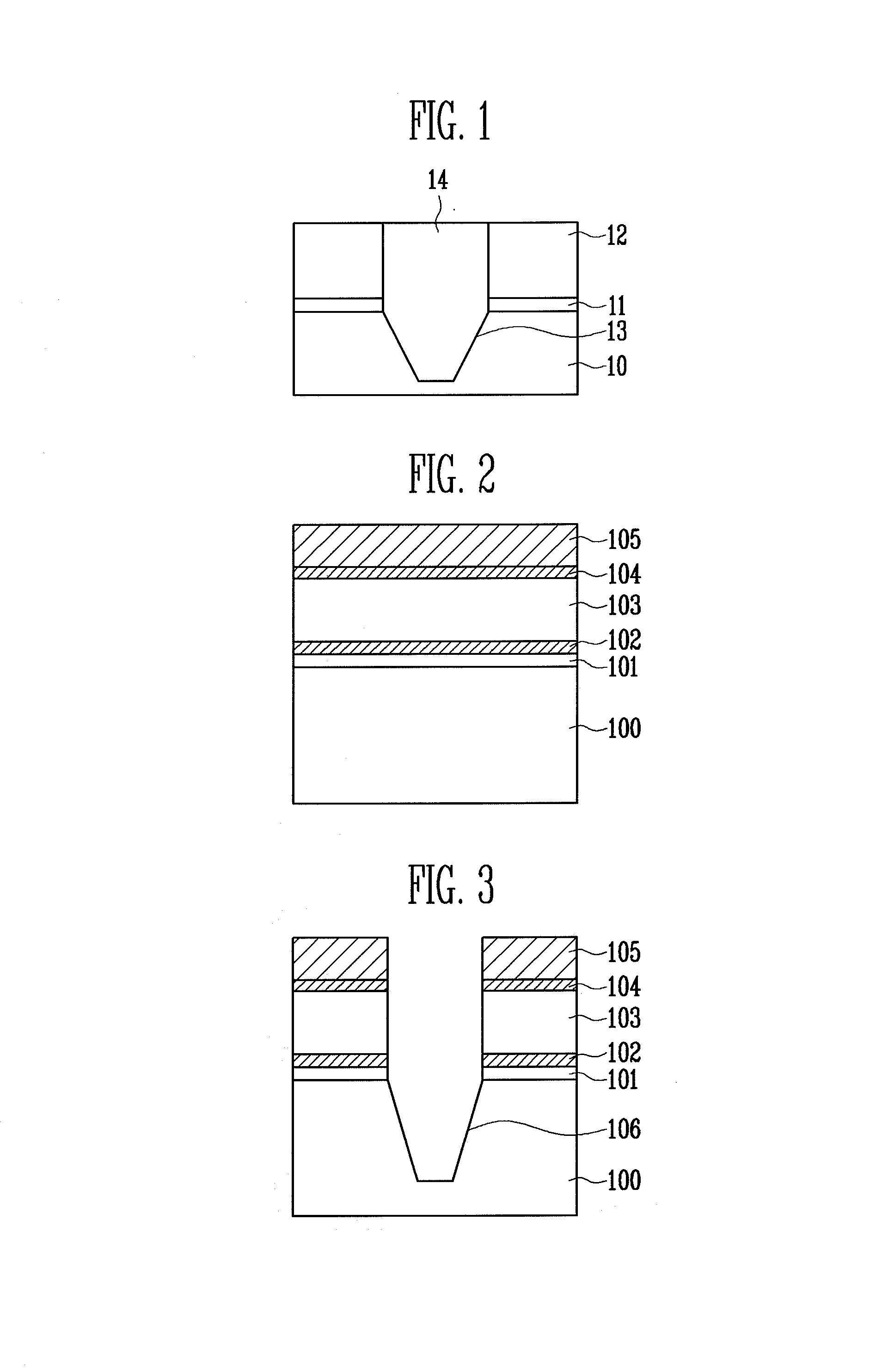

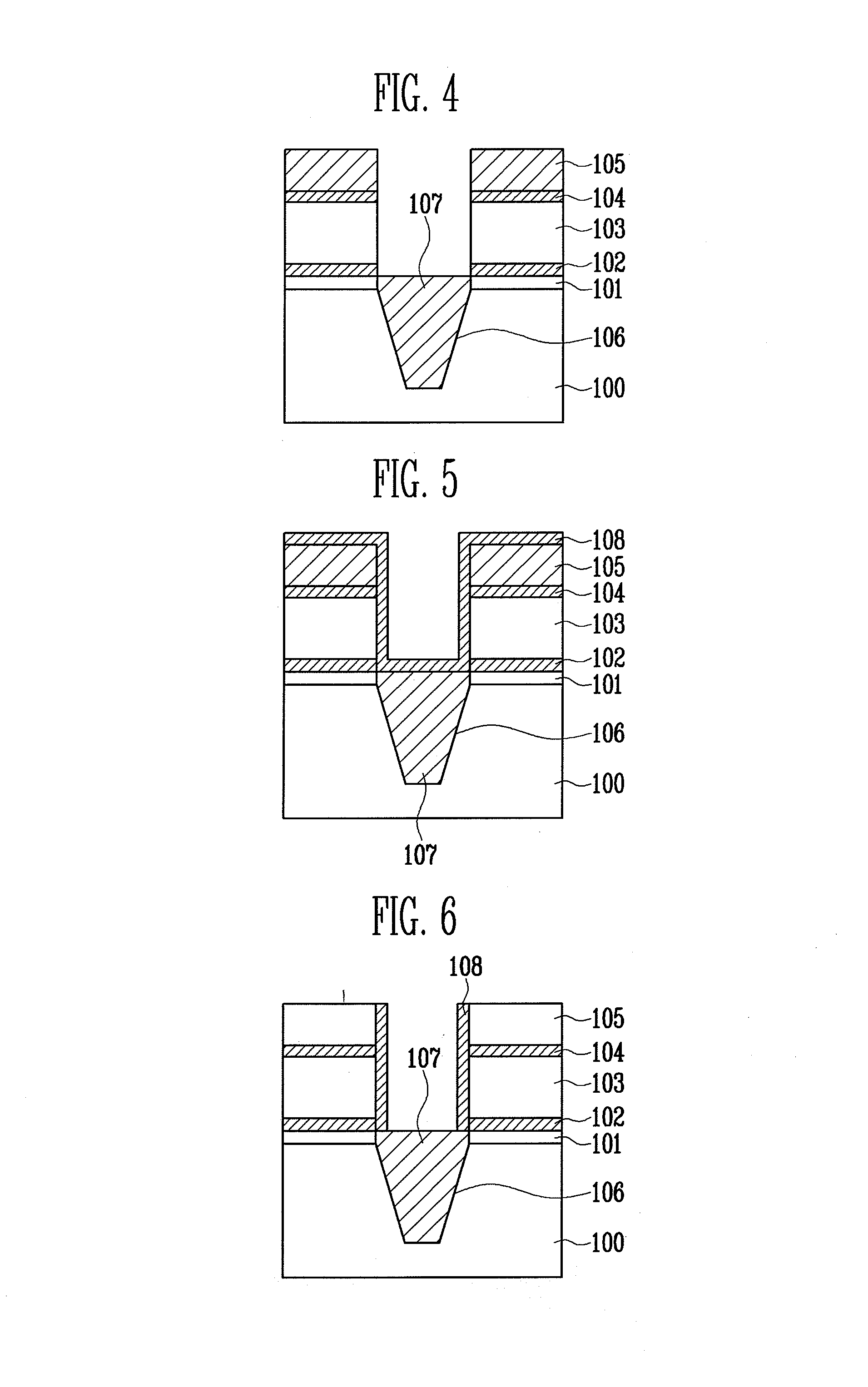

Semiconductor memory device and method of fabricating the same

InactiveUS20090140319A1Improved Threshold Voltage DistributionEnhancing yield and reliabilityTransistorNanoinformaticsEngineeringGap filling

A semiconductor memory devices and a method of fabricating the same includes sequentially stacking a tunnel insulating layer, a first nano-grain film, a conductive layer for a floating gate, and a second nano-grain film over a semiconductor substrate, forming a trench by etching the second nano-grain film, the conductive layer for the floating gate, the first nano-grain film, the tunnel insulating layer, and the semiconductor substrate, gap-filling the trench with an insulating layer, thus forming an isolation layer, and forming a third nano-grain film on sidewalls of the conductive layer for the floating gate.

Owner:SK HYNIX INC

Memory device and operating method thereof

ActiveUS20220139461A1Improve threshold voltage distributionImproved Threshold Voltage DistributionRead-only memoriesDigital storageHemt circuitsElectrical and Electronics engineering

There are provided a memory device and an operating method thereof. The memory device includes: a memory block including a plurality of memory cells and a plurality of select transistors; a peripheral circuit for performing a program operation on selected select transistors among the plurality of select transistors in a select transistor program operation; and a control logic for controlling the peripheral circuit to perform the select transistor program operation. The peripheral circuit applies a coupling voltage having a positive potential to a source line of the memory block in the select transistor program operation.

Owner:SK HYNIX INC

Nonvolatile memory and related reprogramming method

InactiveUS20160141036A1Improve programming speedImproved Threshold Voltage DistributionMemory architecture accessing/allocationMemory adressing/allocation/relocationOperating systemPage buffers

A method of reprogramming a nonvolatile memory device, comprising setting up bit lines of selected memory cells according to logic values of first and second latches of a page buffer connected to the bit lines, supplying a program pulse to the selected memory cells, performing a program verify operation on the selected memory cells using the first and second latches, and performing a predictive program operation on the selected memory cells according to a result of the program verify operation. In the predictive program operation, bit lines of the selected memory cells are setup according to a logic value of a third latch of the page buffer that corresponds to each of the selected memory cells.

Owner:SAMSUNG ELECTRONICS CO LTD

Semiconductor memory device and method of operating the same

ActiveUS20150213902A1Improved Threshold Voltage DistributionRead-only memoriesDigital storageControl circuitComputer science

A semiconductor memory device and a method of operating the same are disclosed. The semiconductor memory device includes a memory cell array configured to include memory cells, a peripheral circuit configured to perform an erase operation and a soft program operation and a control circuit configured to control the peripheral circuit so that the memory cells are programmed though a hot carrier injection HCI method when the soft program operation is performed.

Owner:SK HYNIX INC

Soft program method in a non-volatile memory device

InactiveCN101364443BImproved Threshold Voltage DistributionImprove read marginRead-only memoriesComputer scienceStorage cell

A soft program method in a non-volatile memory device for performing a soft program step so as to improve threshold voltage distribution of an erased cell is disclosed. The soft program method in a non-volatile memory device includes performing a soft program for increasing threshold voltages of memory cells by a given level, wherein an erase operation is performed about the memory cells, performing a verifying operation for verifying whether or not a cell programmed to a voltage more than a verifying voltage is existed in each of cell strings, and performing repeatedly the soft program untilit is verified that whole cell strings have one or more cell programmed to the voltage more than the verifying voltage.

Owner:SK HYNIX INC

Non-volatile memory device, method of manufacturing the same and method of operating the same

InactiveUS7696561B2Improved Threshold Voltage DistributionIncreased durabilityTransistorSolid-state devicesEngineeringDielectric layer

A non-volatile memory device includes a first sensing line, a first word line, a depletion channel region, and impurity regions. The first sensing line and the first word line are formed adjacent to each other in parallel on a substrate. The first sensing line and the first word line have a tunnel oxide layer, a first conductive pattern, a dielectric layer pattern and a second conductive pattern sequentially stacked on the substrate. The depletion channel region is formed at an upper portion of the substrate under the first sensing line. The impurity regions are formed at upper portions of the substrate exposed by the first sensing line and the first word line.

Owner:SAMSUNG ELECTRONICS CO LTD

Memory device and an operating method of a memory device

A memory device and an operating method of the memory device is disclosed. The memory device includes a memory cell array including a plurality of memory blocks. The memory device further includes a peripheral circuit for performing an erase voltage application operation, a first erase verify operation, and a second erase verify operation on a selected memory block among the plurality of memory blocks. The memory device also includes a control logic for setting a start erase voltage of an erase operation, based on a result of the first erase verify operation, and controlling the peripheral circuit to perform the second erase verify operation when it is determined that the first erase verify operation on the selected memory block has been passed.

Owner:SK HYNIX INC

Non-volatile memory device and methods of forming and operating the same

ActiveUS7495281B2Improved Threshold Voltage DistributionHigh degreeTransistorSolid-state devicesThreshold voltageNon-volatile memory

In a non-volatile memory device and methods of forming and operating the same, one memory transistor includes sidewall selection gates covering both sidewalls of a floating gate when the floating gate and a control gate are stacked. The sidewall selection gates are in a spacer form. Since the sidewall selection gates are in a spacer form on the sidewall of the floating gate, the degree of integration of cells can be improved. Additionally, since the side wall selection gates are disposed on both sidewalls of the floating gate, a voltage applied from a bit line and a common source line can be controlled and thus conventional writing / erasing errors can be prevented. Therefore, distribution of threshold voltage can be improved.

Owner:SAMSUNG ELECTRONICS CO LTD

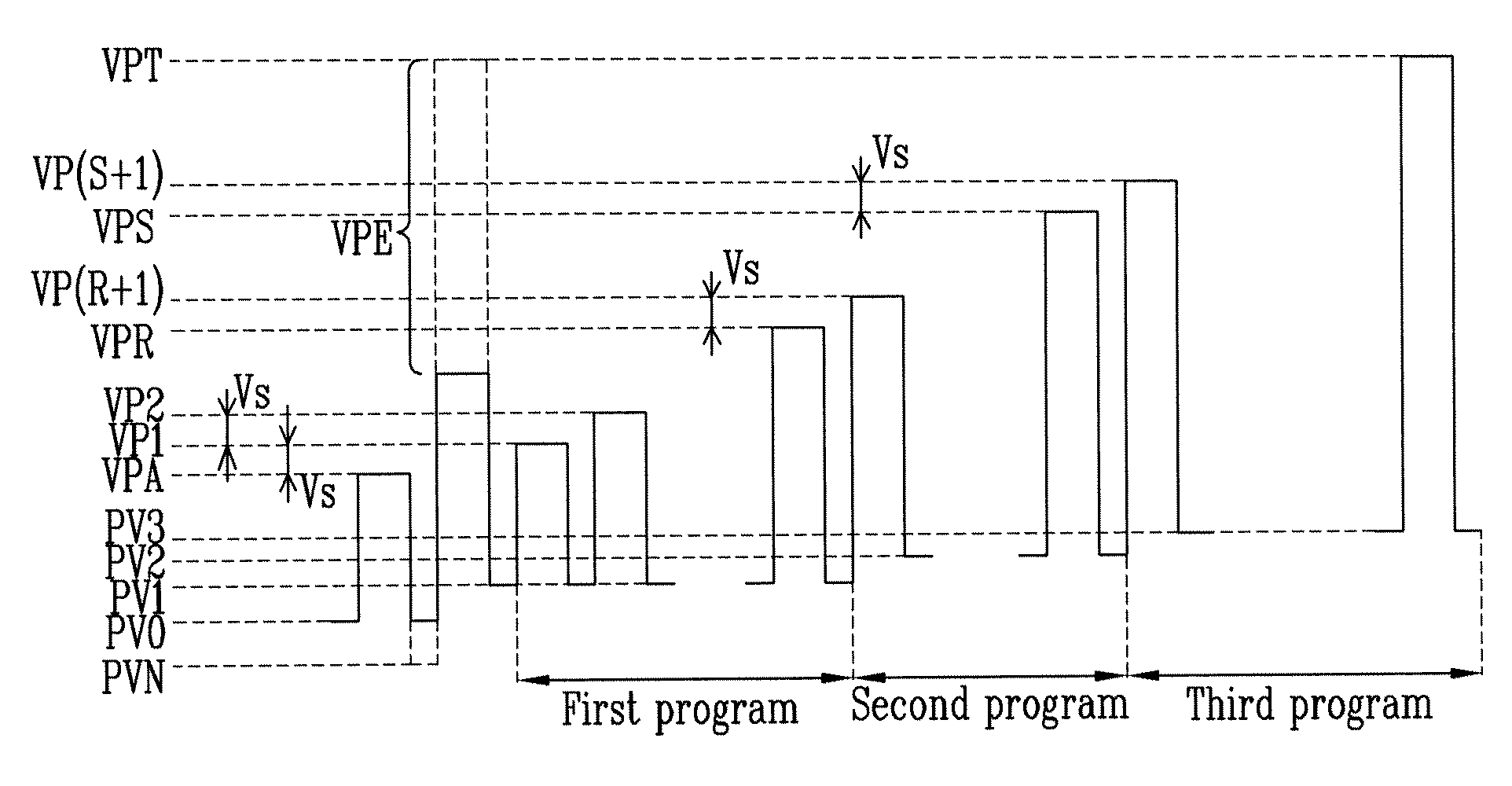

Semiconductor memory device and method of programming multi bit data of the same

ActiveUS10522219B2Improved Threshold Voltage DistributionRaise the threshold voltageRead-only memoriesDigital storageComputer scienceSemiconductor

Owner:SK HYNIX INC

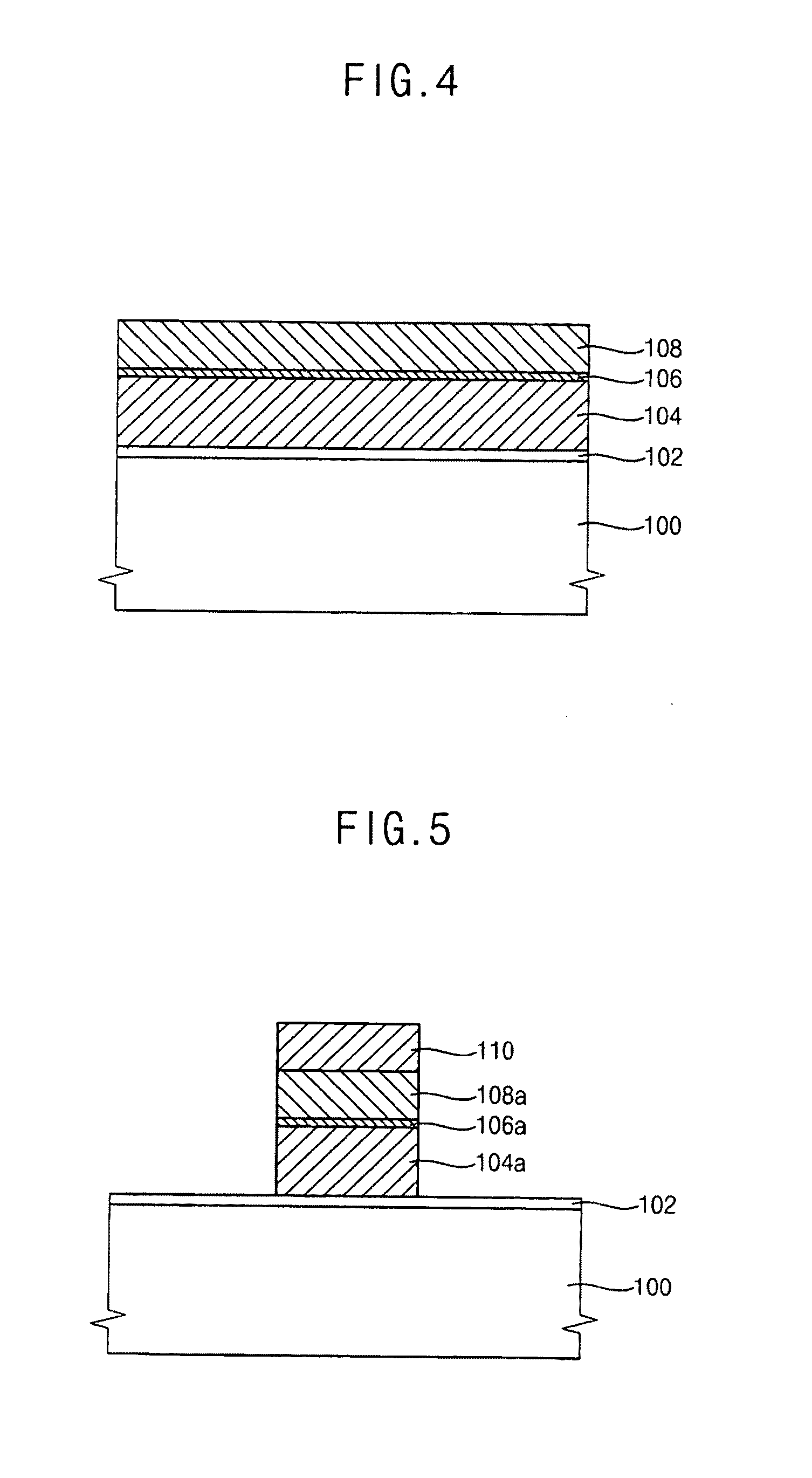

Gate of a transistor and method of forming the same

InactiveUS20110045667A1Improve surface morphologyLower threshold voltageSemiconductor/solid-state device manufacturingSemiconductor devicesGas phaseMetal silicide

A gate of a transistor includes a gate oxide layer formed on a semiconductor device, a first conductive layer pattern including polysilicon doped with boron and formed on the gate oxide layer, a diffusion preventing layer pattern including amorphous silicon formed by a chemical vapor deposition process using a reaction gas having trisilane (Si3H8) and formed on the first conductive layer pattern, and a second conductive layer pattern including metal silicide and formed on the diffusion preventing layer pattern. Since a gate of PMOS transistor includes a diffusion preventing layer having an excellent surface morphology, diffusion of impurities is sufficiently prevented. Thus, the threshold voltage of PMOS transistor may be reduced and threshold voltage distribution may be improved.

Owner:KIM JIN GYUN +2