Semiconductor device and manufacturing method thereof

a technology of semiconductor devices and manufacturing methods, applied in semiconductor devices, capacitors, electrical devices, etc., can solve problems such as difficulty in adjusting etching conditions, and achieve the effect of preventing local damage to ferroelectric films and reducing leakage currents

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

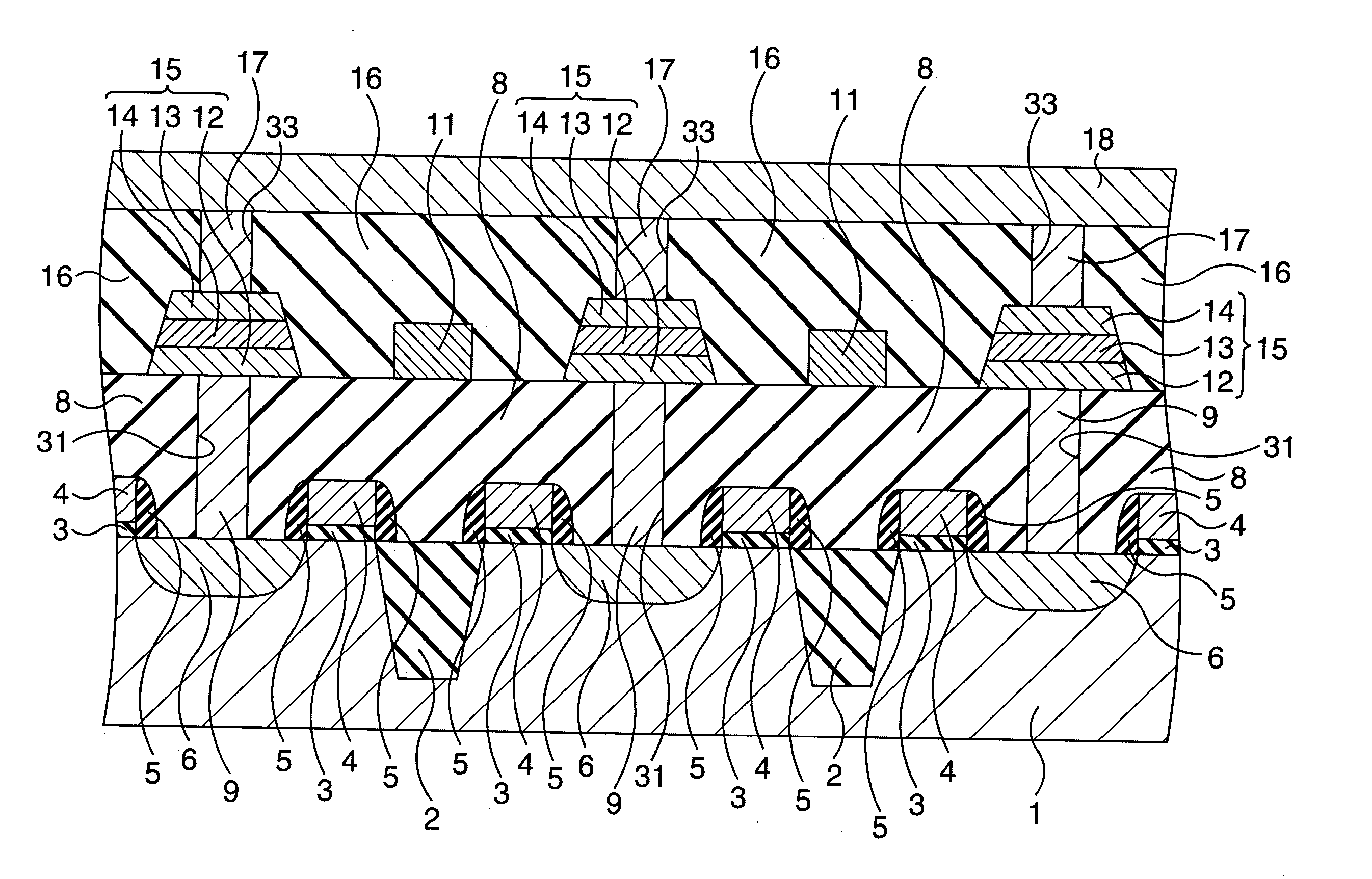

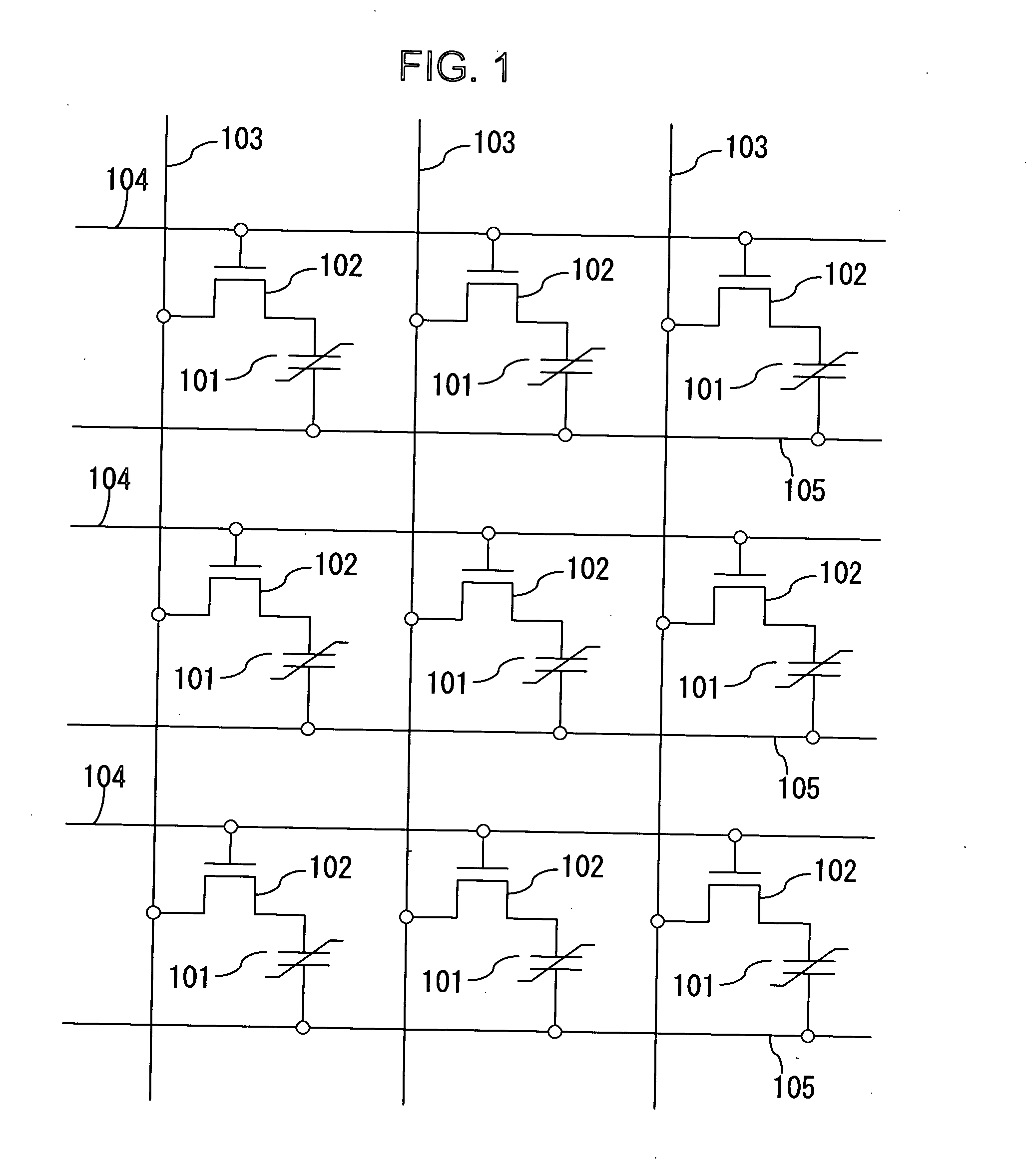

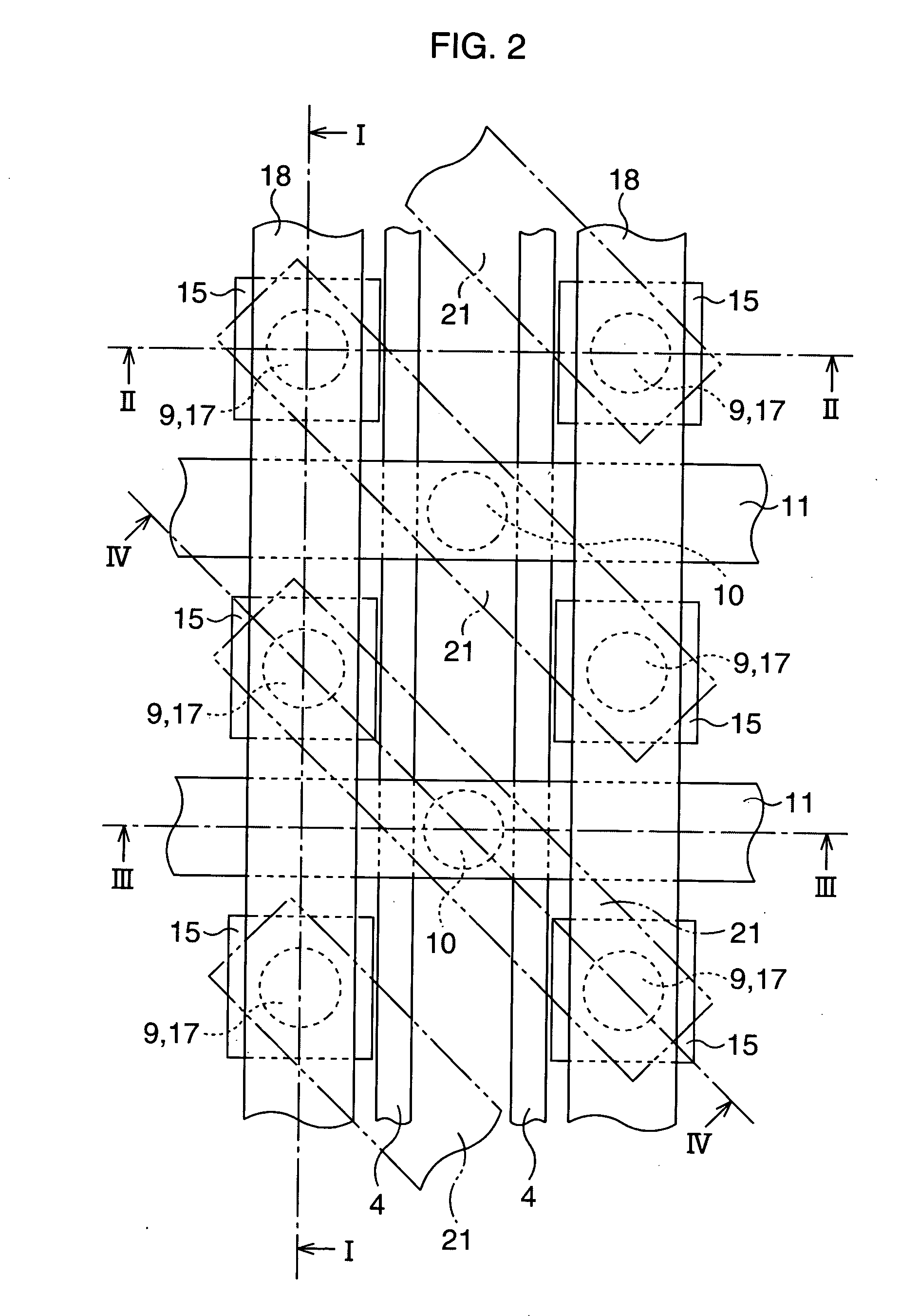

[0035] Hereinbelow, a first embodiment of the present invention will be described. FIG. 2 is a layout illustrating a configuration of a semiconductor device (ferroelectric memory) according to the first embodiment of the present invention. FIG. 3 is a sectional view taken along the I-I line in FIG. 2. FIG. 4A is a sectional view taken along the II-II line in FIG. 2. FIG. 4B is a sectional view taken along the III-III line in FIG. 2. FIG. 5 is a sectional view taken along the IV-IV line in FIG. 2.

[0036] In the present embodiment, as shown in FIG. 2 to FIG. 5, element isolation insulating films 2 for isolating a plurality of element regions 21 extending in one direction are formed for example by STI (Shallow Trench Isolation) method on the surface of a semiconductor substrate 1 such as a silicon substrate or the like. In addition, gate electrodes 4 (word lines) inclining at an angle of 45 degrees to the extending direction of the element regions 21 are formed via gate insulating film...

second embodiment

[0044] Subsequently, a second embodiment of the present invention will be described. FIG. 6 is a layout illustrating a configuration of a semiconductor device (ferroelectric memory) according to the second embodiment of the present invention. FIG. 7 is a sectional view taken along the I-I line in FIG. 6.

[0045] In the present embodiment, differently from the first embodiment, an element region 21 has a dogleg planar shape and the extending direction of a gate electrode 4 (word line) is parallel to a bit line 11 and orthogonal to a plate line 18. Two impurity diffused layers 6 provided in the same element region 21 are connected to lower electrodes 12 of ferroelectric capacitors 15 of which upper electrodes 14 are connected to the same plate line 18.

[0046] Also, in this second embodiment configured as described above, the same effects as of the first embodiment can be obtained.

third embodiment

[0047] Subsequently, a third embodiment of the present invention will be described. FIG. 8 is a layout illustrating a configuration of a semiconductor device (ferroelectric memory) according to the third embodiment of the present invention. In the present embodiment, a ferroelectric capacitor 15 has a circular planar shape in comparison with that of the prior layout shown in FIG. 10 to FIG. 12.

[0048] In the third embodiment as described above, in the manufacturing process thereof, deposits generally become difficult to adhere to the sidewall 5 of the ferroelectric capacitor 15 at the time of the high-temperature simultaneous etching, enabling to reduce leakage current. Whereas, the sidewall deposits have an advantage of preventing a capacitor insulating film 13 from damages as mentioned before. Preferably, therefore, in the high-temperature simultaneous etching, etching conditions are adjusted so that the damages of the capacitor insulating film 13 are prevented. At the time of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More