Efficient model order reduction via multi-point moment matching

a multi-point moment matching and efficient model technology, applied in the field of microelectronic circuit and system design, can solve the problems of inability to adapt smm to parallel, inability to achieve parallel processing, and inability to achieve numerical stability of q order approximation, so as to reduce truncation errors and ensure numerical stability of approximation. , the effect of numerical stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

General Description

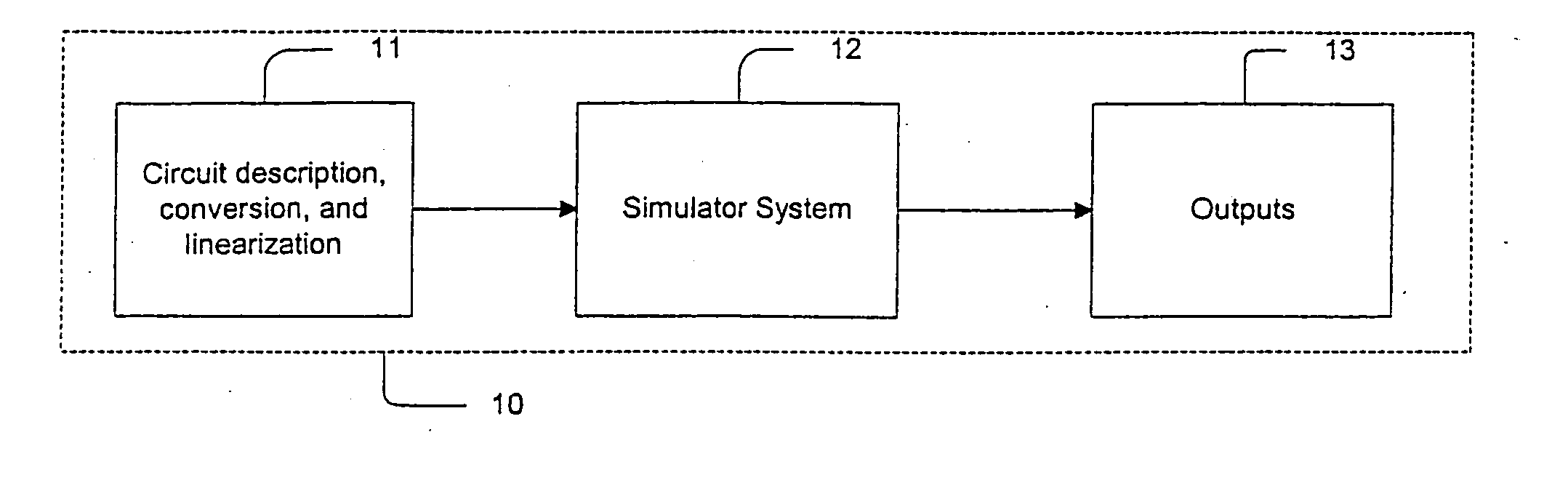

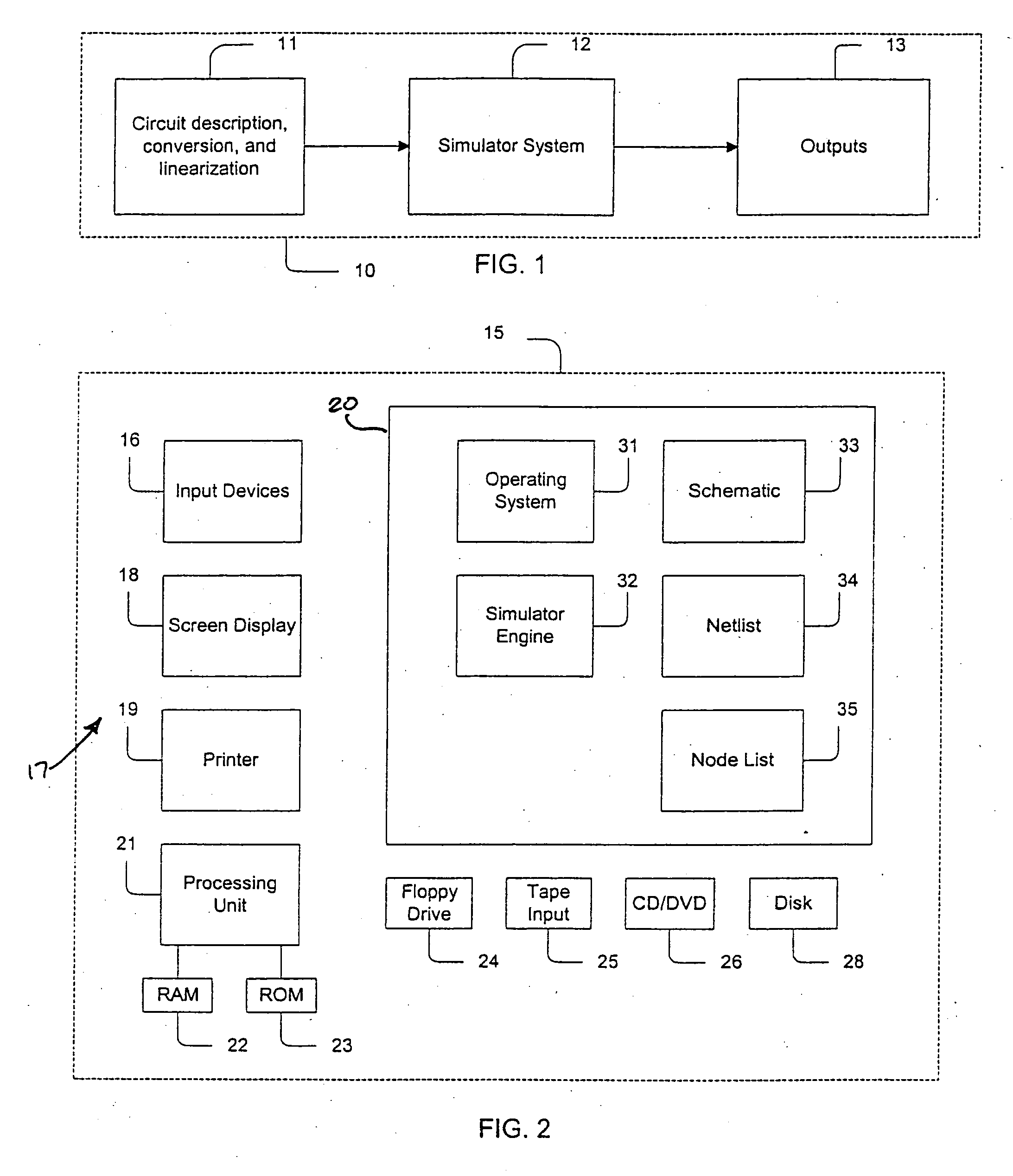

[0068] Referring to the drawings, FIG. 1 is a simplified representation of a circuit simulating system 10 for use in the design and simulation of integrated circuits and / or systems. The circuit simulating system 10 includes a circuit design system 11 and a simulator system 12 which provides outputs, represented by block 13, such as speed of the circuit or system being simulated, power consumption by the circuit or system being simulated, coupling noise, signal skew, for example. The operation of the simulator system 12 is based on model order reduction techniques. In one embodiment, the simulator system 12 is an interconnect evaluator, hereinafter interconnect evaluator 12, which incorporates the multi-point moment matching (MMM) technique / apparatus provided by the present invention. The interconnect evaluator 12 provides verification of the design and operation of circuits or systems being simulated. The interconnect evaluator 12 can be configured to perform DC...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More