Low CTE substrates for use with low-k flip-chip package devices

a technology of flip-chip package device and substrate, which is applied in the direction of printed circuit manufacturing, printed circuit stress/warp reduction, printed circuit aspects, etc., can solve the problems of increasing negative impact on circuit performance, difficult and unique technical problems, and cost yield reduction, so as to reduce the cte mismatch, increase the coplanarity of the package substrate and the chip, and reduce the lead content

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

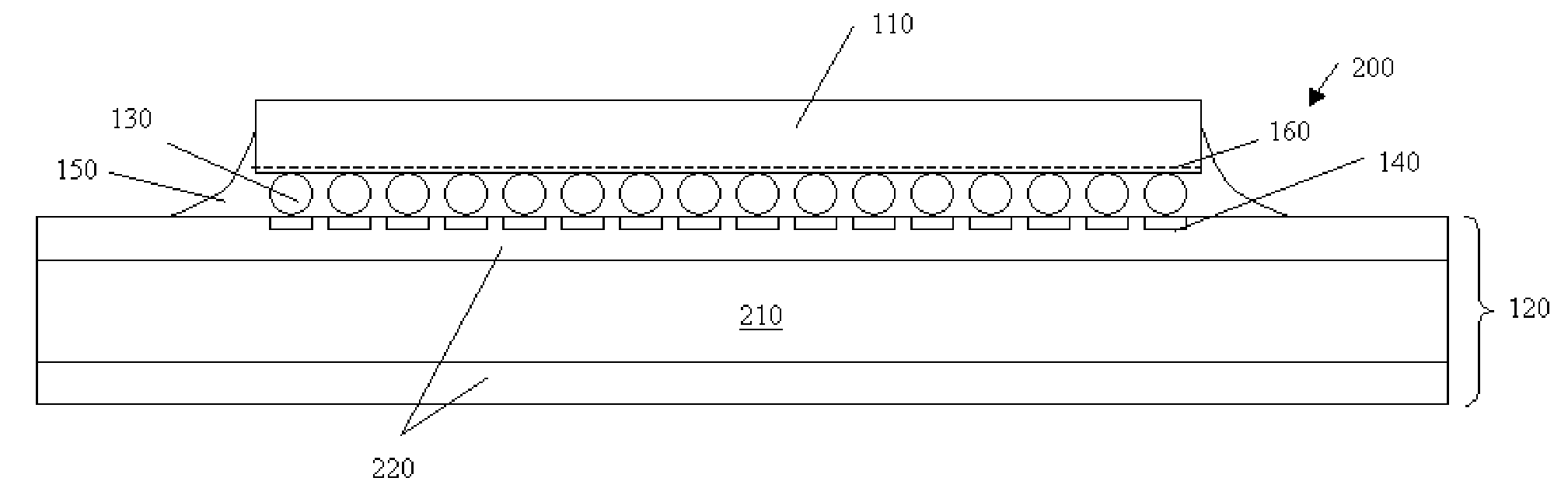

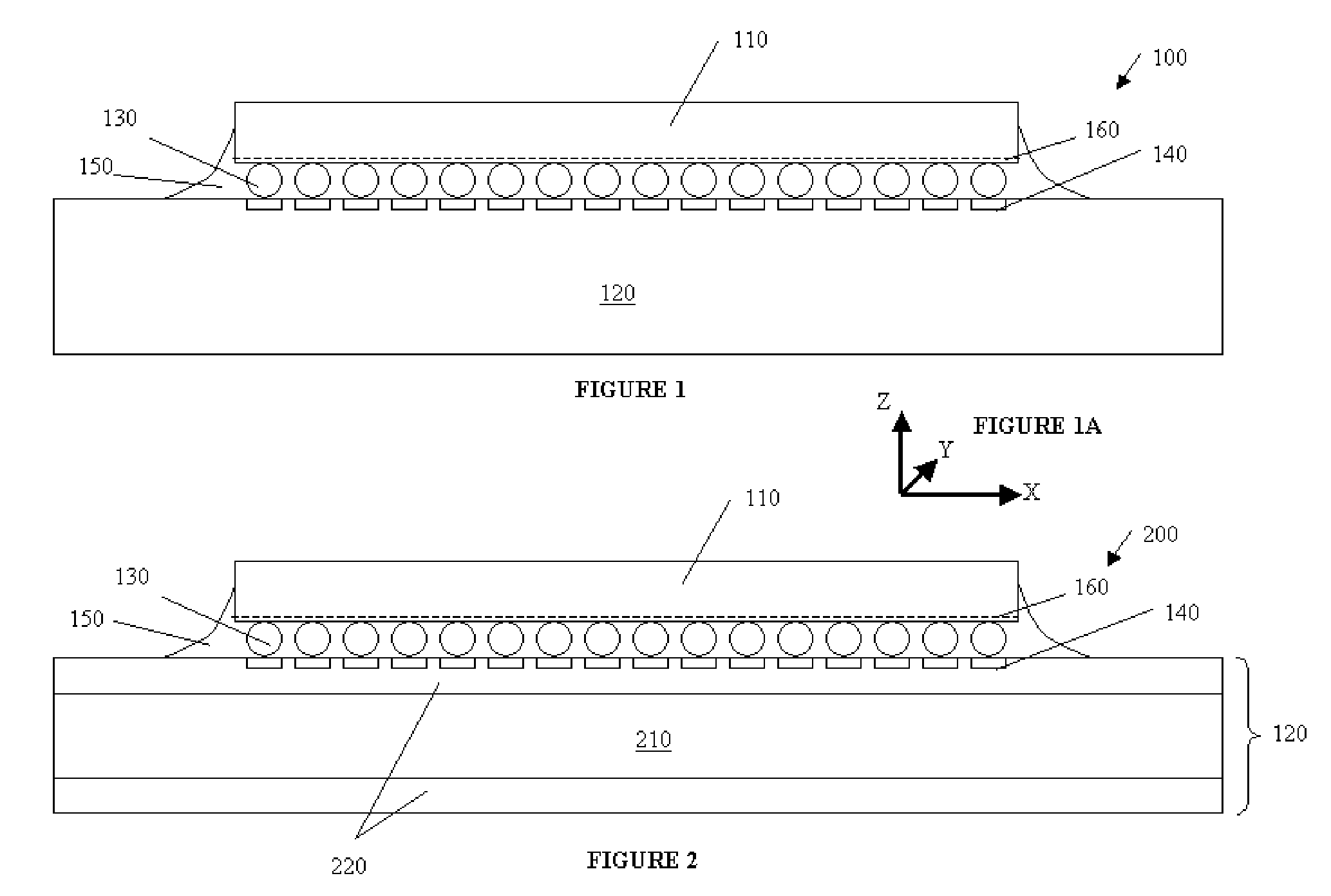

[0014] Turning initially to FIG. 1, illustrated is one embodiment of a semiconductor package device 100 constructed according to the disclosed principles. Specifically, the package device 100 includes an integrated circuit (IC) chip 110 that contains numerous active and inactive components to form one or more functional integrated circuits. In addition, the IC chip 110 is configured for mounting onto another substrate 120 using a flip-chip technique. As such, solder bumps (or other appropriate coupling components) 130 are formed on the bottom or mounting surface of the IC chip 110 in a BGA.

[0015] In the illustrated embodiment, the substrate 120 on which the IC chip 110 is mounted is a package substrate 120. More specifically, the package substrate 120 includes bonding pads (one of which is labeled 140) formed on an exterior mounting surface that faces the IC chip 110, and which are configured to receive the solder bumps 130 from the IC chip during the flip-chip mounting. Finally, a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More