Optical Interconnection Arrangement For High Speed, High Density Communication Systems

a communication system and high-speed technology, applied in the field of optical interconnection arrangement, can solve the problems of consuming a significant amount of power, interconnecting computer servers or network nodes that cannot keep up with the growth of computing power,

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0021]As mentioned above, today's data centers rely on thousands of computing nodes, coupled together with high speed interconnects, to achieve the performance metrics of today's applications. Each computing node consists of an IC (chip) processor core that is used to perform various functions. The processing power of each node is continuing to sharply increase. However, the need to interconnect the nodes at high speed, low power and even lower latency is outpacing the available technologies of today.

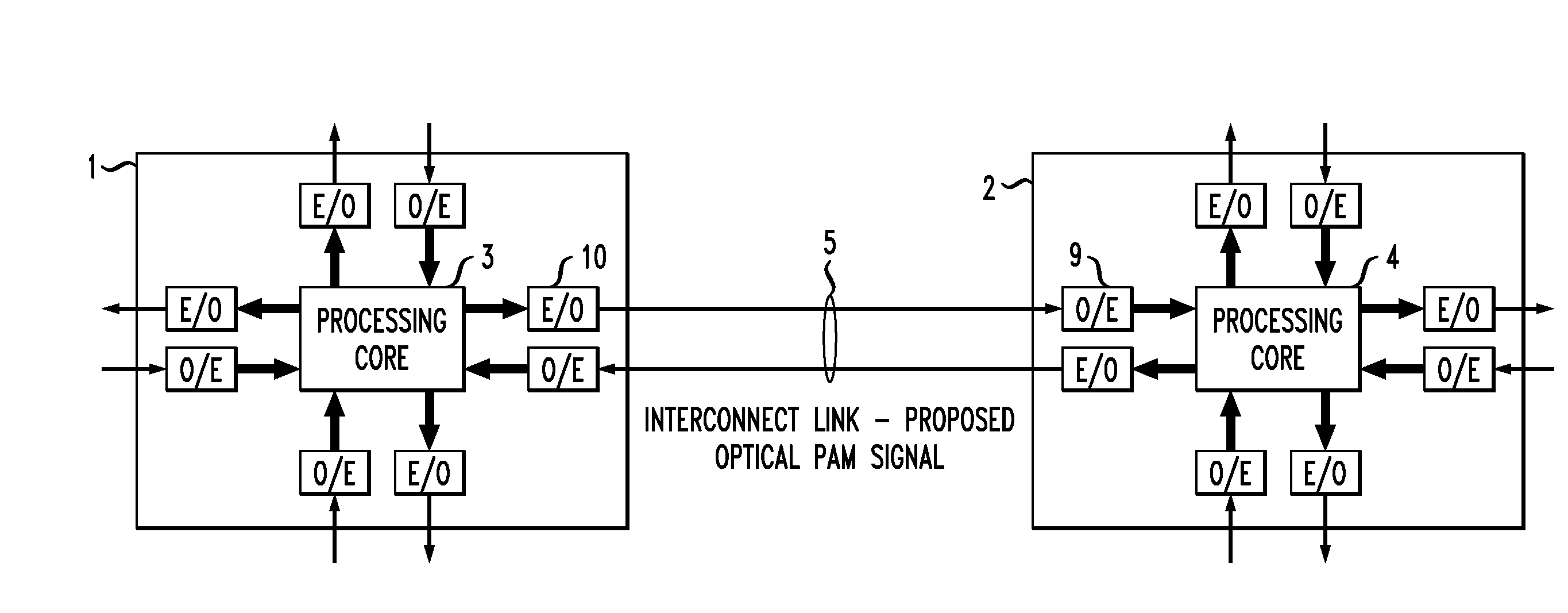

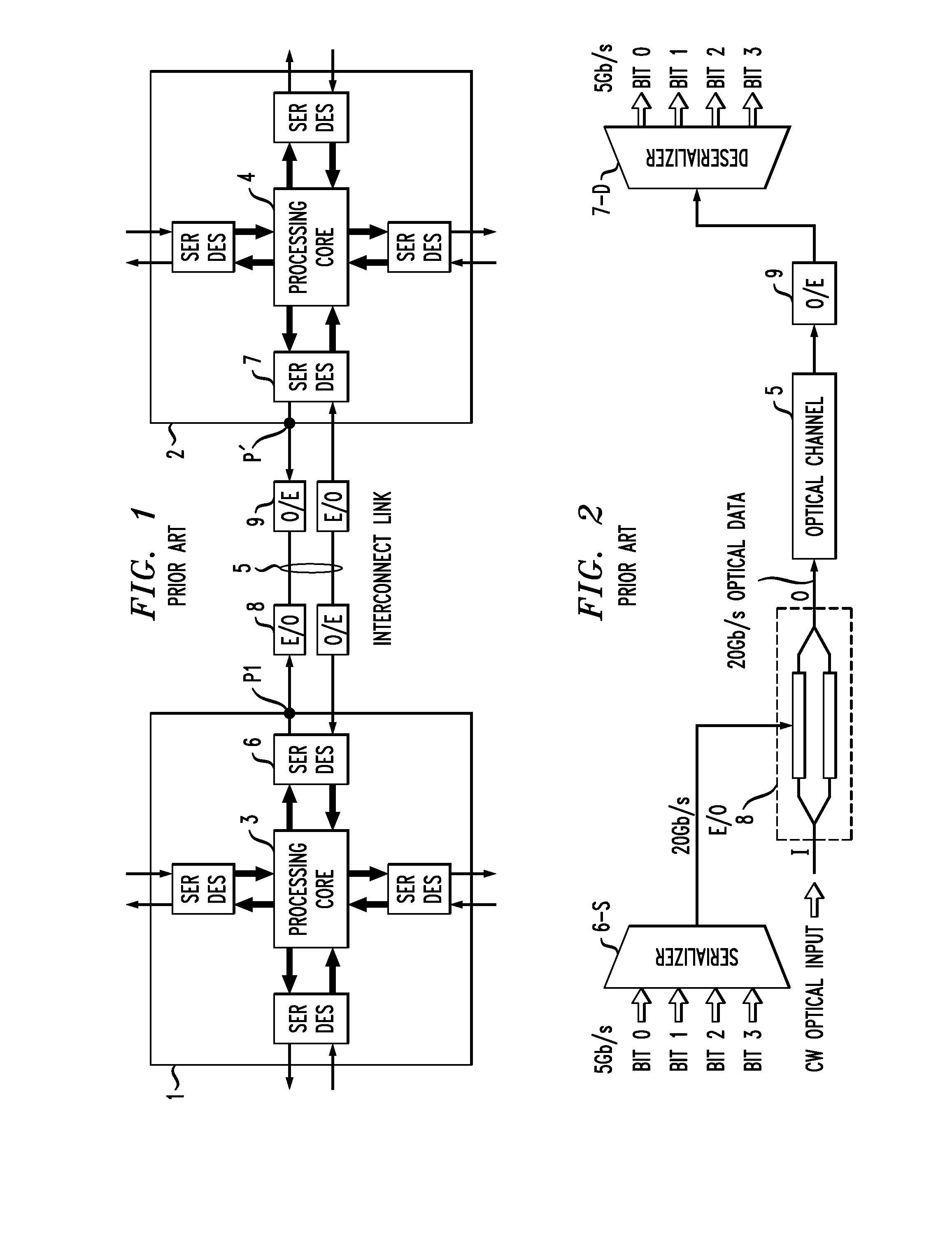

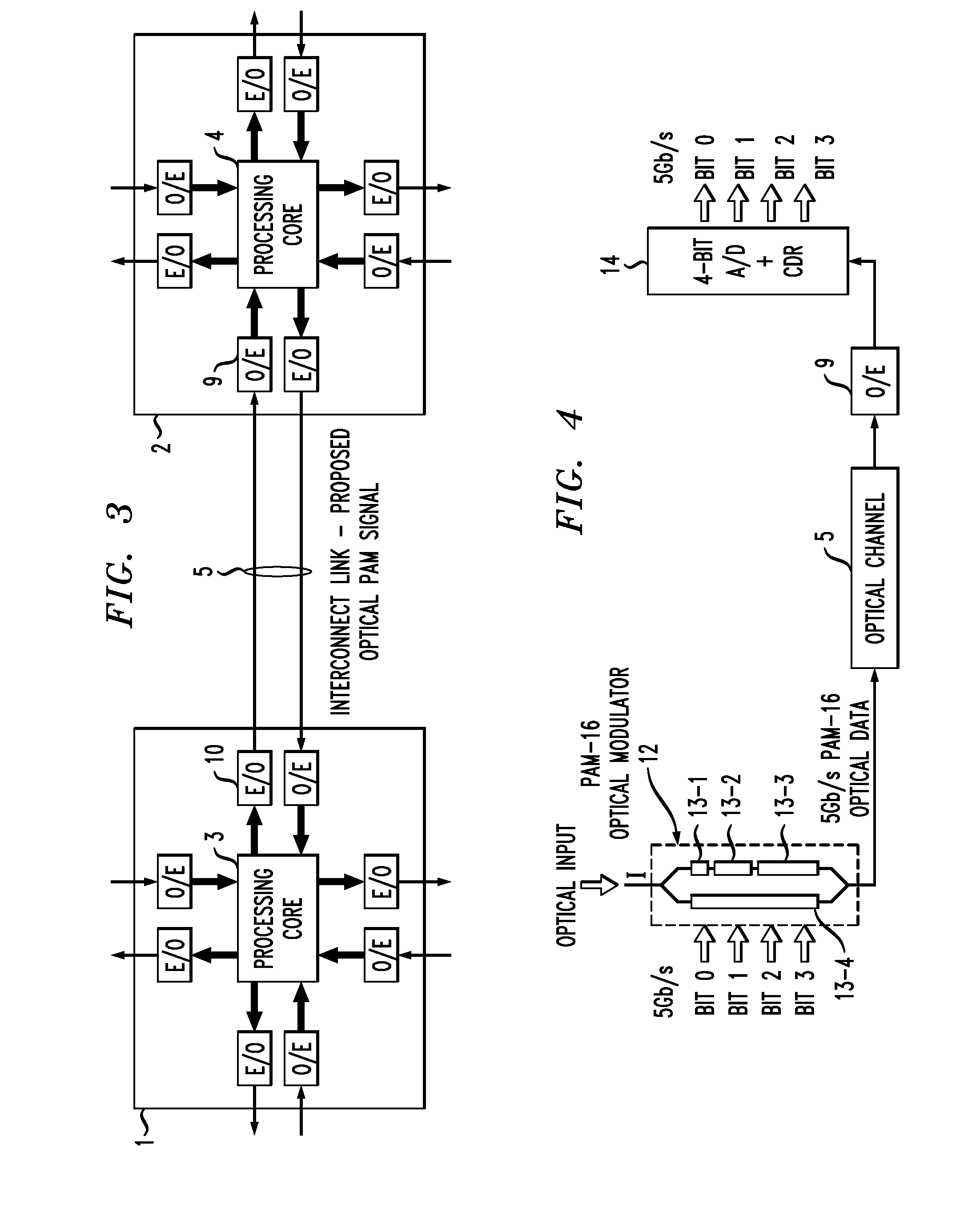

[0022]FIG. 1 illustrates a conventional prior art optical interconnect arrangement between a first chip 1 and a second chip 2. Chip 1 includes a processing core 3 that functions to manipulate massive amounts of data in a parallel word format. A similar processing core 4 is included within chip 2, and there is a need to provide communication between chips 1 and 2 via an optical interconnect link 5. It is to be understood that only a single link 5 is shown for the purposes of clarity. In ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More